Conteúdos das Aulas

Bibliografia

Material para Download

Avaliaçăo

Programa da Disciplina

Semestre 2020/1

Professor

Responsável:

Ney Laert Vilar Calazans

Turma: 490

Sala: 318 ou 304, Prédio 32

Horário: 5AB (das 8:00 ŕs 9:40)

Curso: Engenharia da Computaçăo

ESCOLA

POLITÉCNICA - PUCRS

Índice desta página

Conteúdos das Aulas

Bibliografia

Material para Download

Avaliaçăo

Programa da Disciplina

Avisos Importantes

Regras do Jogo para o Semestre

Plano de Atividades para o Semestre

Aula |

Data |

CONTEÚDO |

Data Máxima para Entrega do Trabalho |

| 1 | 05/03 |

Aula Inaugural - plano da disciplina, contextualizaçăo no curso, avaliaçăo, etc. MATERIAL PARA ESTUDO DA LINGUAGEM VHDL:

Prática de Aula - Enunciado do trabalho T1 (10% da nota de G1) |

|

| 2 | 12/03 |

Prática de Aula - Enunciado do trabalho T1 (10% da nota de G1) Introduçăo ŕ Simulaçăo de Circuitos em VHDL

|

|

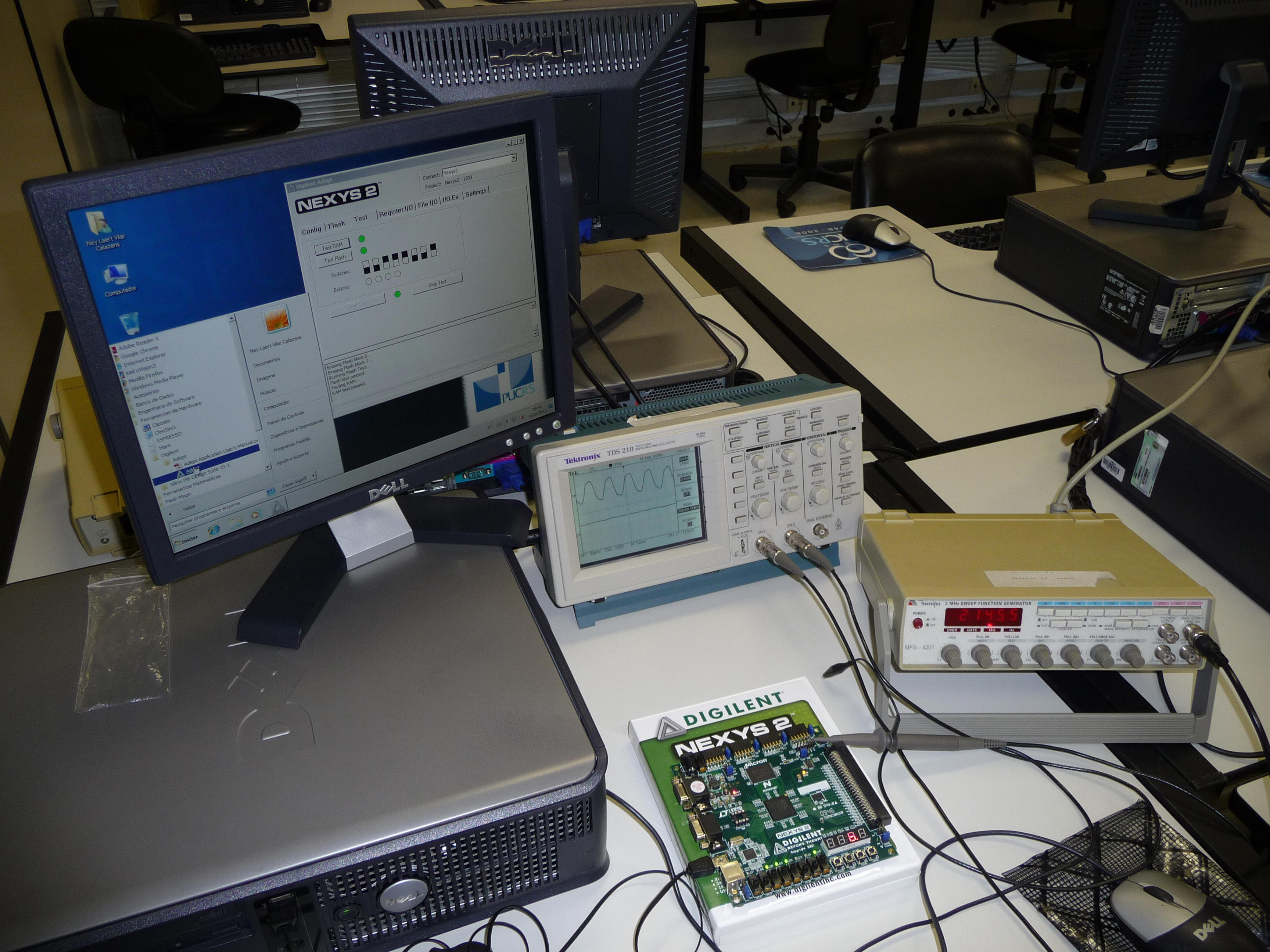

| 3 | 19/03 | Prática de Aula - Enunciado do trabalho T2 (10% da nota de G1) Introduçăo a Prototipaçăo de Hardware com FPGAs

Uso dos recursos da plataforma Nexys2 |

T1 |

| 4 | 26/03 |

Prática de Aula - Enunciado do trabalho T2 (10% da nota de G1) (Continuaçăo) Introduçăo a Prototipaçăo de Hardware com FPGAs - Continuaçăo

|

|

| 5 | 02/04 |

Prática de Aula - Enunciado do trabalho T3 (10% da nota de G1) VHDL: Processos, Paralelismo e o Comando process |

|

| 09/04 | Feriado - Páscoa | ||

| 6 | 16/04 |

Prática de Aula - Enunciado do trabalho T3 (10% da nota de G1) (Continuaçăo) VHDL: Processos, Paralelismo e o Comando process |

|

| 7 | 23/04 |

Prática de Aula - Enunciado do trabalho T3 (10% da nota de G1) (Conclusăo) VHDL: Processos, Paralelismo e o Comando process |

T2 |

| 8 | 30/04 |

Prática de Aula

- Enunciado do trabalho T4 (10% da nota de G1) Programaçăo em Linguagem de Montagem do processador MIPS |

|

| 9 | 07/05 |

Prática de Aula

- Enunciado do trabalho T4 (10% da nota de G1)

(Conclusăo) Programaçăo em Linguagem de Montagem do processador MIPS |

T3 |

| 10 | 14/05 |

Prática de Aula

- Enunciado

do trabalho T5 (25% da nota de G1) Projeto de um Circuito com Média Complexidade

Arquivos Auxiliares: dspl_drv_nexys.vhd e debounce.vhd |

|

| 11 | 21/05 |

Prática de Aula

- Enunciado

do trabalho T5 (25% da nota de G1)

(Continuaçăo) Projeto de um Circuito com Média Complexidade

Arquivos Auxiliares |

T4 |

| 12 | 28/05 |

Prática de Aula

- Enunciado

do trabalho T5 (25% da nota de G1) (Continuaçăo) Projeto de um Circuito com Média Complexidade

Arquivos Auxiliares |

|

| 13 | 04/06 |

Enunciado

do trabalho T6 -

Enunciado geral do trabalho T6

(35% da

nota de G1) Simulaçăo e Prototipaçăo de um Processador capaz de Executar Parte do Conjunto de instruçőes da Arquitetura MIPS - o MRstd Arquivos Auxiliares, biblioteca Xilinx Unisim |

T5 |

| 11/06 | Feriado - Corpus Christi | ||

| 14 | 18/06 |

Prática de Aula

- Enunciado

do trabalho T6

(35% da

nota de G1) (Continuaçăo) Simulaçăo e Prototipaçăo de um Processador capaz de Executar Parte do Conjunto de instruçőes da Arquitetura MIPS - o MRstd Arquivos Auxiliares, biblioteca Xilinx Unisim |

|

| 15 | 25/06 |

Prática de Aula

- Enunciado

do trabalho T6

(35% da

nota de G1) (Continuaçăo) Simulaçăo e Prototipaçăo de um Processador capaz de Executar Parte do Conjunto de instruçőes da Arquitetura MIPS - o MRstd Arquivos Auxiliares, biblioteca Xilinx Unisim |

|

| 16 | 02/07 |

Prática de Aula

- Enunciado

do trabalho T6

(35% da

nota de G1) (Continuaçăo) Simulaçăo e Prototipaçăo de um Processador capaz de Executar Parte do Conjunto de instruçőes da Arquitetura MIPS - o MRstd Arquivos Auxiliares, biblioteca Xilinx Unisim |

T6 |

| 09/07 | Prova de G2 |

LIVROS TEXTO

LIVROS REFERENCIADOS

OUTRAS REFERĘNCIAS

SOFTWARE DE APOIO

This page was last updated on April, 22nd, 2020.

If you find problems in this page, please send an e-mail to

ney.calazans at pucrs.br.

We will fix it in the shortest possible delay. Thanks for your help!