# CoCentric<sup>™</sup> SystemC Compiler Behavioral Modeling Guide

Version 2000.11-SCC1, March 2001

Comments? E-mail your comments about Synopsys documentation to doc@synopsys.com

#### **Copyright Notice and Proprietary Information**

Copyright © 2000 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with the p | ermission of | Synopsys,    | Inc., for th | ne exclusive | use of   |

|-----------------------------------------|--------------|--------------|--------------|--------------|----------|

|                                         |              | _ and its er | nployees.    | This is copy | / number |

|                                         |              |              |              |              |          |

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks**

Synopsys, the Synopsys logo, AMPS, Arcadia, CMOS-CBA, COSSAP, Cyclone, DelayMill, DesignPower, DesignSource, DesignWare, dont\_use, EPIC, ExpressModel, Formality, in-Sync, Logic Automation, Logic Modeling, Memory Architect, ModelAccess, ModelTools, PathBlazer, PathMill, PowerArc, PowerMill, PrimeTime, RailMill, Silicon Architects, SmartLicense, SmartModel, SmartModels, SNUG, SOLV-IT!, SolvNET, Stream Driven Simulator, Synopsys Eagle Design Automation, Synopsys Eagle*i*, Synthetic Designs, TestBench Manager, and TimeMill are registered trademarks of Synopsys, Inc.

#### Trademarks

ACE, BCView, Behavioral Compiler, BOA, BRT, CBA, CBAII, CBA Design System, CBA-Frame, Cedar, CoCentric, DAVIS, DC Expert, DC Expert *Plus*, DC Professional, DC Ultra, DC Ultra Plus, Design Advisor, Design Analyzer, Design Compiler, DesignTime, Direct RTL, Direct Silicon Access, dont\_touch, dont\_touch\_network, DW8051, DWPCI, ECL Compiler, ECO Compiler, Floorplan Manager, FoundryModel, FPGA Compiler, FPGA Compiler II, FPGA *Express*, Frame Compiler, General Purpose Post-Processor, GPP, HDL Advisor, HDL Compiler, Integrator, Interactive Waveform Viewer, Liberty, Library Compiler, Logic Model, MAX, ModelSource, Module Compiler, MS-3200, MS-3400, Nanometer Design Experts, Nanometer IC Design, Nanometer Ready, Odyssey, PowerCODE, PowerGate, Power Compiler, ProFPGA, ProMA, Protocol Compiler, RMM, RoadRunner, RTL Analyzer, Schematic Compiler, Scirocco, Shadow Debugger, SmartModel Library, Source-Level Design, SWIFT, Synopsys EagleV, Test Compiler, Test Compiler Plus, Test Manager, TestGen, TestSim, TetraMAX, TimeTracker, Timing Annotator, Trace-On-Demand, VCS, VCS Express, VCSi, VERA, VHDL Compiler, VHDL System Simulator, Visualyze, VMC, and VSS are trademarks of Synopsys, Inc.

#### **Service Marks**

TAP-in is a service mark of Synopsys, Inc.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A.

Document Order Number: 37581-000 JB CoCentric™ SystemC Compiler Behavioral Modeling Guide, v2000.11-SCC1

# Contents

#### Preface

|    | What's New in This Release                      | xxiv |

|----|-------------------------------------------------|------|

|    | About This Guide                                | xxvi |

|    | Customer Support                                | xxx  |

| 1. | Introduction                                    |      |

|    | Defining Levels of Abstraction in System Design | 1-3  |

|    | Architectural Level                             | 1-4  |

|    | Untimed Functional Model                        | 1-5  |

|    | Timed Functional Model                          | 1-5  |

|    | Functional Coding Style                         | 1-5  |

|    | Behavioral Model                                | 1-9  |

|    | Behavioral Coding Style                         | 1-10 |

|    | Refining From Functional to Behavioral Model    | 1-10 |

|    | Register Transfer Level Model                   | 1-14 |

|    | RTL Coding Style                                | 1-15 |

|    | Refining into RTL                               | 1-15 |

|    | Choosing the Right Abstraction for Synthesis    | 1-19 |

|    | Identifying Attributes Suitable for Behavioral Synthesis | 1-19 |

|----|----------------------------------------------------------|------|

|    | Identifying Attributes Suitable for RTL Synthesis        | 1-21 |

|    | Comparison of Behavioral and RTL Synthesis               | 1-22 |

| 2. | Refining for Behavioral Synthesis                        |      |

|    | Refinement Overview                                      | 2-3  |

|    | Creating and Refining the Structure From a C/C++ Model   | 2-6  |

|    | Define I/O Ports                                         | 2-6  |

|    | Specify Internal Structure                               | 2-6  |

|    | Specify the Internal Communication                       | 2-7  |

|    | Specify the Detailed Architecture                        | 2-8  |

|    | Atomic and Hierarchical Blocks                           | 2-9  |

|    | Modules                                                  | 2-12 |

|    | Module Header File                                       | 2-13 |

|    | Module Ports                                             | 2-14 |

|    | Internal Signals                                         | 2-16 |

|    | Reading and Writing Ports                                | 2-17 |

|    | Internal Data Variables                                  | 2-18 |

|    | Processes                                                | 2-20 |

|    | Types of Processes                                       | 2-21 |

|    | Creating a Process in a Module                           | 2-22 |

|    | Member Functions                                         | 2-23 |

|    | Module Constructor                                       | 2-24 |

|    | Module Implementation File                               | 2-26 |

|    | Using an Infinite Loop                                   | 2-26 |

|    | Refining the Structure From a High-Level SystemC Model   | 2-28 |

|    | Creating and Refining Processes                   | 2-28 |

|----|---------------------------------------------------|------|

|    | Converting to a Synthesizable Subset              |      |

|    | Excluding Simulation-Specific Code                | 2-31 |

|    | SystemC and C++ Synthesizable Subset              | 2-32 |

|    | Nonsynthesizable Subset of SystemC                | 2-33 |

|    | Nonsynthesizable C/C++ Constructs                 | 2-34 |

|    | Refining Data                                     | 2-37 |

|    | Synthesizable Data Types                          | 2-37 |

|    | Nonsynthesizable Data Types                       | 2-38 |

|    | Recommended Types for Synthesis.                  | 2-39 |

|    | Using SystemC Types                               | 2-41 |

|    | Bit and Bit Vector Data Type Operators            | 2-41 |

|    | Fixed and Arbitrary Precision Data Type Operators | 2-42 |

|    | Using Enumerated Types                            | 2-43 |

|    | Using Aggregate Data Types                        | 2-43 |

|    | Using C++ Types                                   | 2-43 |

|    | Recommendations About Data Types                  | 2-46 |

|    | Refining Control.                                 | 2-47 |

|    | Advanced Refinement Techniques                    | 2-48 |

|    | Refinement Recommendations                        | 2-49 |

| 3. | Behavioral Coding Guidelines                      |      |

|    | Using Clocked Thread Processes                    | 3-2  |

|    | Characteristics of the Clocked Thread Process     | 3-2  |

|    | Using the wait Statement                          | 3-3  |

|    | Using the wait_until Statement.                   | 3-3  |

|    |                                                   |      |

| Controlling a Clocked Thread Process        | 3-4  |

|---------------------------------------------|------|

| Simple Clocked Thread Example               | 3-4  |

| Using Inputs and Outputs                    | 3-6  |

| Registered Outputs                          | 3-6  |

| Inputs and Outputs Within Cycles            | 3-6  |

| Specifying I/O Read and Write               | 3-7  |

| Specifying I/O Cycles                       | 3-7  |

| I/O Scheduling Modes                        | 3-8  |

| Cycle-Fixed Scheduling Mode                 | 3-8  |

| Superstate-Fixed Schedule Mode              | 3-8  |

| Comparing I/O Scheduling Modes              | 3-9  |

| Behavioral Coding Style Rules               | 3-10 |

| Definition of Coding Rule Terms             | 3-10 |

| General Coding Rules                        | 3-11 |

| Cycle-Fixed Mode Coding Rules               | 3-12 |

| Superstate-Fixed Mode Coding Rules          | 3-12 |

| General Coding Rules Examples               | 3-13 |

| General Coding Rule 1                       | 3-13 |

| General Coding Rule 2                       | 3-14 |

| General Coding Rule 3                       | 3-15 |

| General Coding Rule 4                       | 3-16 |

| General Coding Rule 5                       | 3-20 |

| Cycle-Fixed Mode Coding Rules Examples.     | 3-23 |

| Cycle-Fixed Coding Rule 1                   | 3-23 |

| Cycle-Fixed Coding Rule 2                   | 3-26 |

| Cycle-Fixed Coding Rule 3                   | 3-28 |

| Superstate-Fixed Mode Coding Rules Examples | 3-29 |

| Superstate-Fixed Coding Rule 1Superstate-Fixed Coding Rule 2 | 3-29<br>3-30 |

|--------------------------------------------------------------|--------------|

| Finding the Cause of Timing-Dependent Coding Errors          | 3-31         |

| Using Conditional Statements                                 | 3-32         |

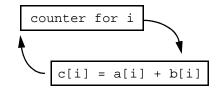

| Using Loops                                                  | 3-33         |

| Understanding How Loops Are Scheduled                        | 3-33         |

| Labeling a Loop                                              | 3-34         |

| Using while Loops                                            | 3-35         |

| Using an Infinite while Loop                                 | 3-35         |

| Using dowhile Loops                                          | 3-36         |

| Using for Loops                                              | 3-36         |

| Rolled Versus Unrolled Loops                                 | 3-36         |

| Rolled for Loops                                             | 3-37         |

| Unrolling for Loops                                          | 3-37         |

| Comparing Rolled and Unrolled Loops                          | 3-39         |

| Selectively Unrolling Loop Iterations                        | 3-40         |

| Ensuring a Statically Determinable Exit Condition            | 3-41         |

|                                                              | 3-42         |

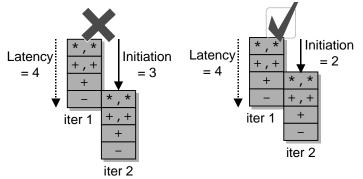

| Pipelining Loop Rules                                        | 3-45         |

| Using Resets                                                 | 3-46         |

| Describing a Global Reset                                    | 3-46         |

| Specifying the Reset Behavior                                | 3-46         |

| Specifying a Reset Implementation                            | 3-48         |

| Using Variables and Signals                                  | 3-49         |

| Initializing Variables                                       | 3-49         |

| Using Signals and Wait Statements                            | 3-50         |

|    | Using Variables and Wait Statements                | 3-52 |

|----|----------------------------------------------------|------|

|    | Using Variables for Register Allocation Efficiency | 3-53 |

|    | Determining the Lifetime of Variables              | 3-54 |

| 4. | Using Functions and DesignWare Components          |      |

|    | Using Member Functions                             | 4-2  |

|    | Using Nonmember Functions                          | 4-4  |

|    | Using Preserved Functions                          | 4-4  |

|    | When to Preserve Functions                         | 4-5  |

|    | Preserved Function Restrictions                    | 4-5  |

|    | Creating Preserved Functions                       | 4-6  |

|    | Nonmember Preserved Functions                      | 4-9  |

|    | Using Reference Parameters in Preserved Functions  | 4-10 |

|    | Using DesignWare Components                        | 4-11 |

|    | Using map_to_operator                              | 4-11 |

|    | Guidelines for Using map_to_operator               | 4-12 |

| 5. | Using Arrays, Register Files, and Memories         |      |

|    | Using Arrays                                       | 5-2  |

|    | Declaring Arrays                                   | 5-2  |

|    | Reading From and Writing to Variable Arrays        | 5-3  |

|    | Reading From and Writing to Signal Arrays.         | 5-4  |

|    | Accessing Slices of an Array Location              | 5-5  |

|    | Array Implementations                              | 5-7  |

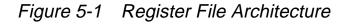

|    | Mapping Arrays to Register Files                   | 5-8  |

|    | Mapping All Arrays to Register Files                       | 5-9<br>5-9 |

|----|------------------------------------------------------------|------------|

|    | Mapping Arrays to Memories                                 |            |

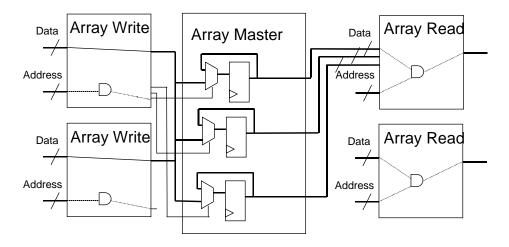

|    | Local Memory          Multiple Arrays Accessing One Memory |            |

|    | Exploring Alternative Memory Types                         |            |

|    | Accessing Register Files and Memories Efficiently          | 5-15       |

|    | Accessing Memory                                           | 5-16       |

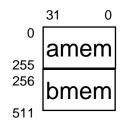

|    | Allowing for Vendor Memory Timing                          | 5-17       |

|    | Eliminating Redundant Memory Accesses                      | 5-18       |

|    | Accessing Bit Slices of Memory Data                        | 5-19       |

| 6. | Using Handshaking in the Circuit and Testbench             |            |

|    | Using Handshake Protocols                                  | 6-3        |

|    | Using One-Way Handshake Protocols                          | 6-4        |

|    | One-Way Handshake Initiated From Behavioral Block          | 6-4        |

|    | One-Way Handshake Initiated From Testbench                 | 6-12       |

|    | Constraining the Width of Handshake Strobes                | 6-19       |

|    | Using Two-Way Handshake Protocols                          | 6-21       |

|    | Two-Way Handshake Initiated From Behavioral Block          | 6-21       |

|    | Two-Way Handshake Initiated From Testbench                 | 6-29       |

|    | Fast Handshaking                                           | 6-36       |

|    | Using ifelse                                               | 6-37       |

|    | Using wait_until                                           | 6-39       |

|    | Using a Pipeline Handshake Protocol                        | 6-40       |

| Appendix A. Compiler Directives        |      |

|----------------------------------------|------|

| Synthesis Compiler Directives          | A-2  |

| line_label                             | A-3  |

| map_to_operator                        | A-3  |

| return_port_name                       | A-4  |

| preserve_function                      | A-4  |

| inout_param                            | A-5  |

| resource                               | A-6  |

| synthesis_off and synthesis_on         | A-7  |

| translate_off and translate_on         | A-7  |

|                                        | A-8  |

| C/C++ Compiler Directives              | A-9  |

| C Line Label                           | A-9  |

| C Conditional Compilation              | A-9  |

| Appendix B. First-In-First-Out Example |      |

| FIFO Description                       | B-2  |

| Architectural Model                    | B-2  |

| Behavioral Model                       | B-6  |

| Ports and Signals                      | B-6  |

| Behavioral Description                 | B-8  |

| Behavioral Testbench                   | B-11 |

| RTL Model                              | 3-15 |

| RTL Description                        | B-16 |

| RTL Testbench                          | B-20 |

| Appendix C. Memory Controller Example      |      |

|--------------------------------------------|------|

| Memory Controller Description              | C-2  |

| Commands                                   | C-2  |

| Ports                                      | C-3  |

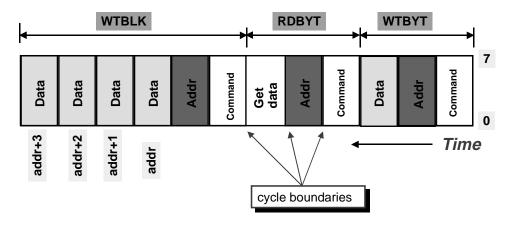

| Communication Protocol                     | C-4  |

| Functional Simulation Model                | C-5  |

| Refined Behavioral Model                   | C-9  |

| Data Types                                 | C-9  |

| Communication Protocol                     | C-9  |

| Clock Placement                            | C-10 |

| Behavioral Model                           | C-10 |

| Appendix D. Fast Fourier Transform Example |      |

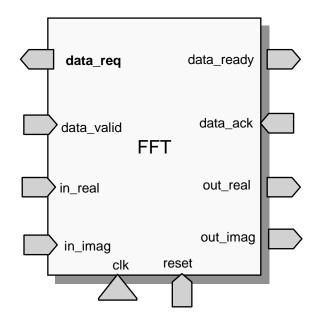

| FFT Description                            | D-2  |

| FFT Computation                            | D-2  |

| Refining From Functional to Behavioral     | D-3  |

| Data Read Two-Way Handshake                | D-3  |

| Data Write Two-Way Handshake               | D-3  |

| FFT Functional Model                       | D-4  |

| FFT Behavioral Model                       | D-9  |

| FFT Testbench                              | D-17 |

| Appendix E. Inverse Quantization Example   |      |

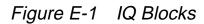

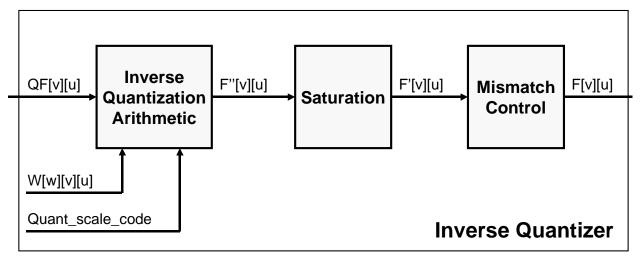

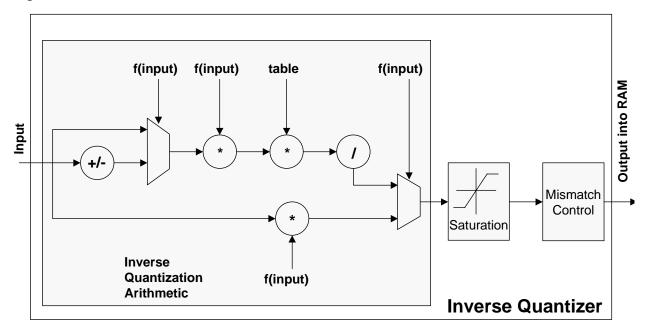

| IQ Description                             | E-2  |

| IQ Data Flow                               | E-3  |

| IQ Block Diagram                       | E-4 |

|----------------------------------------|-----|

| IQ Behavioral Model                    | E-4 |

| Appendix F. Expressions and Operations |     |

| Using Expressions                      | F-2 |

| Operator Precedence                    | F-3 |

| Index                                  |     |

# Figures

| Figure 1-1 | System Design Levels of Abstraction  | 1-3  |

|------------|--------------------------------------|------|

| Figure 1-2 | Architectural Model                  | 1-4  |

| Figure 1-3 | Behavioral Model                     | 1-9  |

| Figure 1-4 | RTL Model                            | 1-14 |

| Figure 2-1 | Refinement Stages and Activities     | 2-4  |

| Figure 2-2 | MPEG Decoder Functional Structure    | 2-7  |

| Figure 2-3 | MPEG Decoder Top-Level Architecture  | 2-8  |

| Figure 2-4 | MPEG Decoder Detailed Architecture   | 2-9  |

| Figure 2-5 | Module                               | 2-12 |

| Figure 2-6 | Module Ports                         | 2-14 |

| Figure 2-7 | Processes and Signals                | 2-16 |

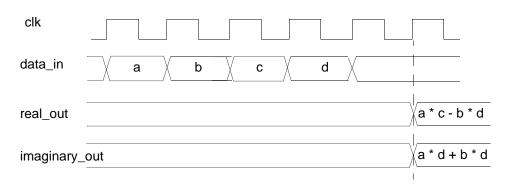

| Figure 3-1 | Simple Multiplier I/O Protocol       | 3-7  |

| Figure 3-2 | Rolled and Unrolled for Loops        | 3-39 |

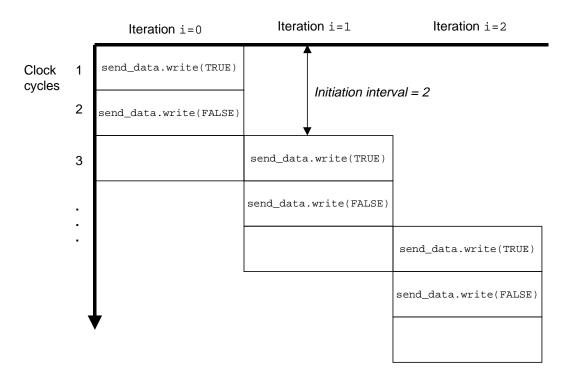

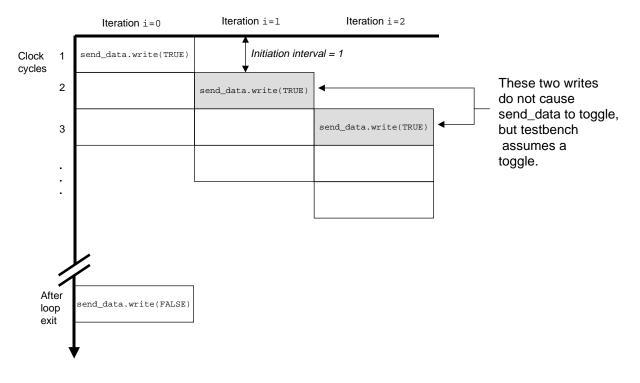

| Figure 3-3 | Loop Latency and Initiation Interval | 3-45 |

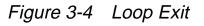

| Figure 3-4 | Loop Exit                            | 3-45 |

| Figure 3-5 | Comparing Signal Use and Data Flow   | 3-51 |

|            |                                      |      |

| Figure 3-6  | Variable Use and Data Flow                     | 3-52 |

|-------------|------------------------------------------------|------|

| Figure 5-1  | Register File Architecture                     | 5-8  |

| Figure 5-2  | Multiple Array Address Space Mapping           | 5-13 |

| Figure 5-3  | Memory Access Time Specification               | 5-17 |

| Figure 5-4  | Bit Slice Accesses                             | 5-20 |

| Figure 6-1  | One-Way Handshake Protocol                     | 6-5  |

| Figure 6-2  | Testbench-Initiated One-Way Handshake          | 6-12 |

| Figure 6-3  | Constraining Input Handshake Signals           | 6-19 |

| Figure 6-4  | Constraining Output Handshake Signals          | 6-20 |

| Figure 6-5  | Two-Way Handshake Protocol                     | 6-22 |

| Figure 6-6  | Two-Way Handshake Protocol                     | 6-29 |

| Figure 6-7  | Timing Diagram of while Loop                   | 6-37 |

| Figure 6-8  | Timing Diagram Using ifelse                    | 6-38 |

| Figure 6-9  | Timing Diagram Using wait_until                | 6-39 |

| Figure 6-10 | Incorrect Loop Pipeline With Handshake         | 6-41 |

| Figure 6-11 | Correct Loop Pipeline With Extended Initiation |      |

|             | Interval                                       | 6-42 |

| Figure 6-12 | Correct Loop Pipeline Without Handshake Signal |      |

|             | De-assertion                                   | 6-44 |

| Figure C-1  | Behavioral Input Data Flow                     | C-10 |

| Figure D-1  | FFT Ports and Data Types                       | D-2  |

| Figure E-1  | IQ Blocks                                      | E-2  |

| Figure E-2  | IQ Data Flow                                   | E-3  |

| Figure E-3  | IQ Block Diagram                               | E-4  |

# Tables

| Table 2-1 | Nonsynthesizable SystemC Classes               | 2-33 |

|-----------|------------------------------------------------|------|

| Table 2-2 | Nonsynthesizable C/C++ Constructs              | 2-34 |

| Table 2-3 | Synthesizable Data Types                       | 2-39 |

| Table 2-4 | SystemC Bit and Bit Vector Data Type Operators | 2-41 |

| Table 2-5 | SystemC Integer Data Type Operators            | 2-42 |

| Table A-1 | SystemC Compiler Compiler Directives           | A-2  |

| Table F-1 | Operator Precedence                            | F-4  |

# Examples

| Example 1-1  | FIFO Functional Model                         | 1-6  |

|--------------|-----------------------------------------------|------|

| Example 1-2  | FIFO Behavioral Coding                        | 1-12 |

| Example 1-3  | RTL Coding                                    | 1-16 |

| Example 2-1  | Using read() and write() Methods              | 2-18 |

| Example 2-2  | Creating a Clocked Thread Process in a Module | 2-22 |

| Example 2-3  | Module Constructor                            | 2-25 |

| Example 2-4  | Module Behavior                               | 2-27 |

| Example 2-5  | Basic Reset Action and Main Loop              | 2-29 |

| Example 2-6  | Excluding Simulation-Only Code                | 2-31 |

| Example 2-7  | Aggregate Data Type                           | 2-43 |

| Example 2-8  | Implicit Bit Size Restriction                 | 2-44 |

| Example 2-9  | Unknown Variable Bit Size                     | 2-44 |

| Example 2-10 | Incorrectly Using a Data Member as a Variable | 2-45 |

| Example 2-11 | Correct Use of Local Variables                | 2-45 |

| Example 3-1  | Infinite Loops                                | 3-4  |

| Example 3-2  | Simple Clocked Thread Multiplier              | 3-5  |

|              |                                               |      |

| Example 3-3  | Error in Use of General Coding Rule 1                      | 3-13 |

|--------------|------------------------------------------------------------|------|

| Example 3-4  | Correct General Coding Rule 1                              | 3-13 |

| Example 3-5  | Error in Use of General Coding Rule 2                      | 3-14 |

| Example 3-6  | Correct General Coding Rule 2                              | 3-14 |

| Example 3-7  | Error in Use of General Coding Rule 3                      | 3-15 |

| Example 3-8  | Correct General Coding Rule 3                              | 3-15 |

| Example 3-9  | Error in Use of General Coding Rule 4, If                  |      |

|              | Conditional                                                | 3-17 |

| Example 3-10 | Correct General Coding Rule 4, If Conditional              | 3-17 |

| Example 3-11 | Error in Use of General Coding Rule 4, If                  |      |

|              | Conditional With Implied Else                              | 3-18 |

| Example 3-12 | Correct General Coding Rule 4, If Conditional              | 3-18 |

| Example 3-13 | Error in Use of General Coding Rule 4, Switch              |      |

|              | Conditional                                                | 3-19 |

| Example 3-14 | Correct General Coding Rule 4, Switch Conditional          | 3-19 |

| Example 3-15 | Error in Use of General Coding Rule 5                      | 3-21 |

| Example 3-16 | Correct General Coding Rule 5                              | 3-22 |

| Example 3-17 | Error in Use of Cycle-Fixed Mode Coding Rule 1, for Loop3  | -23  |

| Example 3-18 | Correct Cycle-Fixed Mode Coding Rule 1, for Loop           | 3-23 |

| Example 3-19 | Error in Use of Cycle-Fixed Mode Coding Rule 1, while Loop | -24  |

| Example 3-20 | Correct Cycle-Fixed Mode Coding Rule 1, while              |      |

|              | loop                                                       | 3-24 |

| Example 3-21 | Error in Use of Cycle-Fixed Mode Coding Rule 1, do-while Loop | 3-25 |

|--------------|---------------------------------------------------------------|------|

| Example 3-22 | Correct Cycle-Fixed Mode Coding Rule 1,                       |      |

|              | do-while loop                                                 | 3-25 |

| Example 3-23 | Error in Use of Cycle-Fixed Mode Coding Rule 2                | 3-26 |

| Example 3-24 | Correct Cycle-Fixed Mode Coding Rule 2                        | 3-27 |

| Example 3-25 | Error in Use of Cycle-Fixed Mode Coding Rule 2,               |      |

|              | Write                                                         | 3-27 |

| Example 3-26 | Correct Cycle-Fixed Mode Coding Rule 2, Write                 | 3-28 |

| Example 3-27 | Error in Use of Cycle-Fixed Mode Coding Rule 3                | 3-29 |

| Example 3-28 | Correct Cycle-Fixed Mode Coding Rule 3                        | 3-29 |

| Example 3-29 | Error in Use of Superstate-Fixed Mode Coding                  |      |

|              | Rule 1                                                        | 3-30 |

| Example 3-30 | Correct Superstate-Fixed Mode Coding Rule 1                   | 3-30 |

| Example 3-31 | Error in Use of Superstate-Fixed Mode Coding                  |      |

|              | Rule 2                                                        | 3-31 |

| Example 3-32 | Correct Superstate-Fixed Mode Coding Rule 2                   | 3-31 |

| Example 3-33 | Operations That Are Not Mutually Exclusive                    | 3-32 |

| Example 3-34 | Mutually Exclusive Operations                                 | 3-32 |

| Example 3-35 | Labeling a Loop                                               | 3-34 |

| Example 3-36 | Structure of a while Loop                                     | 3-35 |

| Example 3-37 | Infinite while Loop                                           | 3-35 |

| Example 3-38 | Structure of dowhile Loop                                     | 3-36 |

| Example 3-39 | for Loop                                                      | 3-36 |

| Example 3-40 | Unrolled for Loop Compiler Directive          | 3-37 |

|--------------|-----------------------------------------------|------|

| Example 3-41 | Unrolled for Loop and Its Execution           | 3-38 |

| Example 3-42 | When to Use unroll                            | 3-40 |

| Example 3-43 | Selective Unrolling of a for Loop             | 3-41 |

| Example 3-44 | for Loop Without Static Exit Condition        | 3-42 |

| Example 3-45 | Consecutive Loops With Overhead               | 3-43 |

| Example 3-46 | Collapsed Consecutive Loops                   | 3-44 |

| Example 3-47 | Global Reset Watching                         | 3-47 |

| Example 4-1  | Member Function                               | 4-3  |

| Example 4-2  | Creating Preserved Functions                  | 4-7  |

| Example 4-3  | Nonmember Preserved Function Declaration      | 4-9  |

| Example 4-4  | Preserved Function With Reference Parameter   | 4-10 |

| Example 4-5  | Using DesignWare Parts                        | 4-11 |

| Example 5-1  | Data Member Array                             | 5-2  |

| Example 5-2  | Array Local to a Process                      | 5-2  |

| Example 5-3  | Reading From a Variable Array                 | 5-3  |

| Example 5-4  | Writing to a Variable Array                   | 5-3  |

| Example 5-5  | Reading From a Signal Array                   | 5-4  |

| Example 5-6  | Writing to a Signal Array                     | 5-4  |

| Example 5-7  | Multiple Accesses to Slices in the Same Array | 5-5  |

| Example 5-8  | Multiple Array Accesses Using a Variable      | 5-6  |

| Example 5-9  | Accessing Slices of a Signal Array Location   | 5-6  |

| Example 5-10 | Mapping Specific Arrays to Register Files     | 5-10 |

| Example 5-11 | Declaring Local Memory Resources              | 5-12 |

| Example 5-12 | Multiple Arrays Accessing One Memory                | 5-13 |

|--------------|-----------------------------------------------------|------|

| Example 5-13 | Changing Memory Types                               | 5-14 |

| Example 5-14 | Incorrect Memory Read Timing for Cycle-Fixed        | 5-16 |

| Example 5-15 | Correct Memory Read Timing for Cycle-Fixed          | 5-16 |

| Example 5-16 | Redundant Memory Read                               | 5-18 |

| Example 5-17 | Array Location Assigned to Temporary Variable       | 5-18 |

| Example 6-1  | One-Way Handshake Protocol Behavioral Block         | 6-6  |

| Example 6-2  | Behavioral Block Responding to One-Way<br>Handshake | 6-13 |

| Example 6-3  | Two-Way Handshake Protocol From GCD Block           | 6-23 |

| Example 6-4  | Two-Way Handshake Protocol From Testbench           | 6-30 |

| Example 6-5  | Two-Way Handshake Using a while Loop                | 6-36 |

| Example 6-6  | Fast Two-Way Handshake Using while Loop             | 6-37 |

| Example 6-7  | Fast Two-Way Handshake Using wait_until             | 6-39 |

| Example 6-8  | Incorrect Loop Pipeline With Handshake              | 6-40 |

| Example 6-9  | Correct Handshake in a Pipelined Loop               | 6-43 |

| Example B-1  | Architectural Simulation Model                      | B-3  |

| Example B-2  | Behavioral Header File                              | B-8  |

| Example B-3  | Behavioral Implementation File.                     | B-9  |

| Example B-4  | Behavioral Synthesis to Gates Script                | B-10 |

| Example B-5  | Behavioral Testbench Header File                    | B-11 |

| Example B-6  | Behavioral Testbench Implementation File            | B-11 |

| Example B-7  | Behavioral Top-Level Simulation File                | B-14 |

| Example B-8  | RTL Header File                                     | B-16 |

| Example B-9  | RTL Implementation File B-1               | 7 |

|--------------|-------------------------------------------|---|

| Example B-10 | RTL Top-Level Simulation File B-20        | 0 |

| Example C-1  | Memory Controller Header File C-          | 6 |

| Example C-2  | Memory Controller Implementation File C-  | 7 |

| Example C-3  | Token Header File C-                      | 8 |

| Example C-4  | Memory Controller Command Types C-        | 8 |

| Example C-5  | Behavioral Header File C-1                | 1 |

| Example C-6  | Behavioral Implementation File C-12       | 2 |

| Example C-7  | Behavioral Synthesis to Gates Script C-13 | 3 |

| Example D-1  | FFT Functional Header File D-4            | 4 |

| Example D-2  | FFT Functional Description File D-        | 5 |

| Example D-3  | FFT Header File D-                        | 9 |

| Example D-4  | FFT Implementation File D-1               | 0 |

| Example D-5  | Behavioral Synthesis to Gates Script D-10 | 6 |

| Example D-6  | FFT Testbench Source D-1                  | 8 |

| Example D-7  | FFT Testbench Sink D-20                   | 0 |

| Example D-8  | FFT Testbench Top-Level Model D-2         | 1 |

| Example E-1  | IQ Header File E-                         | 5 |

| Example E-2  | IQ Implementation File E-                 | 7 |

| Example E-3  | Behavioral Synthesis to Gates Script E-10 | 6 |

## Preface

This preface includes the following sections:

- What's New in This Release

- About This Guide

- Customer Support

## What's New in This Release

This section describes the new features, enhancements, and changes included in SystemC Compiler version 2000.11-SCC1. Unless otherwise noted, you can find additional information about these changes later in this book.

#### **New Features**

SystemC Compiler version 2000.11-SCC1 includes the following new features:

- The write\_rtl command generates either a synthesizable RTL model or an RTL model optimized for simulation. This command provides a single interface to generate RTL models that replaces setting several dc\_shell variables and using the write command.

- Using either the write\_rtl or write command, you can write an RTL SystemC model optimized for simulation.

For information about these commands, see the *CoCentric*<sup>™</sup> *SystemC Compiler Behavioral User Guide*.

#### Enhancements

SystemC Compiler version 2000.11-SCC1 includes the following enhancements:

Synthesizable RTL models now contain operators such as +, which are used instead of instantiations of Synopsys DesignWare components like DW01\_add. Substitutions are made when possible. This eliminates the dependency on Synopsys-specific components for synthesizable RTL models, unless the behavioral description specifies them.

• The memory wrapper generation tool now allows you to specify a memory write latency in addition to a read latency.

You can now customize the address and data bus waveforms. In previous versions of the memory wrapper generation tool, address and data bus waveforms were fixed to the first cycle.

For information about this enhancement, see the *CoCentric*<sup>™</sup> SystemC Compiler Behavioral User Guide.

#### **Known Limitations and Resolved STARs**

Information about known problems and limitations, as well as about resolved Synopsys Technical Action Requests (STARs), is available in the *CoCentric SystemC Compiler Release Note* in SolvNET.

To see the CoCentric SystemC Compiler Release Note,

- 1. Go to the Synopsys Web page at http://www.synopsys.com and click SolvNET.

- 2. If prompted, enter your name and password. If you do not have a SOLV-IT! user name and password, you can obtain them at http://www.synopsys.com/registration.

- 3. Click Release Notes, then open the *CoCentric SystemC Compiler Release Note*.

## **About This Guide**

The CoCentric<sup>™</sup> SystemC Compiler Behavioral Modeling Guide describes system-level design terminology and explains how to develop or refine a SystemC model for behavioral synthesis with SystemC Compiler.

For information about SystemC, see the Open SystemC Community web site at http://www.systemc.org.

#### Audience

The CoCentric<sup>™</sup> SystemC Compiler Behavioral Modeling Guide is for system and hardware designers and electronic engineers who are familiar with the SystemC Class Library and the C or C++ language and development environment.

Familiarity with one or more of the following Synopsys tools is advantageous but not required:

- Synopsys Behavioral Compiler

- Synopsys Design Compiler

- Synopsys Scirocco VHDL Simulator

- Synopsys Verilog Compiled Simulator (VCS)

#### **Related Publications**

In addition to the *CoCentric™ SystemC Compiler Behavioral Modeling Guide*, see the following manuals:

- The CoCentric<sup>™</sup> SystemC Compiler Behavioral User Guide, which provides information about synthesize a refined SystemC behavioral module into an RTL or a gate-level netlist.

- The CoCentric<sup>™</sup> SystemC Compiler RTL User and Modeling Guide, which provides information about how to synthesize a SystemC RTL module. It also describes the coding guidelines and how to develop a SystemC RTL module for synthesis.

- The *SystemC HDL Cosimulation User Guide*, which provides information about cosimulating a system with mixed SystemC and HDL modules

- The *CoCentric SystemC Compiler Quick Reference*, which provides a list of commands with their options and a list of variables.

- The SystemC User's Manual available from the Open SystemC Community web site at http://www.systemc.org.

For additional information about SystemC Compiler and other Synopsys products, see

- Synopsys Online Documentation (SOLD), which is included with the software

- Documentation on the Web, which is available through SolvNET on the Synopsys Web page at http://www.synopsys.com

- The Synopsys Print Shop, from which you can order printed copies of Synopsys documents, at http://docs.synopsys.com

You can also refer to the documentation for the following related Synopsys products:

- Design Compiler

- Scirocco VHDL Simulator

- Verilog Compiled Simulator

## Conventions

The following conventions are used in Synopsys documentation.

| Convention     | Description                                                                                                                                                                                                                                               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Courier        | Indicates command syntax.                                                                                                                                                                                                                                 |

| Courier italic | Indicates a user-defined value in Synopsys<br>syntax, such as <i>object_name</i> . (A user-defined<br>value that is not Synopsys syntax, such as a<br>user-defined value in a Verilog or VHDL<br>statement, is indicated by regular text font<br>italic.) |

| Courier bold   | Indicates user input—text you type verbatim—<br>in Synopsys syntax and examples. (User input<br>that is not Synopsys syntax, such as a user<br>name or password you enter in a GUI, is<br>indicated by regular text font bold.)                           |

| []             | Denotes optional parameters, such as<br>pin1 [pin2 pinN]                                                                                                                                                                                                  |

|                | Indicates a choice among alternatives, such as<br>low   medium   high<br>(This example indicates that you can enter one<br>of three possible values for an option:<br>low, medium, or high.)                                                              |

| _              | Connects terms that are read as a single term by the system, such as set_annotated_delay                                                                                                                                                                  |

| Control-c      | Indicates a keyboard combination, such as holding down the Control key and pressing c.                                                                                                                                                                    |

| ١              | Indicates a continuation of a command line.                                                                                                                                                                                                               |

| /              | Indicates levels of directory structure.                                                                                                                                                                                                                  |

| Edit > Copy    | Indicates a path to a menu command, such as opening the Edit menu and choosing Copy.                                                                                                                                                                      |

## **Customer Support**

Customer support is available through SOLV-IT! and through contacting the Synopsys Technical Support Center.

#### Accessing SOLV-IT!

SOLV-IT! is the Synopsys electronic knowledge base, which contains information about Synopsys and its tools and is updated daily.

To access SOLV-IT!,

- 1. Go to the SolvNET Web page at http://solvnet.synopsys.com.

- 2. If prompted, enter your user name and password.

If you do not have a SOLV-IT! user name and password, you can obtain them at http://www.synopsys.com/registration.

If you need help using SOLV-IT!, click SolvNET Help in the column on the left side of the SolvNET Web page.

## **Contacting the Synopsys Technical Support Center**

If you have problems, questions, or suggestions, you can contact the Synopsys Technical Support Center in the following ways:

- Open a call to your local support center from the Web by going to http://solvnet.synopsys.com (SOLV-IT! user name and password required), then clicking "Enter a Call."

- Send an e-mail message to support\_center@synopsys.com.

- Telephone your local support center.

- Call (800) 245-8005 from within the continental United States.

- Call (650) 584-4200 from Canada.

- Find other local support center telephone numbers at http://www.synopsys.com/support/support\_ctr.

#### Training

For SystemC and SystemC Compiler training and private workshops, contact the Synopsys Customer Education Center in one of the following ways:

- Go to the Synopsys Web page at http://www.synopsys.com/ services/education.

- Telephone (800) 793-3448.

# 1

# Introduction

CoCentric SystemC Compiler synthesizes a SystemC behavioral hardware module into an RTL description or a gate-level netlist. (A future release of SystemC Compiler will provide synthesis of RTL descriptions.)

After synthesis, you can use other Synopsys tools for verification, test insertion, power optimization, and physical design.

This modeling guide defines system design terminology and explains how to develop and refine SystemC behavioral models for synthesis with SystemC Compiler. Before reading this modeling guide, read the *CoCentric SystemC Compiler User Guide* to learn about behavioral synthesis concepts and how to run the tool. This modeling guide assumes you are knowledgeable about the SystemC Class Library, available from the Open SystemC Community at http://www.systemc.org. Synthesizable behavioral design examples are available in Appendix B, "First-In-First-Out Example," Appendix C, "Memory Controller Example," Appendix D, "Fast Fourier Transform Example," and Appendix E, "Inverse Quantization Example" for an MPEG-2 decoder. These examples show you various coding styles and design techniques used with SystemC Compiler.

This chapter contains the following sections:

- Defining Levels of Abstraction in System Design

- Choosing the Right Abstraction for Synthesis

## **Defining Levels of Abstraction in System Design**

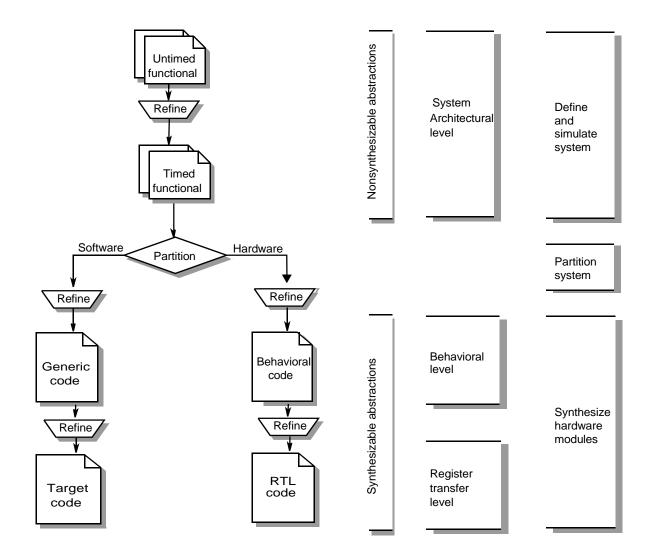

Figure 1-1 shows the traditional levels of abstraction in system design: system architectural level, behavioral level, and RTL. This section describes the traditional levels of abstraction, their purpose, characteristics, and coding style.

#### Figure 1-1 System Design Levels of Abstraction

## **Architectural Level**

In a typical top-down design flow, you start with a purely functional model of your system. This functional model is a software program that describes the system functionality so that it can be validated. This functional model is then mapped into a system architectural model. In addition to the system functionality, the system architectural model describes its architecture (buses, memory, processors, peripherals, and so forth).

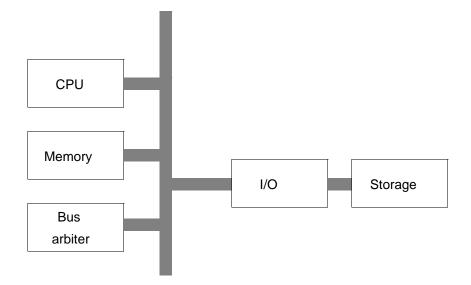

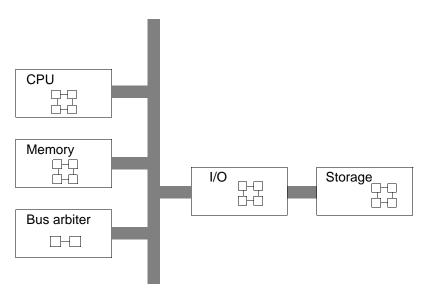

A system architectural model, illustrated in Figure 1-2, is algorithmic in nature. It may be an untimed or timed model. The model is an accurate description of the system behavior, although the description is abstract. The interfaces between modules are transaction oriented and event driven, rather than cycle accurate.

Figure 1-2 Architectural Model

## **Untimed Functional Model**

An untimed functional model is an executable specification of the system. The system is described as a set of processes, communicating through abstract communication links. The system may be described in a sequential form, concurrent form, or a combination of both. Time is expressed as causality.

## **Timed Functional Model**

A timed functional model is a performance model at a high level of abstraction. The processes and communication links in the untimed functional model are assigned execution times, specified in clock cycles or actual time.

## **Functional Coding Style**

A functional model uses a coding style that is abstract, concise, easy to write, and functionally accurate. You can use the SystemC classes and data types, or you can code the functionality by using only the C/C++ language.

Example 1-1 shows a functional model of a simple first-in-first-out (FIFO) circular buffer. (The complete description and set of files for the available in Appendix B, "First-In-First-Out Example.")

Example 1-1 FIFO Functional Model

/\*

```

fifo.cc executable specification.

This model works for a FIFO

with a size that is a power of 2.

*/

#include "systemc.h"

#define BUFSIZE 4

#define LOGBUFSIZE 2

struct circ buf {

// The FIFO buffer

int buffer[BUFSIZE];

sc_uint<LOGBUFSIZE> headp; // Pointer to head of FIFO

sc_uint<LOGBUFSIZE> tailp; // Pointer to tail of FIFO

// Number of buffer elements

int num_in_buf;

// Routine to initialize the FIFO

void init() {

num_in_buf = 0;

headp = 0;

tailp = 0;

}

// Constructor

circ_buf() {

init();

}

void status(); // Status of the FIFO

int road(); // To road from the F

// To read from the FIFO

int read();

void write(int data); // To write to the FIFO

bool is_full(); // To determine if FIFO is full

// To determine if FIFO is empty

bool is_empty();

};

int

circ_buf::read() {

if (num_in_buf) {

num_in_buf--;

return (buffer[headp++]);

}

// Otherwise ignore read request

}

```

```

void

circ_buf::write(int data) {

if (num_in_buf < BUFSIZE) {</pre>

buffer[tailp++] = data;

num_in_buf++;

}

// Otherwise ignore write request

}

bool

circ_buf::is_full() {

return (num_in_buf == BUFSIZE);

}

bool

circ buf::is empty() {

return (num_in_buf == 0);

}

void

circ_buf::status() {

cout << "FIFO is ";</pre>

if(is_empty()) cout << "empty\n" ;</pre>

else if (is_full()) cout << "full\n" ;</pre>

else cout << "neither full nor empty\n";

}

int

main()

{

circ_buf fifo; // instantiate buffer

// This is the testbench for the FIFO

fifo.status();

cout << "FIFO write 1\n"; fifo.write(1);</pre>

cout << "FIFO write 2\n"; fifo.write(2);</pre>

cout << "FIFO write 3\n"; fifo.write(3);</pre>

fifo.status();

cout << "FIFO write 4\n"; fifo.write(4);</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

cout << "FIFO read " << fifo.read() << endl;</pre>

cout << "FIFO read " << fifo.read() << endl;</pre>

```

```

fifo.status();

cout << "FIFO write 1\n"; fifo.write(1);</pre>

cout << "FIFO write 2\n"; fifo.write(2);</pre>

cout << "FIFO write 3\n"; fifo.write(3);</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

cout << "FIFO read " << fifo.read() << endl;</pre>

fifo.status();

cout << "FIFO write 4\n"; fifo.write(4);</pre>

cout << "FIFO write 5\n"; fifo.write(5);</pre>

fifo.status();

cout << "FIFO write 6\n"; fifo.write(6);</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

cout << "FIFO read " << fifo.read() << endl;</pre>

fifo.status();

cout << "FIFO read " << fifo.read() << endl;</pre>

fifo.status();

return 0;

```

}

## **Behavioral Model**

A behavioral model of a block in a system is an algorithmic description of the block's behavior. Unlike a pure software program, however, the I/O behavior of the block is described in a cycle-accurate fashion. Therefore, wait statements are inserted into the algorithmic description to clearly delineate clock-cycle boundaries and when I/O happens. Unlike register-transfer-level (RTL) descriptions, the behavior of the block is still described algorithmically rather than in terms of a finite state machine (FSM) and a data path. Therefore, behavioral descriptions are more compact, and easier to understand, and because of the higher level of abstraction, they simulate faster than RTL.

Figure 1-3 shows a block diagram for a behavioral model.

Figure 1-3 Behavioral Model

## **Behavioral Coding Style**

The general characteristics of the behavioral coding style for synthesis are the following:

- The behavior is described like an algorithm (a software program), and functions can be used to manage complexity.

- Although the initial model may have float or integer data types, you need to refine these types to synthesizable types, described in "Recommended Types for Synthesis" on page 2-39.

- You specify the I/O protocol of the design by defining in which clock cycle the I/O happens. Note that only the I/O, not the operations described in the algorithm, is bound to clock cycles.

- It uses the synthesizable subset of the SystemC language, described in "SystemC and C++ Synthesizable Subset" on page 2-32

## **Refining From Functional to Behavioral Model**

To refine a functional model into a behavioral model,

- Restrict constructs to the synthesizable subset of C++. See the "Nonsynthesizable Subset of SystemC" on page 2-33.

- Refine ports from abstract data types to synthesizable data types, and refine all other data types to synthesizable data types, which are described in "Synthesizable Data Types" on page 2-37.

- Define a clock port for the module.

- Specify the I/O interface by adding wait statements to your description and put signal and port read and write operations with the correct wait statements, described in Chapter 3, "Behavioral Coding Guidelines."

• If required, manage complexity by using functions.

Chapter 2, "Refining for Behavioral Synthesis" describes the refinement activities in more detail.

Example 1-2 shows a behavioral description of the FIFO that was refined from the algorithmic description in Example 1-1 on page 1-6. The design description and complete set of files for the FIFO are available in Appendix B, "First-In-First-Out Example."

Example 1-2 FIFO Behavioral Coding

```

/* fifo_bhv.h header file */

#define BUFSIZE 4

#define LOGBUFSIZE 2

#define LOGBUFSIZEPLUSONE 3

SC_MODULE(circ_buf) {

// The clock

sc_in_clk clk;

sc_in<bool> read_fifo; // Indicate read from FIFO

sc_in<bool> write_fifo; // Indicate write to FIFO

sc_in<int> data_in; // Data written to FIFO

sc_in<bool> reset;

// Reset the FIFO

sc_out<int> data_out; // Data read from the FIFO

sc_out<bool> full; // Indicate FIFO is full

// Indicate FIFO is empty

sc out<bool> empty;

// FIFO buffer

int buffer[BUFSIZE];

sc uint<LOGBUFSIZE> headp; // Pointer to FIFO head

sc_uint<LOGBUFSIZE> tailp; // Pointer to FIFO tail

// Counter for number of elements

sc_uint<LOGBUFSIZEPLUSONE> num_in_buf;

void read_write(); // FIFO process

SC_CTOR(circ_buf) {

SC_CTHREAD(read_write, clk.pos());

watching(reset.delayed() == true);

}

};

/* fifo bhv.cc implementation file */

#include "systemc.h"

#include "fifo_bhv.h"

void

circ_buf::read_write() {

// Reset operations

headp = 0;

tailp = 0;

num_in_buf = 0;

full = false;

empty = true;

data_out = 0;

```

```

wait();

// Main loop

while (true) {

if (read_fifo.read()) {

// Check if FIFO is not empty

if (num_in_buf != 0) {

num_in_buf--;

data_out = buffer[headp++];

full = false;

if (num_in_buf == 0) empty = true;

}

// Ignore read request otherwise

wait();

}

else if (write_fifo.read()) {

// Check if FIFO is not full

if (num_in_buf != BUFSIZE) {

buffer[tailp++] = data_in;

num_in_buf++;

empty = false;

if (num_in_buf == BUFSIZE) full = true;

}

// Ignore write request otherwise

wait();

}

else {

wait();

}

}

```

}

## **Register Transfer Level Model**

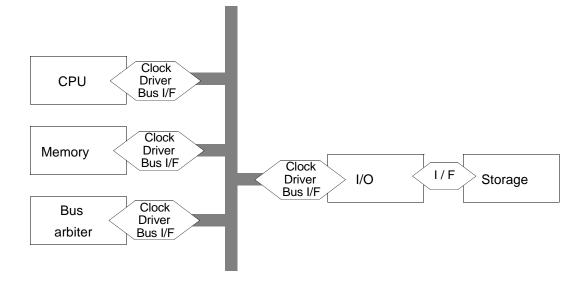

An RTL model describes registers in your design and the combinational logic between the registers. As such, the functionality of your system is specified as an FSM and a data path. Because register updates are tied to a clock, the model is cycle accurate, both at the interfaces and also internally. Internal cycle accuracy means the clock cycle in which each operation is performed is specified. This is different from a behavioral model that is cycle accurate at the interface, and the operation execution is not cycle accurate

Figure 1-4 shows a block diagram for a cycle-accurate model.

## **RTL Coding Style**

The general characteristics of the RTL coding style for synthesis are the following:

- Implements the design as combinational logic between registers. The finite state machine and the data path are explicitly specified.

- Uses only the synthesizable data types, described in "Synthesizable Data Types" on page 2-37.

- Uses the synthesizable subset of the C++ language, described in "SystemC and C++ Synthesizable Subset" on page 2-32.

## **Refining into RTL**

To refine a behavioral model into a RTL model

- Separate the control logic and data path.

- Determine the data-path architecture.

- Define an explicit FSM for the control logic.

Example 1-3 shows the RTL version of the FIFO behavioral model in Example 1-2. The RTL coding style has separate processes for the FSM control and data path. Notice that the RTL version of the FIFO is much longer and more detailed than the equivalent behavioral version, and it is harder to follow than the behavioral description. For details about refining a functional or behavioral model into an RTL model, see the *SystemC Compiler RTL Modeling Guide*.

#### Example 1-3 RTL Coding

```

/* fifo_rtl.h header file */

#define BUFSIZE 4

#define LOGBUFSIZE 2

#define LOGBUFSIZEPLUSONE 3

SC_MODULE(circ_buf) {

// Same I/O as behavioral

sc_in<bool> clk;

sc_in<bool> read_fifo;

sc_in<bool> write_fifo;

sc_in<int> data_in;

sc in<bool> reset;

sc_out<int> data_out;

sc_out<bool> full;

sc_out<bool> empty;

// Internal signals

sc_signal<int> buf0, buf0_next;

sc_signal<int> buf1, buf1_next;

sc_signal<int> buf2, buf2_next;

sc_signal<int> buf3, buf3_next;

sc_signal<sc_uint<LOGBUFSIZEPLUSONE> >

num_in_buf, num_in_buf_next;

sc_signal<bool> full_next, empty_next;

sc_signal<int> data_out_next;

// Declare processes

void ns logic(); // Next-state logic

void update_regs();// Update all registers

void gen_full(); // Generate a full signal

void gen_empty(); // Generate an empty signal

// Constructor

SC_CTOR(circ_buf) {

SC_METHOD(ns_logic);

sensitive << read fifo << write fifo

<< data_in << num_in_buf;

SC_METHOD(update_regs);

sensitive_pos << clk;</pre>

SC METHOD(gen full);

sensitive << num_in_buf_next;</pre>

```

```

SC_METHOD(gen_empty);

sensitive << num_in_buf_next;</pre>

}

};

/* fifo_rtl.cc implementation file */

#include "systemc.h"

#include "fifo_rtl.h"

void circ_buf::gen_full(){

if (num_in_buf_next.read() == BUFSIZE)

full_next = 1;

else

full_next = 0;

}

void circ_buf::gen_empty(){

if (num_in_buf_next.read() == 0)

empty_next = 1;

else

empty_next = 0;

}

void circ_buf::update_regs(){

if (reset.read() == 1) {

full = 0;

empty = 1;

num in buf = 0;

buf0 = 0;

buf1 = 0;

buf2 = 0;

buf3 = 0;

data out = 0;

}

else {

full = full_next;

empty = empty_next;

num_in_buf = num_in_buf_next;

buf0 = buf0_next;

buf1 = buf1_next;

buf2 = buf2_next;

buf3 = buf3_next;

data_out = data_out_next;

}

}

void circ_buf::ns_logic(){

```

```

// Default assignments

buf0_next = buf0;

buf1_next = buf1;

buf2_next = buf2;

buf3_next = buf3;

num_in_buf_next = num_in_buf;

data_out_next = 0;

if (read_fifo.read() == 1) {

if (num_in_buf.read() != 0) {

data_out_next = buf0;

buf0_next = buf1;

buf1_next = buf2;

buf2 next = buf3;

num_in_buf_next = num_in_buf.read() - 1;

}

}

else if (write_fifo.read() == 1) {

switch(int(num_in_buf.read())) {

case 0:

buf0_next = data_in.read();

num_in_buf_next = num_in_buf.read() + 1;

break;

case 1:

buf1_next = data_in.read();

num_in_buf_next = num_in_buf.read() + 1;

break;

case 2:

buf2_next = data_in.read();

num_in_buf_next = num_in_buf.read() + 1;

break;

case 3:

buf3_next = data_in.read();

num_in_buf_next = num_in_buf.read() + 1;

default:

// ignore the write command

break;

}

}

```

Introduction

}

## **Choosing the Right Abstraction for Synthesis**

You can implement a hardware module by using behavioral-level synthesis or RTL synthesis. Behavioral descriptions are smaller, make it easier to capture complex algorithms, are faster to simulate, accommodate late specification changes, and are more intuitive to write and understand (and therefore maintain) than RTL descriptions.

At this level of abstraction, the model's architecture refers to its hardware implementation, which is not yet specified.

Behavioral synthesis, however, is not suitable for all modules of a design. Evaluate each design module by module, and consider each module's attributes, described in the following sections, to determine whether behavioral or RTL synthesis is applicable.

### Identifying Attributes Suitable for Behavioral Synthesis

Look for the following design attributes when identifying a hardware module that is suitable for behavioral synthesis with SystemC Compiler:

- It is easier to conceive the design as an algorithm than as an FSM and a data path for example, an FFT, filter, IQ, or DSP.

- The design has a complex control flow for example, a network processor.

- The design has memory accesses, and you need to synthesize access to synchronous memory.

Applications that are suitable for behavioral modeling and synthesis are

- Digital communication applications such as cable modems, cellular phones, cordless phones, two-way pagers, wireless LANs, satellite DSPs, and XDSL modems

- Image and video processing applications such as digital cameras, printers, set-top boxes, 3-D graphic devices, and video capture devices

- Networking applications such as ATM switches, fast networking switches, and packet routers

- Digital signal processing applications such as filters, codecs, IQ, IDCT, and channel equalizers

- Computers applications such as cache controllers, hardware accelerators, and fixed-point arithmetic units

## Identifying Attributes Suitable for RTL Synthesis

Some designs are more appropriate for RTL synthesis than for behavioral synthesis. The following design attributes indicate that the design is suitable for RTL synthesis:

- The design is asynchronous.

- It is easier to conceive the design as an FSM and a data path than as an algorithm for example, a microprocessor.

- The design is very high performance, and the designer, therefore, needs complete control over the architecture.

- The design contains complex memory such as SDRAM or RAMBUS.

## **Comparison of Behavioral and RTL Synthesis**

The following are benefits of behavioral synthesis compared to RTL synthesis.

A behavioral description

- Promotes communication of design intent

- Is usually smaller than RTL code

- Promotes greater design reuse, because the design is technology and architecture independent

- Accommodates late design specification changes, because the code is architecture independent

- Cuts implementation time significantly, increasing designer productivity

- Increases verification speed and decreases verification time

- Promotes exploration of alternative architectures

- Automatically creates the control FSM and data path

- Pipelines critical parts of the design such as loops

- Shares operators and registers

- Automatically synthesizes memory accesses

This modeling guide tells you how to develop descriptions for behavioral synthesis with SystemC Compiler.

# **Refining for Behavioral Synthesis**

This chapter explains how to refine a high-level SystemC model or a purely C/C++ model into a behavioral model that can be synthesized with SystemC Compiler. The SystemC and C/C++ language elements that are important for synthesis are also described.

This chapter contains the following sections:

- Refinement Overview

- Creating and Refining the Structure From a C/C++ Model

- Refining the Structure From a High-Level SystemC Model

- Creating and Refining Processes

- Converting to a Synthesizable Subset

- Refining Data

- Refining Control

- Advanced Refinement Techniques

- Refinement Recommendations

Refining for Behavioral Synthesis

## **Refinement Overview**

Assuming that you have decided on the architecture for your system and have identified the functionality you want to synthesize with SystemC Compiler, you need to refine the functional model for synthesis. For information about deciding on an system architecture and other design methodology tradeoffs, refer to books and other information sources about design methodology.

Starting with either a purely C/C++ model or a high-level SystemC model, the stages for refining the high-level model into a behavioral model for synthesis with SystemC Compiler are

- Structure refinement

- Data refinement

- Control refinement

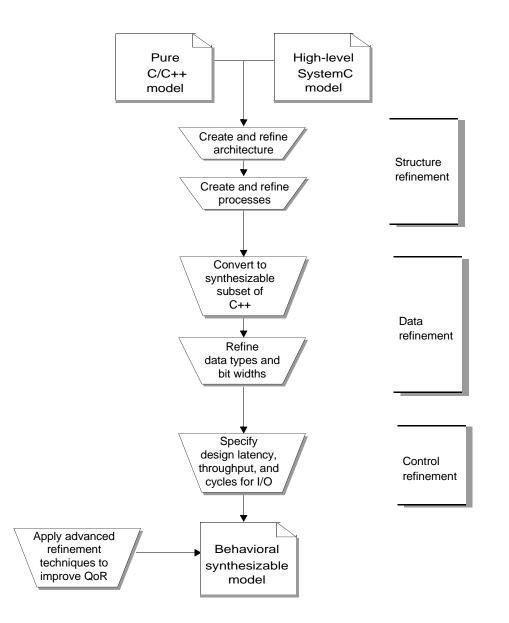

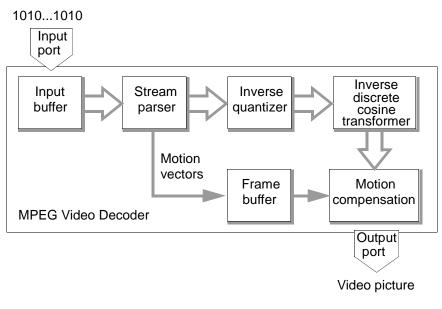

Figure 2-1 shows the three major stages for refining the model and the activities in each stage.

#### Figure 2-1 Refinement Stages and Activities

For structure refinement, you create the architecture of your design, which is the hierarchical structure, and the communication your design uses. For data refinement, you restrict the model to use only the synthesizable subset of C++ and you choose appropriate data types and bit-widths.

For control refinement, you specify the latency of the design and the cycles in which I/O happens. You also need to ensure that your model adheres to the coding rules required for synthesis.

After synthesis, you can use advanced refinement techniques such as preserved functions ("Using Preserved Functions" on page 4-4) and loop recoding ("Using Loops" on page 3-33) to further refine your design and achieve a higher quality of results (QoR).

You typically perform the refinement activities in the order shown in Figure 2-1. You do not need to complete each stage before going on to the next stage. You may want to partially complete stages and iterate over the entire set of stages several times to develop a synthesizable model.

## Creating and Refining the Structure From a C/C++ Model

A pure C/C++ model of your hardware describes only what the hardware is intended to do. When you start with a C/C++ model, the goal of the first refinement stage is to create the hardware structure. To synthesize the hardware, you need to

- Define I/O ports for the hardware module

- Specify the internal structure as blocks

- Specify the internal communication between the blocks

- Define the clock and reset signals, described in Chapter 3, "Behavioral Coding Guidelines"

#### **Define I/O Ports**

To define I/O ports for the hardware, you need to determine input ports for reading data into the module and output ports for writing data out from the module. Ports are communication resources, and they can be shared. You can define any number of ports, dedicate a port for each I/O, or share ports for I/O based on the requirements of your design.

#### **Specify Internal Structure**

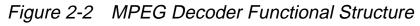

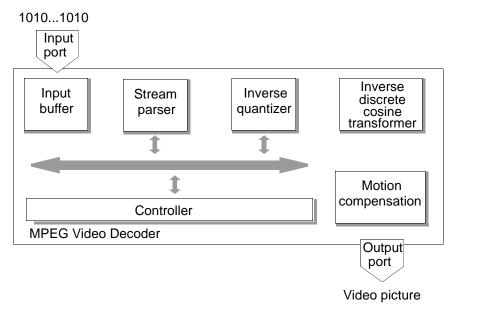

Next, you need to specify the internal structure of your design as blocks. Structuring the hardware depends on the way you conceptualize your design and how you intend to synthesize the design with SystemC Compiler. For example, consider an MPEG decoder. You can conceptualize an MPEG decoder to consist of an input port that accepts an MPEG stream, an output port that produces a decoded MPEG stream, an inverse quantizer (IQ) block, an inverse discrete cosine transformer (IDCT) block, an MPEG stream parser (SP) block, a motion compensation (MC) unit block, input and output buffers (IBs and OBs), and a controller (CT) that controls all the other blocks. Figure 2-2 shows an initial structure of an MPEG design with these blocks.

### **Specify the Internal Communication**

After you determine the blocks of your design, you need to decide how these blocks communicate with one another. You can use dedicated communication resources between blocks, or you can use a shared communication resource such as a bus. For the blocks in your design, you need to decide what ports they use and what communication resources are used to connect them. For the MPEG example, assume that a bus was chosen. The blocks and the communication between them determines the top-level architecture of your design, as shown in Figure 2-3.

Figure 2-3 MPEG Decoder Top-Level Architecture

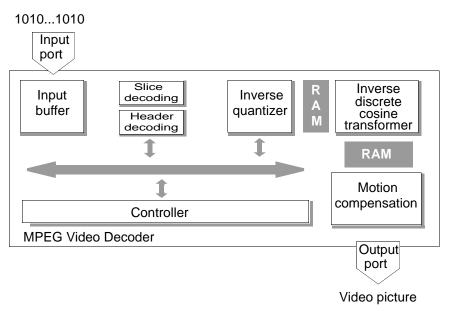

#### **Specify the Detailed Architecture**

After the top-level architecture is complete, you can take a closer look at each block of the design to decide if you want to apply the same principles of structure refinement to all the blocks. For example, you might want to decompose the MPEG stream parser block into a slice decoding (SD) block and a header decoding (HD) block. You might also want to insert buffers (B) between the IQ and IDCT and between the IDCT and MC. This further refines your architecture and creates hierarchy in your design, as shown in Figure 2-4.

Figure 2-4 MPEG Decoder Detailed Architecture

Continue this type of structure refinement until you are satisfied with the final architecture. In your final architecture, all blocks, their ports, and all communication resources are defined. Though it is not required to have the communication protocols defined at this stage, it is highly recommend that you define the bus protocols and protocols used on dedicated links. You will use the protocol later, during the control refinement stage, to specify when I/O happens.

### **Atomic and Hierarchical Blocks**

In your final architecture, blocks can be atomic, which means they do not contain other blocks. You can also have blocks that are hierarchical, which means they contain other blocks. In the MPEG example, the MPEG decoder and the SP blocks are hierarchical and the other blocks are atomic. You need to create a SystemC module for each atomic block and a SystemC signal for each communication resource, which is described in "Modules" on page 2-12. A SystemC module can contain only SystemC behavioral or RTL processes. (This document describes only behavioral processes. For information about RTL processes, see the *CoCentric™ SystemC Compiler RTL User and Modeling Guide*.)

For each atomic block, you

- Create a SystemC module

- Define input and output ports

- Define the clock and reset ports (the clock port is mandatory, and the reset port is highly recommended)

- Create a behavioral clocked thread process

- Declare reset watching

For each hierarchical block, you create a SystemC module in which you can define processes as well as instantiations of other modules.

SystemC Compiler synthesizes processes in a module, and their interconnection is inferred from the module instantiation. To synthesize hierarchical modules, RTL synthesis is required. How to create hierarchical modules and integrated behavioral and RTL modules is described in the *CoCentric™ SystemC Compiler RTL User and Modeling Guide*.

When creating the hardware structure, adhere to the following guidelines:

- A hierarchical module contains instances of other modules and the interconnections between the instances. The hierarchical module can contain RTL processes, but it cannot contain behavioral processes.

- Each atomic module for behavioral synthesis can contain only clocked thread processes.

- For behavioral synthesis, if SystemC Compiler runtime is excessive, you can break your module into smaller modules.

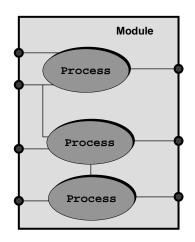

## Modules

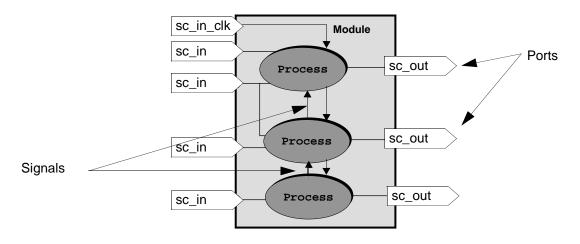

The basic building block in SystemC is a module. A SystemC module is a container in which processes and other modules are instantiated. Figure 2-5 shows a typical module with several processes. The processes within a module are concurrent.

Figure 2-5 Module

Note:

For synthesis with SystemC Compiler version 2000.05-SCC1.0, a module cannot contain instances of other modules.

As a recommended coding practice, describe a module by using two separate files, a separate header file (*module\_name*.h) and an implementation file (*module\_name*.cpp or *module\_name*.cc).

## Module Header File

Each module header file contains the module declaration, which includes

- Port declarations

- Internal signal variable declarations

- Internal data variable declarations

- Process declarations

- Member function declarations

- Constructor of the module

#### Module Syntax

Declare a module by using the syntax shown in bold in the following example:

```

SC_MODULE (module_name) {

//Module port declarations

//Signal variable declarations

//Data variable declarations

//Clocked thread process declarations

//Member function declarations

//Module constructor

SC_CTOR (module_name) {

//Register processes

//Declare sensitivity list

//Define global watching

}

};

```

Note:

SC\_MODULE and SC\_CTOR are C++ macros defined in the System Class library.

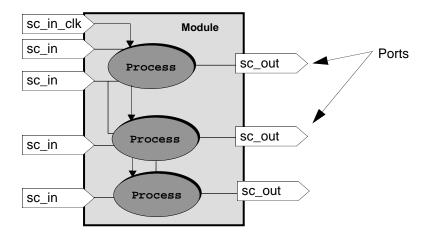

## **Module Ports**

Each module has any number of input and output ports (Figure 2-6), which determine the direction of data into or out of the module.

Figure 2-6 Module Ports

A port is a data member of SC\_MODULE. You can declare any number of sc\_in or sc\_out ports. For a module with a behavioral (SC\_THREAD) process, you must declare one sc\_in\_clk port.

Note:

SystemC sc\_inout ports are not used for behavioral synthesis.

#### Port Syntax

Declare ports by using the syntax shown in bold in the following example:

```

SC_MODULE (module_name) {

//Module port declarations

sc_in<port_data_type> port_name;

sc_out<port_data_type> port_name;

sc_in_clk port_name; // Mandatory

sc_in<bool> reset; // Highly recommended

//Signal variable declarations

//Data variable declarations

//Clocked thread processes

//Member function declarations

//Module constructor

SC_CTOR (module_name) {

//Register processes

//Declare sensitivity list

//Define global watching

}

};

```

#### **Port Data Types**

Ports connect to signals and, like signals, have a data type associated with them. For synthesis, declare each port as one of the synthesizable data types, described in "Synthesizable Data Types" on page 2-37.

An sc\_in\_clk is a special port that connects to the clock signal to trigger one or more SC\_CTHREAD processes. Each SC\_CTHREAD process requires one sc\_in\_clk port. You can use the same clock port for all processes in a module, or you can declare a separate sc\_in\_clk port for each SC\_CTHREAD process.

## **Internal Signals**

Modules use ports to communicate with other modules. Internal signals are used by processes to communicate with other processes within the same module, as shown in Figure 2-7.

#### Figure 2-7 Processes and Signals

#### Signal Syntax

Declare signals by using the syntax shown in bold in the following example:

```

SC_MODULE (module_name) {

//Module port declarations

sc_in<port_type> port_name;

sc_out<port_type> port_name;

sc_in_clk port_name;

//Internal signal variable declarations

sc_signal<signal_type> signal_name;

//Data variable declarations

//Clocked thread processes

//Member function declarations

//Module constructor

SC_CTOR (module_name) {

//Register processes

//Declare sensitivity list

//Define global watching

}

};

```

#### Signal Data Types

A signal's bit-width is determined by its corresponding data type. Specify the data type as any of the synthesizable SystemC or C++ data types listed in "Synthesizable Data Types" on page 2-37. Signals and the ports they connect must have compatible data types.

## **Reading and Writing Ports**

When you read a port, it is recommended to use the read() and write() methods to distinguish ports from variable assignments. Example 2-1 shows in bold how to use these methods rather than simple assignments.

Example 2-1 Using read() and write() Methods

```

//...

wait();

address = into.read(); // read from into port

wait(); // wait one clock

data_tmp = memory[address]; // get data from memory

outof.write(data_tmp); // write to outof port

wait();

//...

```

You need to read or write all bits of a port. You cannot read or write the individual bits, regardless of its type. To select a bit on a port, read the port data into a temporary variable and select a bit in the temporary variable.

### **Reading and Writing Signals**

You can read or write a signal using either the read() and write() methods or by assignment. You cannot read or write the individual bits, regardless of its type. To select a bit on a signal, read the signal data into a temporary variable and select a bit in the temporary variable.

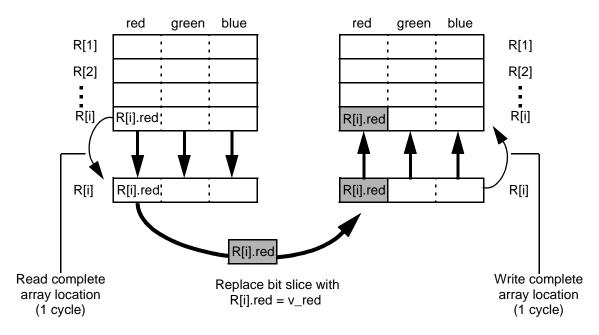

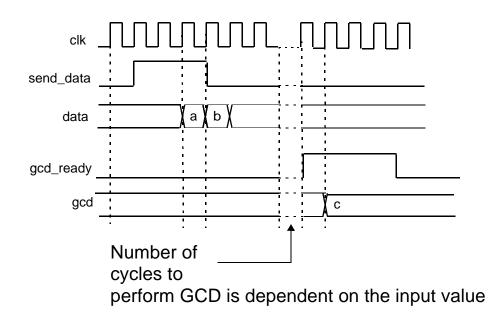

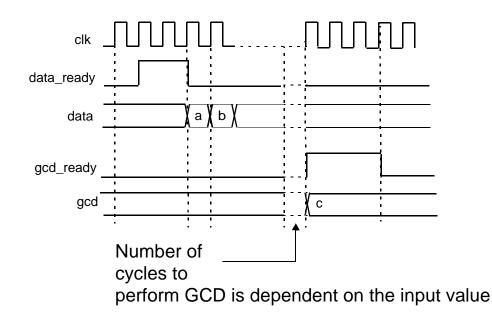

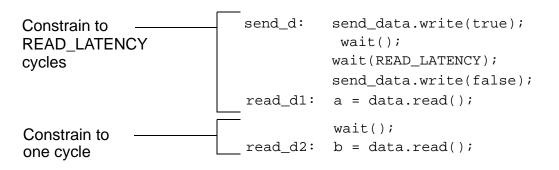

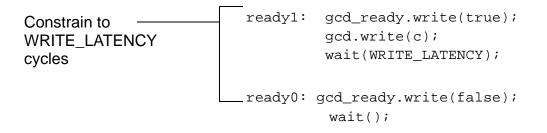

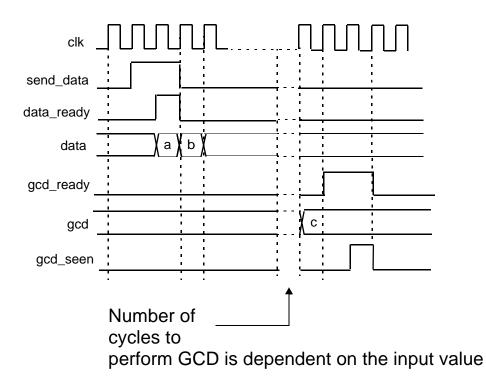

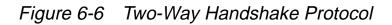

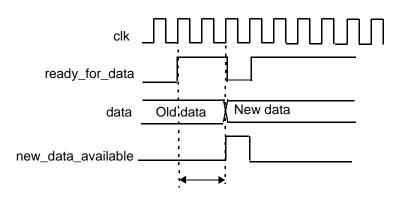

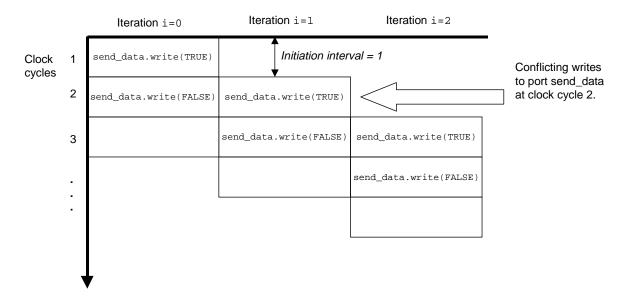

## **Internal Data Variables**