# Beginners Introduction to the Assembly Language of ATMEL-AVR-Microprocessors

## by

## **Gerhard Schmidt**

## http://www.avr-asm-tutorial.net

## February 2011

#### History:

Added page on assembler concept in February 2011

Added chapter on code structures in April 2009

Additional corrections and updates as of January 2008

Corrected version as of July 2006

Original version as of December 2003

# Content

| 1 Why learning Assembler?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 2 The concept behind the language assembler in micro-controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

| 2.1 The hardware of micro-controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                                                                                                      |

| 2.2 How the CPU works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                                      |

| 2.3 Instructions in assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                                                                                                                                      |

| 2.4 Difference to high-level languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                                      |

| 2.5 Assembler is not machine language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

| 2.6 Interpreting and assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

| 2.7 High level languages and Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

| 2.8 What is really easier in assembler?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                        |

| 3 Hardware for AVR-Assembler-Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

| 3.1 The ISP Interface of the AVR processor family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| 3.2 Programmer for the PC-Parallel-Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

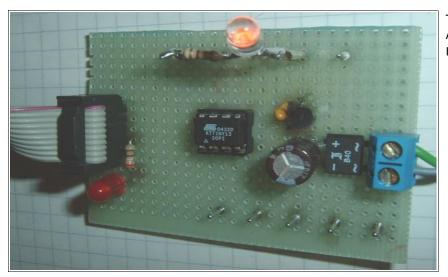

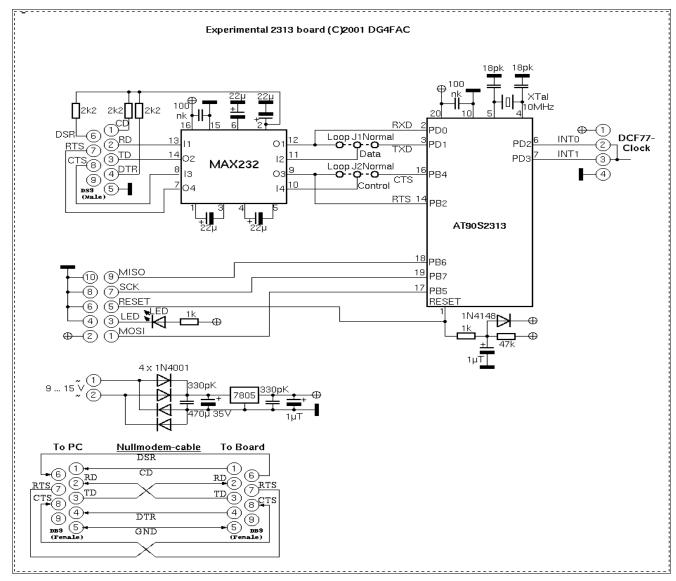

| 3.3 Experimental boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                        |

| 3.3.1 Experimental board with an ATtiny13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| 3.3.2 Experimental board with an AT90S2313/ATmega2313                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

| 3.4 Ready-to-use commercial programming boards for the AVR-family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| 3.4.1 STK200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 3.4.2 STK500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 3.4.3 AVR Dragon.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| 4 Tools for AVR assembly programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

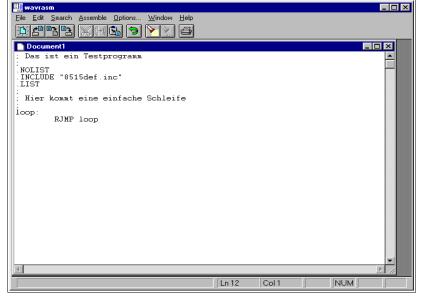

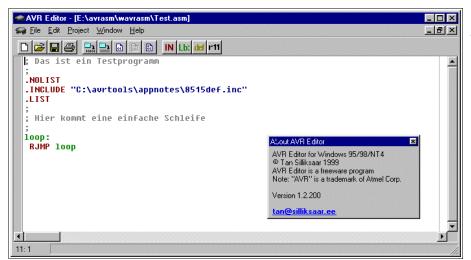

| 4.1 The editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

| 4.1.1 A simple typewriter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| 4.1.2 Structuring assembler code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

| 4.1.2 Structuring assembler code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |

| 4.3 Programming the chips.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

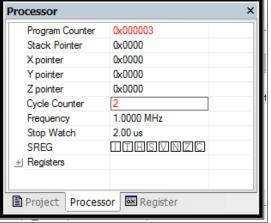

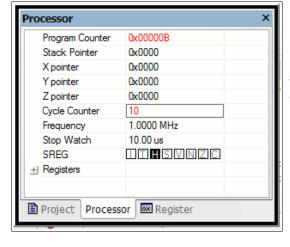

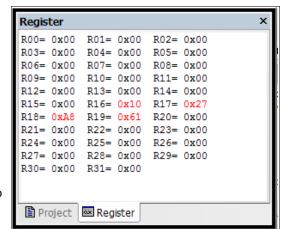

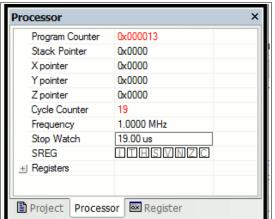

| 4.4 Simulation in the studio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 5 What is a register?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

| 5.1 Different registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

| 50D:4 :4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

| 5.2 Pointer-registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

| 5.2.1 Accessing memory locations with pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                     |

| 5.2.1 Accessing memory locations with pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                     |

| 5.2.1 Accessing memory locations with pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22<br>22<br>23                                                                                                                         |

| 5.2.1 Accessing memory locations with pointers 5.2.2 Reading program flash memory with the Z pointer 5.2.3 Tables in the program flash memory 5.2.4 Accessing registers with pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22<br>23<br>23                                                                                                                         |

| 5.2.1 Accessing memory locations with pointers 5.2.2 Reading program flash memory with the Z pointer 5.2.3 Tables in the program flash memory 5.2.4 Accessing registers with pointers 5.3 Recommendation for the use of registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22<br>22<br>23<br>23<br>24<br>25<br>25                                                                                                 |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22<br>22<br>23<br>23<br>24<br>25<br>25                                                                                                 |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25                                                                                           |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25<br>26                                                                                     |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26                                                                               |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26                                                                               |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26                                                                         |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details.                                                                                                                                                                                                                                                                                                                                                                                                                             | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>27<br>28                                                             |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM.                                                                                                                                                                                                                                                                                                                                                                                                                     | 22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28                                                             |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM?                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29                                                       |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM?                                                                                                                                                                                                                                                                                                                                                            | 22<br>22<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29                                                             |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM?                                                                                                                                                                                                                                                                                                                                       | 22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29                                                       |

| 5.2.1 Accessing memory locations with pointers 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing.                                                                                                                                                                                                                                                                                                               | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29<br>29                                                       |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM?                                                                                                                                                                                                                                                                                                                                       | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29<br>29                                                       |

| 5.2.1 Accessing memory locations with pointers 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing.                                                                                                                                                                                                                                                                                                               | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29                                           |

| 5.2.1 Accessing memory locations with pointers 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing.                                                                                                                                                                                                                                                                                     | 22<br>22<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29                                     |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack.                                                                                                                                                                                                 | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30                               |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack.                                                                                                                                                                                                                                | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30                               |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack.                                                                                                                                                                                                 | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>30<br>30<br>30<br>31                         |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack. 7.4.2 Use of the stack. 7.4.2 Use of the stack. 7.4.3 Common bugs with the stack operation.                                                                           | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>31<br>31                         |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack. 7.4.2 Use of the stack. 7.4.3 Common bugs with the stack operation.                                                                                                    | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>31<br>31<br>33                   |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port?. 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack. 7.4.2 Use of the stack. 7.4.2 Use of the stack. 7.4.3 Common bugs with the stack operation.                                                                           | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>31<br>31<br>33<br>33       |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3 How to use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack. 7.4.2 Use of the stack. 7.4.3 Common bugs with the stack operation. 8 Jumping and branching.                                                                           | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>31<br>31<br>31<br>33<br>33       |

| 5.2.1 Accessing memory locations with pointers. 5.2.2 Reading program flash memory with the Z pointer. 5.2.3 Tables in the program flash memory. 5.2.4 Accessing registers with pointers. 5.3 Recommendation for the use of registers. 6 Ports. 6.1 What is a Port? 6.2 Write access to ports. 6.3 Read access to ports. 6.4 Read-Modify-Write access to ports. 6.5 Memory mapped port access. 6.6 Details of relevant ports in the AVR. 6.7 The status register as the most used port. 6.8 Port details. 7 SRAM. 7.1 What is SRAM? 7.2 For what purposes can I use SRAM? 7.3.1 Direct addressing. 7.3.2 Pointer addressing. 7.3.2 Pointer addressing. 7.3.3 Pointer with offset. 7.4 Use of SRAM as stack. 7.4.1 Defining SRAM as stack. 7.4.2 Use of the stack 7.4.3 Common bugs with the stack operation. 8 Jumping and branching. 8.1 Controlling sequential execution of the program. 8.2 Linear program execution and branches. | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>31<br>31<br>31<br>33<br>33<br>33 |

|    | 8.6 Interrupts and program execution                            | 37 |

|----|-----------------------------------------------------------------|----|

|    | Calculations                                                    |    |

|    | 9.1 Number systems in assembler                                 | 39 |

|    | 9.1.1 Positive whole numbers (bytes, words, etc.)               |    |

|    | 9.1.2 Signed numbers (integers)                                 |    |

|    | 9.1.3 Binary Coded Digits, BCD                                  |    |

|    | 9.1.4 Packed BCDs.                                              |    |

|    | 9.1.5 Numbers in ASCII-format.                                  |    |

|    | 9.2 Bit manipulations.                                          |    |

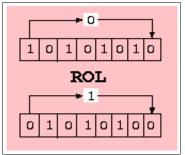

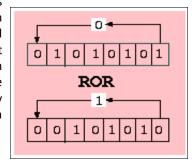

|    | 9.3 Shift and rotate                                            |    |

|    | 9.4 Adding, subtracting and comparing.                          |    |

|    |                                                                 |    |

|    | 9.4.1 Adding and subtracting 16-bit numbers.                    |    |

|    | 9.4.2 Comparing 16-bit numbers.                                 |    |

|    | 9.4.3 Comparing with constants                                  |    |

|    | 9.4.4 Packed BCD math                                           |    |

|    | 9.5 Format conversion for numbers.                              |    |

|    | 9.5.1 Conversion of packed BCDs to BCDs, ASCII or Binaries      |    |

|    | 9.5.2 Conversion of Binaries to BCD.                            |    |

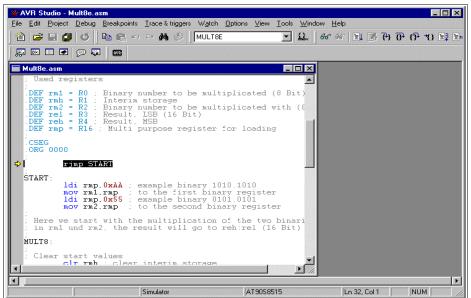

|    | 9.6 Multiplication                                              |    |

|    | 9.6.1 Decimal multiplication.                                   | 44 |

|    | 9.6.2 Binary multiplication                                     | 44 |

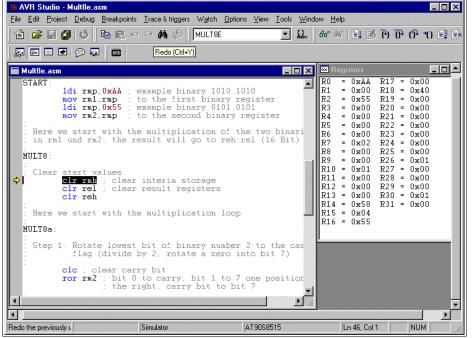

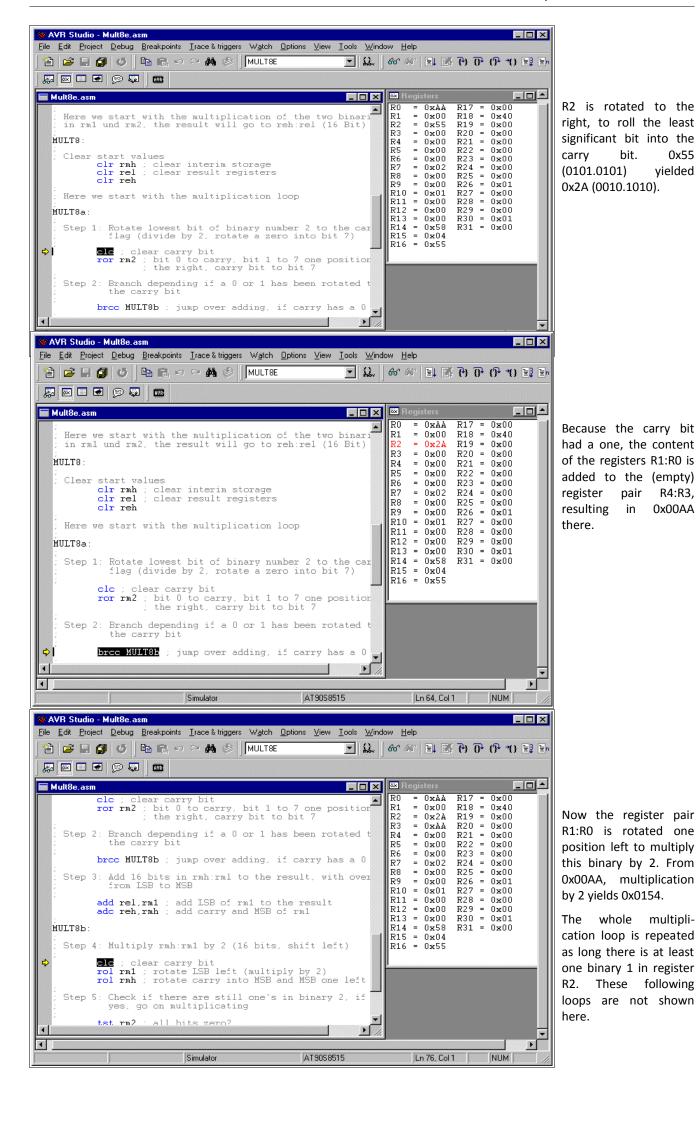

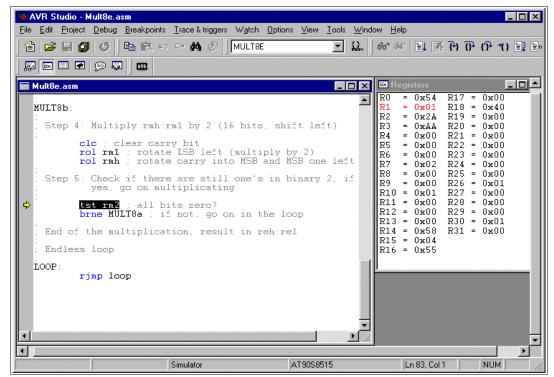

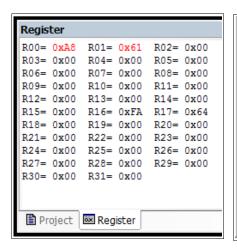

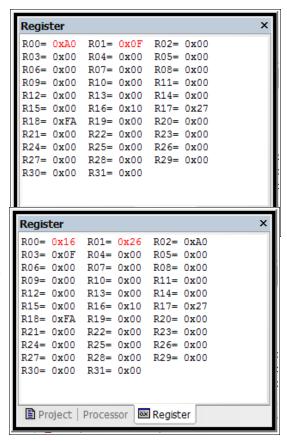

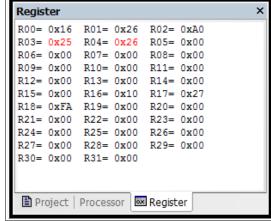

|    | 9.6.3 AVR assembler program                                     | 45 |

|    | 9.6.4 Binary rotation                                           | 46 |

|    | 9.6.5 Multiplication in the studio.                             | 46 |

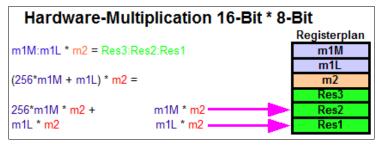

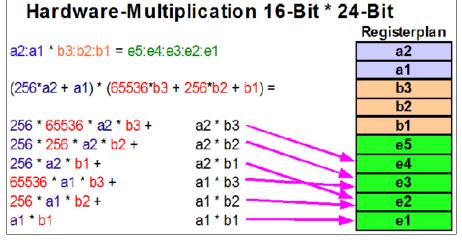

|    | 9.7 Hardware multiplication.                                    |    |

|    | 9.7.1 Hardware multiplication of 8-by-8-bit binaries.           |    |

|    | 9.7.2 Hardware multiplication of a 16- by an 8-bit-binary       |    |

|    | 9.7.3 Hardware multiplication of a 16- by a 16-bit-binary       |    |

|    | 9.7.4 Hardware multiplication of a 16- by a 24-bit-binary       |    |

|    | 9.8 Division                                                    |    |

|    | 9.8.1 Decimal division.                                         |    |

|    |                                                                 |    |

|    | 9.8.2 Binary division.                                          |    |

|    | 9.8.3 Program steps during division.                            |    |

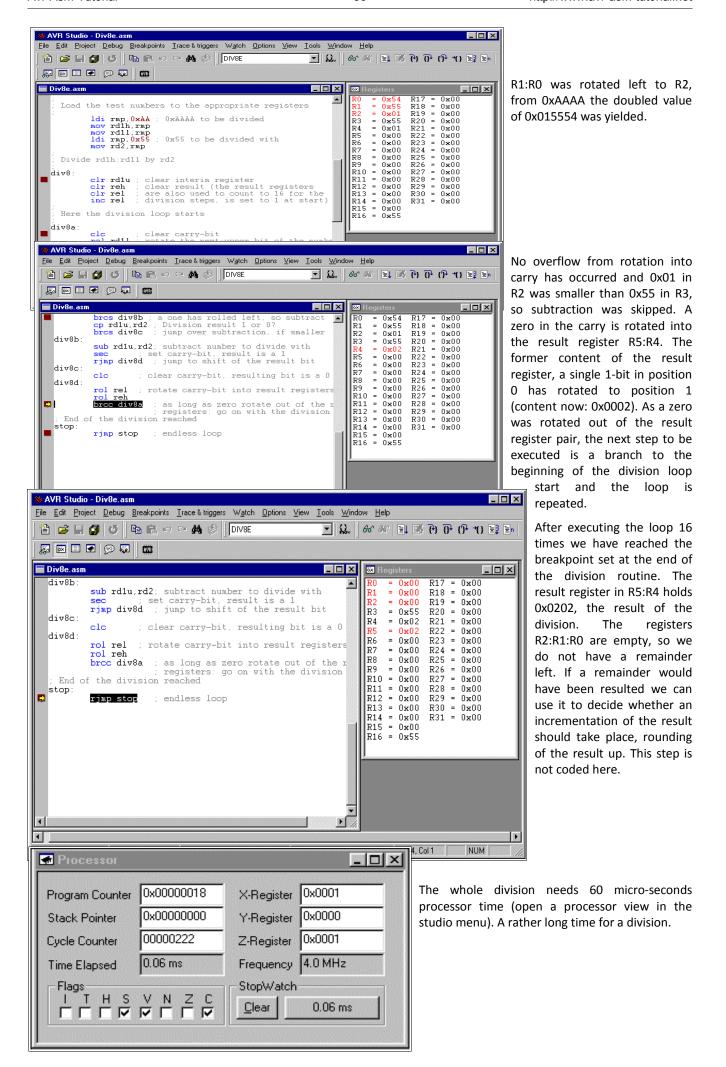

|    | 9.8.4 Division in the simulator                                 |    |

|    | 9.9 Number conversion.                                          |    |

|    | 9.10 Decimal Fractions                                          |    |

|    | 9.10.1 Linear conversions.                                      |    |

|    | 9.10.2 Example 1: 8-bit-AD-converter with fixed decimal output  |    |

|    | 9.10.3 Example 2: 10-bit-AD-converter with fixed decimal output |    |

| 10 | Project planning                                                | 60 |

|    | 10.1 How to plan an AVR project in assembler                    | 60 |

|    | 10.2 Hardware considerations                                    |    |

|    | 10.3 Considerations on interrupt operation                      |    |

|    | 10.3.1 Basic requirements of interrupt-driven operation         |    |

|    | 10.3.2 Example for an interrupt-driven assembler program        |    |

|    | 10.4 Considerations on timing.                                  | 63 |

| 11 | Annex                                                           |    |

|    | 11.1 Instructions sorted by function                            |    |

|    | 11.2 Directives and Instruction lists in alphabetic order       |    |

|    | 11.2.1 Assembler directives in alphabetic order                 |    |

|    | 11.2.1 Assembler directives in alphabetic order                 |    |

|    | ±                                                               |    |

|    | 11.3 Port details                                               |    |

|    | 11.3.1 Status-Register, Accumulator flags                       |    |

|    | 11.3.2 Stackpointer.                                            |    |

|    | 11.3.3 SRAM and External Interrupt control                      |    |

|    | 11.3.4 External Interrupt Control.                              | 70 |

|    | 11.3.5 Timer Interrupt Control.                                 |    |

|    | 11.3.6 Timer/Counter 0                                          |    |

|    | 11.3.7 Timer/Counter 1                                          |    |

|    | 11.3.8 Watchdog-Timer.                                          | 73 |

|    | 11.3.9 EEPROM                                                   |    |

|    | 11.3.10 Serial Peripheral Interface SPI                         | 74 |

|    | 11.3.11 UART                                                    |    |

|    |                                                                 |    |

| 11.3.12 Analog Comparator    | 75 |

|------------------------------|----|

| 11.3.13 I/O Ports            |    |

| 11.4 Ports, alphabetic order |    |

| 11.5 List of abbreviations.  |    |

# 1 Why learning Assembler?

Assembler or other languages, that is the question. Why should I learn another language, if I already learned other programming languages? The best argument: while you live in France you are able to get through by speaking English, but you will never feel at home then, and life remains complicated. You can get through with this, but it is rather inappropriate. If things need a hurry, you should use the country's language.

Many people that are deeper into programming AVRs and use higher-level languages in their daily work recommend that beginners start with learning assembly language. The reason is that sometimes, namely in the following cases:

- if bugs have to be analyzed,

- if the program executes different than designed and expected,

- if the higher-level language doesn't support the use of certain hardware features,

- if time-critical in line routines require assembly language portions,

it is necessary to understand assembly language, e. g. to understand what the higher-level language compiler produced. Without understanding assembly language you do not have a chance to proceed further in these cases.

#### Short and easy

Assembler instructions translate one by one to executed machine instructions. The processor needs only to execute what you want it to do and what is necessary to perform the task. No extra loops and unnecessary features blow up the generated code. If your program storage is short and limited and you have to optimize your program to fit into memory, assembler is choice 1. Shorter programs are easier to debug, every step makes sense.

#### Fast and quick

Because only necessary code steps are executed, assembly programs are as fast as possible. The duration of every step is known. Time critical applications, like time measurements without a hardware timer, that should perform excellent, must be written in assembler. If you have more time and don't mind if your chip remains 99% in a wait state type of operation, you can choose any language you want.

#### Assembler is easy to learn

It is not true that assembly language is more complicated or not as easy to understand than other languages. Learning assembly language for whatever hardware type brings you to understand the basic concepts of any other assembly language dialects. Adding other dialects later is easy. As some features are hardware-dependent optimal code requires some familiarity with the hardware concept and the dialect. What makes assembler sometimes look complicated is that it requires an understanding of the controller's hardware functions. Consider this an advantage: by learning assembly language you simultaneously learn more about the hardware. Higher level languages often do not allow you to use special hardware features and so hide these functions.

The first assembly code does not look very attractive, with every 100 additional lines programmed it looks better. Perfect programs require some thousand lines of code of exercise, and optimization requires lots of work. The first steps are hard in any language. After some weeks of programming you will laugh if you go through your first code. Some assembler instructions need some months of experience.

#### AVRs are ideal for learning assembler

Assembler programs are a little bit silly: the chip executes anything you tell it to do, and does not ask you if you are sure overwriting this and that. All protection features must be programmed by you, the chip does exactly anything like it is told, even if it doesn't make any sense. No window warns you, unless you programmed it before.

To correct typing errors is as easy or complicated as in any other language. Basic design errors, the more tricky type of errors, are also as complicated to debug like in any other computer language. But: testing programs on ATMEL chips is very easy. If it does not do what you expect it to do, you can easily add some diagnostic lines to the code, reprogram the chip and test it. Bye, bye to you EPROM programmers, to the UV lamps used to erase your test program, to you pins that don't fit into the socket after having them removed some dozen times.

Changes are now programmed fast, compiled in no time, and either simulated in the studio or checked in-circuit. No pin is removed, and no UV lamp gives up just in the moment when you had your excellent idea about that bug.

#### Test it!

Be patient doing your first steps! If you are familiar with another (high-level) language: forget it for the first time. Behind every assembler language there is a certain hardware concept. Most of the special features of other computer languages don't make any sense in assembler.

The first five instructions are not easy to learn, after that your learning speed rises fast. After you had your first lines: grab the instruction set list and lay back in the bathtub, wondering what all the other instructions are like.

Serious warning: Don't try to program a mega-machine to start with. This does not make sense in any computer language, and just produces frustration. Start with the small "Hello world"-like examples, e. g. turning some LEDs on and off for a certain time, then explore the hardware features a bit deeper.

Recommendation: Comment your subroutines and store them in a special directory, if debugged: you will need them again in a short time.

Have success!

# 2 The concept behind the language assembler in micro-controllers

Attention! These pages are on programming micro-controllers, not on PCs with Linux- or Windows operating systems and similar elephants, but on a small mice. It is not on programming Ethernet mega-machines, but on the question why a beginner should start with assembler and not with a complex high-level language.

This page shows the concept behind assembler, what those familiar with high-level languages have to give up to learn assembler and why assembler is not machine language.

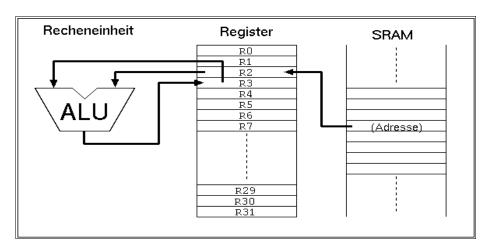

#### 2.1 The hardware of micro-controllers

What has the hardware to do with assembler? Much, as can be seen from the following.

The concept behind assembler is to make the hardware resources of the processor accessible. Resources means all hardware components, like

- \* the central processing unit (CPU) and its math servant, the arithmetic and logic unit (ALU),

- \* the diverse storage units (internal and external RAM, EEPROM storage),

- \* the ports that control characteristics of port-bits, timers, AD converters, and other devices.

Accessible means directly accessible and not via drivers or other interfaces, that an operating system provides. That means, you control the serial interface or the AD converter, not some other layer between you and the hardware. As award for your efforts, the complete hardware is at your command, not only the part that the compiler designer and the operating system programmer provides for you.

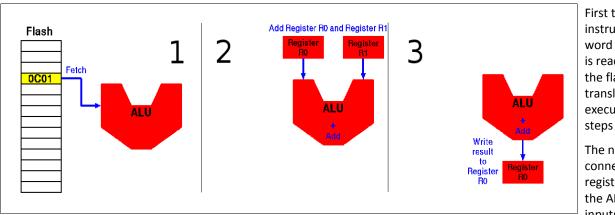

#### 2.2 How the CPU works