# Asynchronously Controlled Frequency Locked Loop

async techniques in a sync system

Suwen Yang, Frankie Y. Liu, Vincent C. Lee

May 9 2016

## The Big Picture

## The Big Picture

#### Applications and prior

#### Apps

- PLL : sep. phase and freq loops, or coarseness

- Dist power grid sync : small freq. variations

- Frequency synthesis : lower loop order

- Capacitance measurement : measure osc. freq

### Applications and prior

#### Prior

- Counters

- Sigma-delta noise shaping modulators

- Frequency-to-voltage conversion

- Second-order integrators

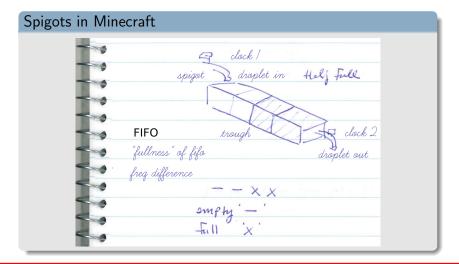

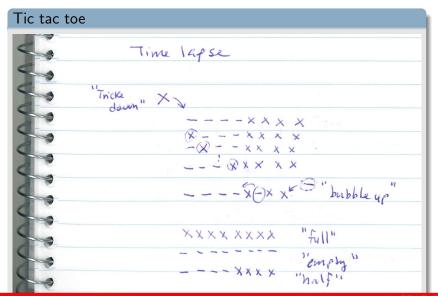

## Asynchronous FIFO for frequency detection

## Symbology

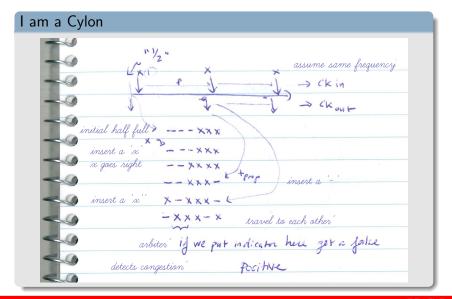

#### False positive

#### Clobber

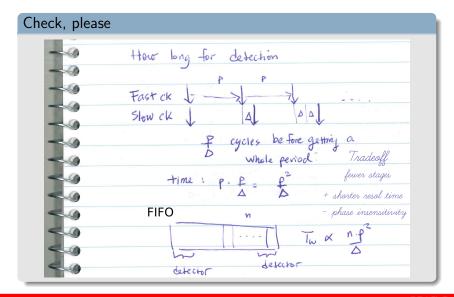

## How long before an update

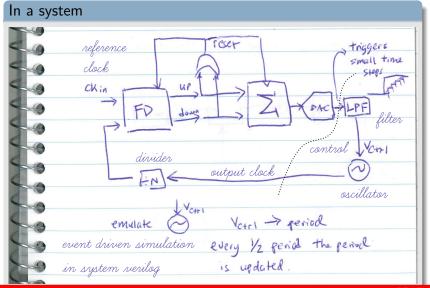

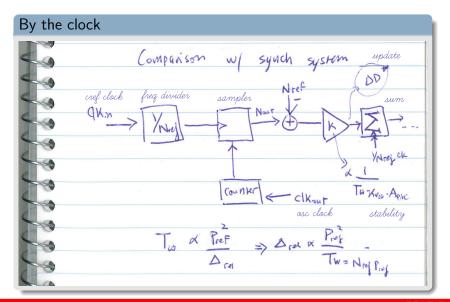

### FLL with the frequency detector

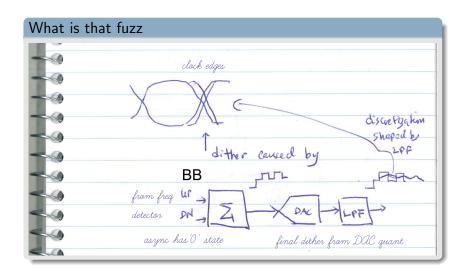

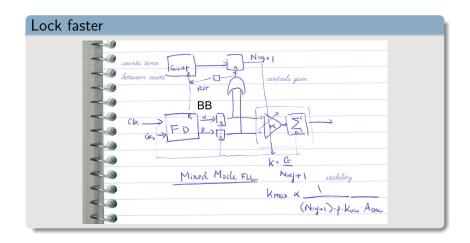

#### Dither

## Synchronous counting

#### Mixed Mode FLL

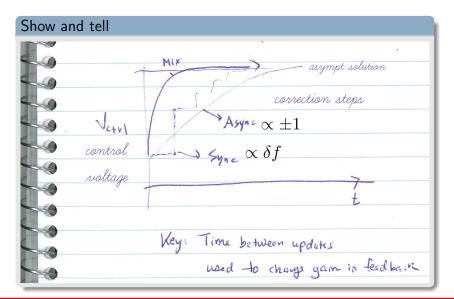

### Time traces for oscillator control voltage

ORACLE

#### **Ending**

#### There is no place like home

- Pro: simple design FLL, resolution not set by large number of bits, fixed "space" requirement

- Pro: not sensitive to phase offset between the two signals

- Pro: static jitter set by DAC quantization error

- Pro: fast locking via gear shifting, done in an asynchronous manner, goes with the flow

- Con: adoption of non time-synchronous solution

#### Safe Harbor Statement

The preceding is intended to outline our general product direct on. It is intended for informat on purposes only, and may not be incorporated into any contract. It is not a commitment to deliver any material, code, or funct onality, and should not be relied upon in making purchasing decisions. The development, release, and t ming of any features or funct onality described for Oracle's products remains at the sole discret on of Oracle.

## Questions?

Frankie Liu frankie liu@oracle.com

ORACLE