# **Detailed Instruction Repertoire of the MCS-4**

home

Intel 4004 Instructions Set

| Intel 4004 Instructions Set |          |                                     |          |                     |

|-----------------------------|----------|-------------------------------------|----------|---------------------|

| INSTRUCTION                 | MNEMONIC | BINARY EQUIVALENT 1st byte 2nd byte |          | MODIFIERS           |

| No Operation                | NOP      | 00000000                            | -        | none                |

| Jump Conditional            | JCN      | 0001CCCC                            | AAAAAAA  | condition, address  |

| Fetch Immediate             | FIM      | 0010RRR0                            |          | register pair, data |

| Send Register Control       | SRC      | 0010RRR1                            | -        | register pair       |

| Fetch Indirect              | FIN      | 0011RRR0                            | -        | register pair       |

| Jump Indirect               | JIN      | 0011RRR1                            | _        | register pair       |

| Jump Uncoditional           | JUN      | 0100AAAA                            | AAAAAAA  | address             |

| Jump to Subroutine          | JMS      | 0101AAAA                            | AAAAAAAA | 1                   |

| Increment                   | INC      | 0110RRRR                            | -        | register            |

| Increment and Skip          | ISZ      | 0111RRRR                            | AAAAAAA  | register, address   |

| Add                         | ADD      | 1000RRRR                            | -        | register            |

| Subtract                    | SUB      | 1001RRRR                            | -        | register            |

| Load                        | LD       | 1010RRRR                            | -        | register            |

| Exchange                    | ХСН      | 1011RRRR                            | -        | register            |

| Branch Back and Load        | BBL      | 1100DDDD                            | -        | data                |

| Load Immediate              | LDM      | 1101DDDD                            | _        | data                |

| Write Main Memory           | WRM      | 11100000                            | _        | none                |

| Write RAM Port              | WMP      | 11100001                            | -        | none                |

| Write ROM Port              | WRR      | 11100010                            | _        | none                |

| Write Status Char 0         | WR0      | 11100100                            | -        | none                |

| Write Status Char 1         | WR1      | 11100101                            | -        | none                |

| Write Status Char 2         | WR2      | 11100101                            | _        | none                |

| Write Status Char 3         | WR3      | 11100111                            | _        | none                |

| Subtract Main Memory        | SBM      | 11101000                            | -        | none                |

| Read Main Memory            | RDM      | 11101001                            | -        | none                |

| Read ROM Port               | RDR      | 11101010                            |          | none                |

| Add Main Memory             | ADM      | 11101011                            | -        | none                |

| Read Status Char 0          | RD0      | 11101110                            | -        | none                |

| Read Status Char 1          | RD1      | 11101101                            |          | none                |

| Read Status Char 2          | RD2      | 11101110                            | -        | none                |

| Read Status Char 3          | RD3      | 11101111                            | -        | none                |

| Clear Both                  | CLB      | 11110000                            | _        | none                |

| Clear Carry                 | CLC      | 11110001                            |          | none                |

| Increment Accumulator       | IAC      | 11110010                            | _        | none                |

| Complement Carry            | CMC      | 11110010                            | -        | none                |

| Complement                  | CMA      | 11110100                            | -        | none                |

| Rotate Left                 | RAL      | 11110101                            | -        | none                |

| Rotate Right                | RAR      | 111101110                           | -        | none                |

| Transfer Carry and Clear    | TCC      | 11110111                            | <u> </u> | none                |

| Decrement Accumulator       | DAC      | 11111000                            | -        | none                |

| Transfer Carry Subtract     | TCS      | 11111000                            | -        | none                |

| Set Carry                   | STC      | 11111001                            | -        | 1                   |

| Decimal Adjust Accumulator  | DAA      | 11111010                            | -        | none                |

|                             | KBP      | 111111011                           |          | none                |

| Keybord Process             |          |                                     | -        | none                |

| Designate Command Line      | DCL      | 11111101                            |          | none                |

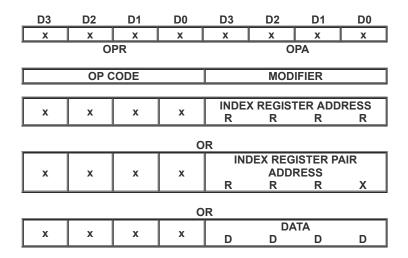

#### **Instuction Format**

The MCS-4 micro computer set has two types of instuction

- a) 1 word instruction with an 8-bit code and an execution time of 10.8 usec.

- b) 2 word instruction with an 16-bit code and an execution time of 21.6 usec.

Due to the time multiplexed operation of the system, the 8-bit instruction is fetched 4-bits at a time on two succesive clock periods.

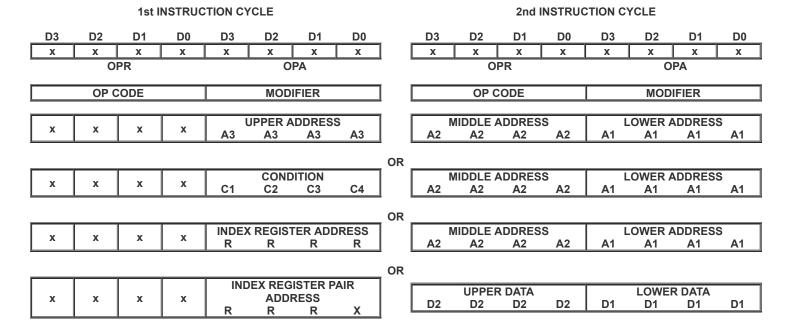

The instruction formats are illustrated in Tables I and II.

Table I

**ONE WORD INSTRUCTION**

Table II

#### TWO WORD INSTRUCTIONS

### **Symbols and Abbreviations**

The following Symbols and abbreviations will be used thorughout the next few sections:

() the content of --> is transferred to ACC Accumulator (4-bit) CY Carry/link Flip-Flop

ACBR Accumulator Buffer Register (4-bit)

RRRR Index register address

RRR Index register pair address

PL Low order program counter Field (4-bit)

PM Middle order program counter Field (4-bit)

PH High order program counter Field (4-bit)

ai Order i content of the accumulator

CMi Order i content of the command register

M RAM main character location

MSi RAM status character i

DB (T) Data bus content at time T

Stack The 3 registers in the address register other than the program counter

# Format for Describing Each Instruction

Each instruction will be described as follows:

(1) Mnemonic symbol and meaning

- (2) OPR and OPA code

- (3) Symbolic representation of the instruction

- (4) Description of the instruction (if necessary)

- (5) Example and/or exceptions (if necessary)

# **One Word Machine Instruction**

| Mnemonic:    | NOP (No Operation)     |

|--------------|------------------------|

| OPR OPA:     | 0000 0000              |

| Symbolic:    | Not applicable         |

| Description: | No operation performed |

| Mnemonic:    | LDM (Load data to Accumulator)                                                                                                                                                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1101 DDDD                                                                                                                                                                                 |

| Symbolic:    | DDDD> ACC                                                                                                                                                                                 |

| Description: | The 4 bits of data, DDDD stored in the OPA field of insruction word are loaded into the accumulator. The previous contents of the acummulator are lost. The carry/link bit is unaffected. |

| Mnemonic: | LD (Load index register to Accumulator)                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:  | 1010 RRRR                                                                                                                                                                                                               |

| Symbolic: | (RRRR)> ACC                                                                                                                                                                                                             |

| l '       | The 4 bit content of the designated index register (RRRR) is loaded into accumulator. The previous contents of the accumulator are lost. The 4 bit content of the index register and the carry/link bit are unaffected. |

| Mnemonic: | XCH (Exchange index register and accumulator)                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:  | 1011 DDDD                                                                                                                                                                                   |

| Symbolic: | (ACC)> ACBR, (RRRR)> ACC, (ACBR)> RRRR                                                                                                                                                      |

|           | The 4 bit content of designated index register is loaded into the accumulator. The prior content of the accumulator is loaded into the designed register. The carry/link bit is unaffected. |

| Mnemonic:    | ADD (Add index register to acc                                                                                                                                          | cumulator                                                                                                                   | with carry)                                     |                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|

| OPR OPA:     | 1000 RRRR                                                                                                                                                               |                                                                                                                             |                                                 |                                               |

| Symbolic:    | (RRRR) + (ACC) + (CY)> ACC                                                                                                                                              | C, CY                                                                                                                       |                                                 |                                               |

| Description: | The 4 bit content of the design the content of the accumulato in the accumulator. The carry/lthan 15 was generated to indicarry/link is set to 0. The 4 bit unaffected. | r with carr<br>ink is set<br>ate a carr                                                                                     | y. The result<br>to 1 if a sum<br>y out; other\ | is stored<br>greater<br>wise, the             |

| Example:     | Augend (ACC)   a3 a2 a1 a0   c0   +) r3 r2 r1 r0                                                                                                                        | <<br><sum< td=""><td>(CY)<br/> <br/> <br/> <br/> </td><td>Addend<br/>(RRRR)<br/> <br/> <br/> <br/> <br/> <br/> </td></sum<> | (CY)<br> <br> <br> <br>                         | Addend<br>(RRRR)<br> <br> <br> <br> <br> <br> |

|              | <br>     <br>(CY) (ACC)                                                                                                                                                 |                                                                                                                             |                                                 |                                               |

http://e4004.szyc.org/iset.html 3/10

| Total Control of the | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------|

| Mnemonic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SUB (Subtract index register from accu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ımulator w                                | vith borrow)                                      |

| OPR OPA:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1001 RRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                                                   |

| Symbolic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (ACC) + ~(RRRR) + (CY)> ACC, CY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                                   |

| Description:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The 4 bit content of the designated ind complemented (ones complement) and the accumulator with borrow and the reaccumulator. If a borrow is generated, otherwise, it is set to 1. The 4 bit conte is unaffected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l added to<br>esult is sto<br>the carry b | content of<br>ored in the<br>oit is set to 0;     |

| Example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Minuend (ACC)    a3 a2 a1 a0    c0 < +) \( \bar{r} \) \( \bar{r} \ | (CY)<br> <br> <br> <br>                   | Subtrahend<br>(RRRR)<br> <br> <br> <br> <br> <br> |

| Mnemonic:    | INC (Increment index register)                                                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 0110 RRRR                                                                                                                                                    |

| Symbolic:    | (RRRR) +1> RRRR                                                                                                                                              |

| Description: | The 4 bit content of the designated index register is incremented by 1. The index register is set to zero in case of overflow. The carry/link is unaffected. |

| Mnemonic:    | BBL (Branch back and load data to the accumulator)                                                                                                                                                                                                                                                                                   |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 0110 RRRR                                                                                                                                                                                                                                                                                                                            |

| Symbolic:    | (Stack)> PL, PM, PH; DDDD> ACC                                                                                                                                                                                                                                                                                                       |

| Description: | The program counter (address stack) is pushed down one level. Program control transfers to the next instruction following the last jump to subroutine (JMS) instruction. The 4 bits of data DDDD stored in the OPA portion of the instruction are loaded to the accumulator.  BBL is used to return from subroutine to main program. |

| Mnemonic: | JIN (Jump indirect)                                                                                                                                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:  | 0011 RRR1                                                                                                                                                                                                                                                                                                           |

| Symbolic: | (RRRO)> PM<br>(RRR1)> PL; PH unchanged                                                                                                                                                                                                                                                                              |

|           | The 8 bit content of the designated index register pair is loaded into the low order 8 positions of the program counter. Program control is transferred to the instruction at that address on the same page (same ROM) where the JIN instruction is located. The 8 bit content of the index register is unaffected. |

|           | When JIN is located at the address (PH) 1111 1111 program control is transferred to the next page in sequence and not to the same page where the JIN instruction is located. That is, the next address is (PH + 1) (RRRO) (RRR1) and not (PH) (RRRO) (RRR1)                                                         |

| Mnemonic:    | SRC (Send register control)                                                                                                                                                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 0010 RRR1                                                                                                                                                                                                                                                                                                             |

| Symbolic:    | (RRRO)> DB (X2)<br>(RRR1)> DB (X3)                                                                                                                                                                                                                                                                                    |

| Description: | The 8 bit content of the designated index register pair is sent to the RAM address register at X2 and X3. A subsequent read, write, or I/O operation of the RAM will utilize this address. Specifically, the first 2 bits of the address designatea RAM chip; the second 2 bits designate 1 out of 4 registers within |

the chip; the last 4 bits designate 1 out of 16 4-bit main memory characters within the register. This command is also used to designate a ROM for a subsequent ROM I/O port operation. The first 4 bits designate the ROM chip number to be selected. The address in ROM or RAM is not cleared until the next SRC instruction is executed. The 8 bit content of the index register is unaffected.

| Mnemonic:    | FIN (Fetch indirect from ROM)                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 0011 RRRO                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Symbolic:    | (PH) (0000) (0001)> ROM address<br>(OPR)> RRRO<br>(OPA)> RRR1                                                                                                                                                                                                                                                                                                                                                                                     |

| Description: | The 8 bit content of the 0 index register pair (0000) (0001) is sent out as an address in the same page where the FIN instruction is located. The 8 bit word at that location is loaded into the designated index register pair. The program counter is unaffected; after FIN has been executed the next instruction in sequence will be addressed. The content of the 0 index register pair is unaltered unless index register 0 was designated. |

|              | a) Although FIN is a 1-word instruction, its execution requires two memory cycles (21.6 psec).  b) When FIN is located at address (PH) 1111 1111 data will be fetched from the next page(ROM) in sequence and not from the same page(ROM) where the FIN instruction is located. That is, next address is (PH + 1) (0000) (0001) and not (PH) (0000) (0001).                                                                                       |

#### **Two Word Machine Instruction**

| Mnemonic:         | JUN (Jump unconditional)                                                                                                        |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1st word OPR OPA: | 0100 A3 A3 A3 A3                                                                                                                |

| 2nd word OPR OPA: | A2 A2 A2 A1 A1 A1 A1                                                                                                            |

| *                 | AI AI AI> PL,<br>A2 A2 A2> PM,<br>A3 A3 A3> PH                                                                                  |

|                   | Program control is unconditionally transferred to the instruction locater at the address A3 A3 A3 A3, A2 A2 A2 A2, AI AI AI AI. |

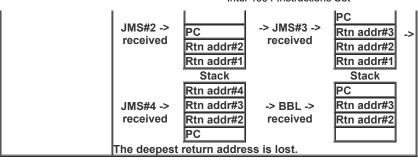

| Mnemonic:         | JMS (Jump to Subroutine)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1st word OPR OPA: | 0101 A3 A3 A3 A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2nd word OPR OPA: | A2 A2 A2 A1 A1 A1 A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbolic:         | AI AI AI> PL,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | A2 A2 A2 A2> PM,<br>A3 A3 A3 A3> PH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Description:      | The address of the next instruction in sequence following JMS (return address) is saved in the push down stack. Program control is transferred to the instruction located at the 12 bit address (A3A3A3A3A2A2A2A2A1A1A1A1). Execution of a return instruction (BBL) will cause the saved address to be pulled out of the stack, therefore, program control is transferred to the next sequential instruction after the last JMS.  The push down stack has 4 registers. One of them is used as the program counter, therefore nesting of JMS can occur up to 3 levels. |

| EXAMPLE:          | No JMS -> received PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mnemonic:         | JCN (Jump conditional)                                                                                                                                                                                                                                                                                                                                           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1st word OPR OPA: | 0001 C1C2C3C4                                                                                                                                                                                                                                                                                                                                                    |

| 2nd word OPR OPA: | A2 A2 A2 A1 A1 A1 A1                                                                                                                                                                                                                                                                                                                                             |

| Symbolic:         | If C1C2C3C4 is true, A2A2A2A2> PM                                                                                                                                                                                                                                                                                                                                |

|                   | A1A1A1A1> PL, PH unchanged                                                                                                                                                                                                                                                                                                                                       |

|                   | if C1C2C3C4 is false,                                                                                                                                                                                                                                                                                                                                            |

|                   | (PH)> PH, (PM)> PM, (PL + 2)> PL                                                                                                                                                                                                                                                                                                                                 |

| Description:      | If the designated condition code is true, program control is transferred to the instruction located at the 8 bit address A2A2A2A2, A1A1A1A1 on the same page (ROM) where JCN is located.  If the condition is not true the next instruction in sequence after JCN is executed.  The condition bits are assigned as follows:  C1 = 0 Do not invert jump condition |

|                   | C1 = 1 Invert jump condition                                                                                                                                                                                                                                                                                                                                     |

|                   | C2 = 1 Jump if the accumulator content is zero C3 = 1 Jump if the carry/link content is 1                                                                                                                                                                                                                                                                        |

|                   | C4 = 1 Jump if test signal (pin 10 on 4004) is zero.                                                                                                                                                                                                                                                                                                             |

| Example:          | OPR OPA                                                                                                                                                                                                                                                                                                                                                          |

| Lxample.          |                                                                                                                                                                                                                                                                                                                                                                  |

|                   | 0001 0110 Jump if accumulator is zero or carry = 1                                                                                                                                                                                                                                                                                                               |

|                   | Several conditions can be tested simutaneously.                                                                                                                                                                                                                                                                                                                  |

|                   | The logic equation describing the condition for a jump is give below:                                                                                                                                                                                                                                                                                            |

|                   | JUMP = ~C1 . ((ACC = 0) . C2 + (CY = 1) . C3 +<br>~TEST . C4) + C1 . ~((ACC = 0) . C2 +<br>(CY = 1) . C3 + ~TEST . C4)                                                                                                                                                                                                                                           |

| EXCEPTIONS:       | If JCN is located on words 254 and 255 of a ROM page, when JCN is executed and the condition is true, program control is transferred to the 8-bit address on the next page where JCN is located.                                                                                                                                                                 |

| Mnemonic:         | ISZ (Increment index register skip if zero)                                                                                                                                                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1st word OPR OPA: | 0111 RRRR                                                                                                                                                                                                                                                                                                                                                                             |

| 2nd word OPR OPA: | A2 A2 A2 A1 A1 A1 A1                                                                                                                                                                                                                                                                                                                                                                  |

| Symbolic:         | (RRRR) + 1> RRRR, if result = 0<br>(PH)> PH, (PM)> PM, (PL + 2)> PL:<br>if result <> 0 (PH)> PH,<br>A2A2A2A2> PM, A1A1A1A1> PL                                                                                                                                                                                                                                                        |

|                   | The content of the designated index register is incremented by 1. The accumulator and carry/link are unaffected. If the result is zero, the next instruction after ISZ is executed. If the result is different from 0, program control is transferred to the instruction located at the 8 bit address A2A2A2A2, A1A1A1A1 on the same page (ROM) where the ISZ instruction is located. |

| EXCEPTIONS:       | If ISZ is located on words 254 and 255 of a ROM page, when ISZ is executed and the result is not zero, program control is transferred to the 8-bit address located on the next page in sequence and not on the same page where ISZ is located.                                                                                                                                        |

| Mnemonic:         | FIM (Fetched immediate from ROM) |

|-------------------|----------------------------------|

| 1st word OPR OPA: | 0010 RRR0                        |

|                   |                                  |

| 2nd word OPR OPA: D2 D2 D2 D1 D1 D1 D1 |                                                                                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------------|

| Symbolic:                              | D2D2D2D2> RRR0, D1D1D1D1> RRR1                                                                   |

| Description:                           | The 2nd word represents 8-bits of data which are loaded into the designated index register pair. |

Input/Output and RAM Instructions

(The RAM's and ROM's operated on in the I/O and RAM instructions have been previously selected by the last SRC instruction executed.)

| Mnemonic:    | RDM (Read RAM character)                                                                                                                                                 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 1001                                                                                                                                                                |

| Symbolic:    | (M)> ACC                                                                                                                                                                 |

| Description: | The content of the previously selected RAM main memory character is transferred to the accumulator. The carry/linkis unaffected. The 4-bit data in memory is unaffected. |

| Mnemonic:    | RD0 (Read RAM status character 0)                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 1100                                                                                                                                                             |

| Symbolic:    | (MS0)> ACC                                                                                                                                                            |

| Description: | The 4-bits of status character 0 for the previously selected RAM register are transferred to the accumulator. The carry/link and the status character are unaffected. |

| Mnemonic: | RD1 (Read RAM status character 1) |

|-----------|-----------------------------------|

| OPR OPA:  | 1110 1101                         |

| Symbolic: | (MS1)> ACC                        |

| Mnemonic: | RD2 (Read RAM status character 2) |

|-----------|-----------------------------------|

| OPR OPA:  | 1110 1110                         |

| Symbolic: | (MS2)> ACC                        |

| Mnemonic: | RD3 (Read RAM status character 3) |

|-----------|-----------------------------------|

| OPR OPA:  | 1110 1111                         |

| Symbolic: | (MS0)> ACC                        |

| Mnemonic:    | RDR (Read ROM port)                                                                                                                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 1010                                                                                                                                                                                                                                                                                                                                                                  |

| Symbolic:    | (ROM input lines)> ACC                                                                                                                                                                                                                                                                                                                                                     |

| Description: | The data present at the input lines of the previously selected ROM chip is transferred to the accumulator. The carry/link is unaffected. If the I/O option has both inputs and outputs within the same 4 I/O lines, the user can choose to have either "0" or "1" transferred to the accumulator for those I/O pins coded as outputs, when an RDR instruction is executed. |

| EXAMPLE:     | Given a 4001 with I/O coded with 2 inputs and 2 outputs, when RDR is executed the transfer is as shown below:  I3 O2 O1 I0 (ACC)  1 X X 0 1> 1 (1 or 0) (1 or 0) 0  Input Data User can choose                                                                                                                                                                             |

| Mnemonic: | WRM (Write accumulator into RAM character)                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:  | 1110 0000                                                                                                                                          |

| Symbolic: | (ACC)> M                                                                                                                                           |

| l '       | The accumulator content is written into the previously selected RAM main memory character location. The accumulator and carry/link are unaffected. |

| Mnemonic: | WRO (Write accumulator into RAM status character 0) |

|-----------|-----------------------------------------------------|

| OPR OPA:  | 1110 0100                                           |

| Symbolic: | (ACC)> MS0                                          |

|           |                                                     |

| Description: | The content of the accumulator is written into the RAM status |

|--------------|---------------------------------------------------------------|

|              | character 0 of the previously selected RAM register. The      |

|              | accumulator and the carry/link are unaffected.                |

| Mnemonic: | WR1 (Write accumulator into RAM status character 1) |

|-----------|-----------------------------------------------------|

| OPR OPA:  | 1110 0101                                           |

| Symbolic: | (ACC)> MS1                                          |

| Mnemonic: | WR2 (Write accumulator into RAM status character 2) |

|-----------|-----------------------------------------------------|

| OPR OPA:  | 1110 0110                                           |

| Symbolic: | (ACC)> MS2                                          |

| Mnemonic: | WR3 (Write accumulator into RAM status character 3) |

|-----------|-----------------------------------------------------|

| OPR OPA:  | 1110 0111                                           |

| Symbolic: | (ACC)> MS3                                          |

| Mnemonic:    | WRR (Write ROM port)                                                                                                                                                                                                                                                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 0010                                                                                                                                                                                                                                                                                                                                                                      |

| Symbolic:    | (ACC)> ROM output lines                                                                                                                                                                                                                                                                                                                                                        |

| Description: | The content of the accumulator is transferred to the ROM output port of the previously selected ROM chip. The data is available on the output pins until a new WRR is executed on the same chip. The ACC content and carry/link are unaffected. (The LSB bit of the accumulator appears on I/O0, pin 16, of the 4001). No operation is performed on I/O lines coded as inputs. |

| Mnemonic: | WMP (Write memory port)                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:  | 1110 0001                                                                                                                                                                                                                                                                                                                          |

| Symbolic: | (ACC)> RAM output register                                                                                                                                                                                                                                                                                                         |

| ·         | The content of the accumulator is transferred to the RAM output port of the previously selected RAM chip. The data is available on the output pins until a new WMP is executed on the same RAM chip. The content of the ACC and the carry/link are unaffected. (The LSB bit of the accumultor appears on O0, Pin 16, of the 4002.) |

| Mnemonic:    | ADM (Add from memory with carry)                                                                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 1011                                                                                                                                 |

| Symbolic:    | (M) + (ACC) + (CY)> ACC, CY                                                                                                               |

| Description: | The content of the previously selected RAM main memory character is added to the accumulator with carry. The RAM character is unaffected. |

| Mnemonic:    | SBM (Subtract from memory with borrow)                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| OPR OPA:     | 1110 1000                                                                                                                            |

| Symbolic:    | ~(M) + (ACC) + ~(CY)> ACC, CY                                                                                                        |

| Description: | Thecontent of the previously selected RAM character is subtracted from the accumulator with borrow. The RAM character is unaffected. |

# **Accumulator Group Instructions**

| Mnemonic:    | CLB (Clear both)                     |

|--------------|--------------------------------------|

| OPR OPA:     | 1111 0000                            |

| Symbolic:    | 0> ACC, 0> CY                        |

| Description: | Set accumulator and carry/link to 0. |

| Mnemonic: | CLC (Clear carry) |

|-----------|-------------------|

| OPR OPA:  | 1111 0001         |

| Symbolic: | 0> CY             |

Description: Set carry/link to 0.

| Mnemonic:    | CMC (Complement carry)                  |

|--------------|-----------------------------------------|

| OPR OPA:     | 1111 0011                               |

| Symbolic:    | ~(CY)> CY                               |

| Description: | The carry/link content is complemented. |

| Mnemonic:    | STC (Set carry)       |

|--------------|-----------------------|

| OPR OPA:     | 1111 1010             |

| Symbolic:    | 1> CY                 |

| Description: | Set carry/link to a 1 |

| Mnemonic:    | CMA (Complement Accumulator)                                                  |

|--------------|-------------------------------------------------------------------------------|

| OPR OPA:     | 1111 0100                                                                     |

| Symbolic:    | ~a3 ~a2 ~a1 ~a0> ACC                                                          |

| Description: | The content of the accumulator is complemented. The carry/link is unaffected. |