# **M6800**

# **Assembly Language Programming**

# 3. MC6802 MICROPROCESSOR

MC6802 microprocessor runs in 1MHz clock cycle. It has 64 Kbyte memory address capacity using 16-bit addressing path (A0-A15). The 8-bit data path (D0-D7) is bidirectional and has three states. It has 72 instructions which are 1, 2 or 3 byte instructions.

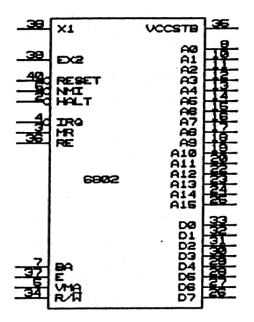

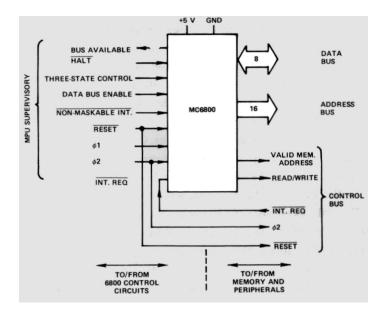

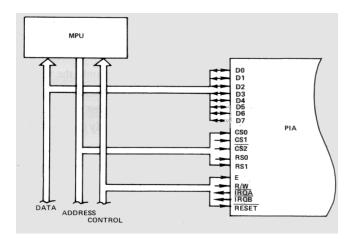

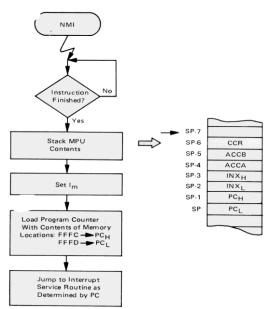

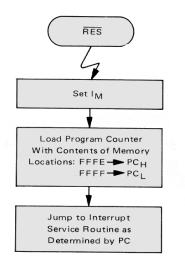

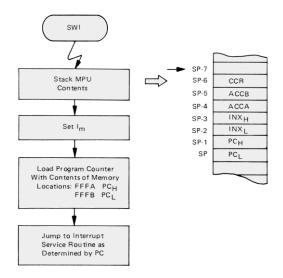

MC6802 microprocessor has 3 interrupt inputs. One of them is maskable (IRQ), the other one is unmaskable (NMI) and the last one is the reset (RESET). It also has 2 special instructions: SWI (software interrupt) and WAI (wait for interrupt). MC6802's pin numbers and their connections are shown in Figure 3.1.

Figure 3.1 - MC6082 Microprocessor

# 3.1 REGISTERS

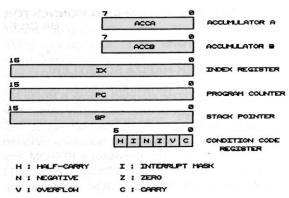

MC6802 Microprocessor has three 16-bit registers and three 8-bit registers available for use by the programmer (Figure 3.2).

- 2 Accumulators (Accumulator A, Accumulator B)

- Program Counter (PC)

- Stack Pointer (SP)

- Index Register (X)

- Condition Code Register (CCR).

Figure 3.2 - Registers of the MC6802 Microrprocessor

Accumulators: The Microprocessor unit (MPU) contains two 8-bit accumulators (Accumulator A and Accumulator B) that are used to hold operands and/or result produced by the arithmetic logic unit (ALU).

**Program Counter:** It is a 2-byte (16-bit) register that points to the current program address.

**Stack Pointer:** It is a 2-byte register that contains the address of the next available location in an external push-down/pop–up stack. The contents of the stack pointer defines the top of the stack in RAM.

**Index Register:** It is a 2-byte register that is used to store data or a 2-byte memory address for indexed memory addressing.

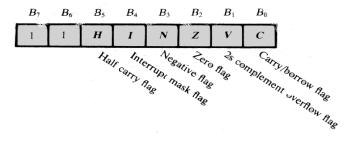

**Condition Code Register:** It shows the conditions occurs as a result of an Arithmetic Logic Unit operation (Figure 3.2):

- Bit 0: carry from bit 7 of an arithmetic operation (C)

- Bit 1: Overflow flag (V)

- Bit 2: Zero flag (Z)

- Bit 3: Negative flag (N)

- Bit 4: Interrupt Mask (I)

- Bit 5: Half carry from bit 3 of an arithmetic operation (H)

- Bit 6: Unused

- Bit 7: Unused

These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 of the CCR is the interrupt mask bit (I). The unused bits of the Condition Code Register (bit 6 and bit 7) are 1.

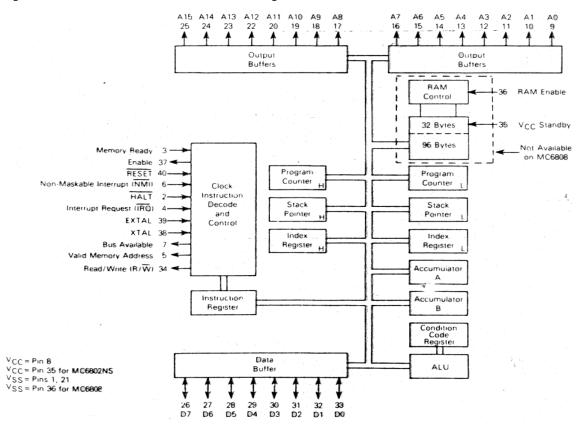

Figure 3.3 shows the internal connections of the registers and the other units of the MC6802.

Figure 3.3 - Functional block diagram of 6802 MPU

# 3.2 ADDRESSING MODES

MC6802 Microprocessor has 7 addressing modes that can be used by the programmer:

- 1. Accumulator

- 2. Immediate

- 3. Direct

- 4. Extended

- 5. Indexed

- 6. Implied (Inherent)

- 7. Relative

MC6802 instructions may be used with one or more of these addressing modes. The instruction set and their addressing modes are given in Appendix A.

## Accumulator Addressing

In accumulator addressing, either accumulator A or accumulator B is specified. These are 1-byte instructions.

Ex: ABA adds the contetns of accumulators and stores the result in accumulator A

## Immediate Addressing

In immediate addressing, operand is located immediately after the opcode in the second byte of the instruction in program memory (except LDS and LDX where the operand is in the second and third bytes of the instruction). These are 2-byte or 3-byte instructions.

Ex: LDAA #25H loads the number (25)<sub>H</sub> into accumulator A

## Direct Addressing

In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes of the memory, i.e, locations 0 through 255. Enhanced execution times are achieved by storing data in these locations. These are 2-byte instructions.

Ex: LDAA 25H loads the contents of the memory address (25)<sub>H</sub> into accumulator A

## Extended Addressing

In extended addressing, the address contained in the second byte of the instruction is used as the higher eight bits of the address of the operand. The third byte of the instruction is used as the lower eight bits of the address for the operand. This is an absolute address in the memory. These are 3-byte instructions.

Ex: LDAA 1000H loads the contents of the memory address  $(1000)_{H}$  into accumulator A

#### Indexed Addressing

In indexed addressing, the address contained in the second byte of the instruction is added to the index register's lowest eight bits. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are 2-byte instructions.

#### Ex: LDX #1000H LDAA 10H,X

Initially, LDX #1000H instruction loads 1000H to the index register (X) using immediate addressing. Then LDAA 10H,X instruction, using indexed addressing, loads the contents of memory address  $(10)_{H} + X = 1010_{H}$  into accumulator A.

## Implied (Inherent) Addressing

In the implied addressing mode, the instruction gives the address inherently (i.e, stack pointer, index register, etc.). Inherent instructions are used when no operands need to be fetched. These are 1-byte instructions.

Ex: INX increases the contents of the Index register by one. The address information is "inherent" in the instruction itself.

**INCA** increases the contents of the accumulator A by one. **DECB** decreases the contents of the accumulator B by one.

## **Relative Addressing**

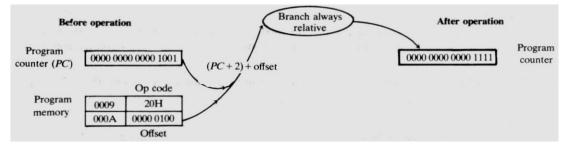

The relative addressing mode is used with most of the branching instructions on the 6802 microprocessor. The first byte of the instruction is the opcode. The second byte of the instruction is called the *offset*. The offset is interpreted as a *signed 7-bit number*. If the MSB (most significant bit) of the offset is 0, the number is positive, which indicates a forward branch. If the MSB of the offset is 1, the number is negative, which indicates a backward branch. This allows the user to address data in a range of -126 to +129 bytes of the present instruction. These are 2-byte instructions.

| Ex: | PC   | Hex Label | Instru | ction |

|-----|------|-----------|--------|-------|

|     | 0009 | 2004      | BRA    | 0FH   |

Figure 3.4 shows the address calculation in the execution of the unconditional branch instruction (BRA). Program counter (PC) before the operation is  $0009_{\rm H}$ . The opcode of the "branch always" instruction ( $20_{\rm H}$ ) is fetched from location  $0009_{\rm H}$  in program memory with the offset  $04_{\rm H}$  ( $00000100_2$ ). Then the program counter is incremented to the address of the next instruction ( $000B_{\rm H}$ ) just before the actual operand fetch. The 6802 processor internally adds the offset ( $04_{\rm H}$ ) to the current contents of program counter ( $000B_{\rm H}$ ). The new address in the program counter after the "branch always" operation is  $000B+04=000F_{\rm H}$  ( $0000\ 0000\ 0000\ 1111_2$ ). The processor then jumps to this new address and fetches an instruction from location  $000F_{\rm H}$ . Note that the offset's most significant bit (MSB) is 0. This indicates a positive offset, which causes a forward branch.

Figure 3.4 - Relative Addressing (branching forward)

All branch operations use relative addressing mode. Branches can be forward or backward. The program in Figure 3.5 is an example for the use of branch instructions. In the first branch instruction (BRA NEXT), the address to be branched is  $109_{\rm H}$ . As relative addressing is used, the offset is calculated as

$$109_{\rm H} - 105_{\rm H} = 04_{\rm H}$$

where  $105_{\rm H}$  is the contents of PC which points to the next instruction. The offset is written in the machine code program as the operand of the branch instruction (20 04<sub>H</sub>). The second branch instruction (BRA LAST) is a backward branch. The displacement (offset) is calculated as

$$105_{\rm H} - 10E_{\rm H} = -09_{\rm H}$$

where  $10E_H$  is the contents of PC. As the offset is a negative number, its 2's complement (F7<sub>H</sub>) is used as the offset (20 F7<sub>H</sub>).

| Memory  | Machine Code | Assembly Language Program |      | PC after instruction execution |      |

|---------|--------------|---------------------------|------|--------------------------------|------|

| Address | Program      |                           |      |                                |      |

|         |              |                           | ORG  | 100H                           |      |

| 0100    | B6 0110      | BEGIN:                    | LDAA | 110H                           | 0103 |

| 0103    | 20 04        |                           | BRA  | NEXT                           | 0109 |

| 0105    | B7 0130      | LAST:                     | STAA | 130H                           | 0108 |

| 0108    | 3F           |                           | SWI  |                                | -    |

| 0109    | BB 0120      | NEXT:                     | ADDA | 120H                           | 010C |

| 010C    | 20 F7        |                           | BRA  | LAST                           | 0105 |

Figure 3.5 - A program using branch instruction

## 4. 6802 ASSEMBLY LANGUAGE PROGRAMMING I

## 4.1 Flags

The 6802 MPU uses six condition code bits or flags (Figure 4.1). These flags are grouped into an 8-bit register called the Condition Code Register (CCR). The branch instructions test these flags to determine whether a branch will be taken or not.

As on the generic, the carry flag (C) is set to 1 whenever a carry (or 'borrow') is generated out by the most significant bit (MSB) of the accumulator. A sum larger than the capacity of the 8-bit accumulator sets the C flag to 1.

The overflow flag (V) in the condition code register of the MPU indicates a 2's complement overflow. When dealing with signed numbers, the MSB ( $B_7$ ) of accumulator(s) is the sign bit. The remaining 7 bits are written in 2's complement form. These 7 bits can hold numbers between decimal +127 to -128. This is the range of signed numbers. If the result of an arithmetic operation exceeds this range, an overflow occurs and the overflow flag (V) is set to 1.

Figure 4.1 - Condition Code Register

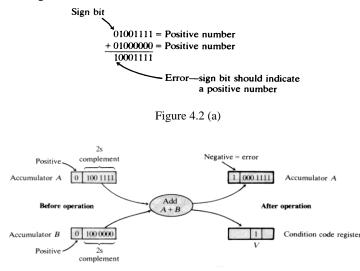

Consider adding the positive numbers  $79_{10}$  and  $64_{10}$ . Decimal +79 is 01001111 in 2's complement and decimal +64 is 01000000 in 2's complement. These 2's complement numbers are added in Figure 4.2(a). Due to the carry from B<sub>6</sub> to B<sub>7</sub>, the sign bit of the result changes to 1, (which indicates a negative number). This is an error. Figure 4.2(b) shows how the overflow flag is set in the microprocessor if two such numbers ( in accumulator A and B) are added. The sum (10001111 in this example) is deposited in accumulator A after add operation. The overflow flag (V) is set to 1, indicating that the sum is larger than +127<sub>10</sub> (sum= $79_{10}+64_{10}=143_{10}$ ).

Figure 4.2 (b)

Figure 4.2 - Addition of positive numbers using 2's complement and CCR(a) 2's complement addition showing effect on sign bit(b) Effect on overflow flag

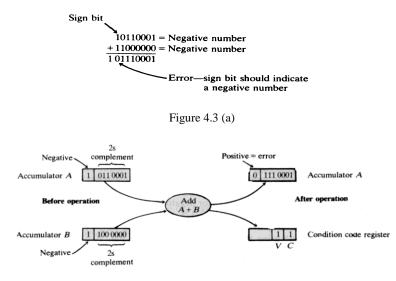

Consider adding two negative numbers  $-79_{10}$  and  $-64_{10}$ . Decimal -79 is 10110001 in 2's complement and decimal -64 is 11000000 in 2's complement. Since the most significant bits of both 2's complement numbers are 1 they represent negative numbers between -1 and -128. These 2's complement numbers are added in Figure 4.3(a). The result is 1 01110001. Although the sign bit must be 1 (negative), the addition results with a 0. This is an error because the sum exceeds the limit  $-128_{10}$ .

Addition of the negative numbers  $-79_{10}$  (10110001 in 2's complement) and  $-64_{10}$  (11000000 in 2's complement) using the 6802 MPU is shown in Figure 4.3(b). The 2's complement numbers are held in the accumulators A and B, and the sum is stored in accumulator A after the add operation. As the addition causes an overflow, the overflow flag (V) is set to 1, warning the user that the range of the 6802 microprocessor register is exceeded. The carry flag (C) is also set to 1, indicating the carry out from the B<sub>7</sub> position.

Figure 4.3(b)

Figure 4.3 - Addition of negative numbers using 2's complement and CCR (a) 2's complement addition showing the effect on sign bit (b) Effect on overflow flag

The zero flag (Z) in the condition code register of the 6802 MPU is set to 1 whenever the accumulator becomes zero as a result of an operation or data transfer. The zero flag resets to 0, indicating the accumulator does not contain a zero.

The negative flag (N) in the condition code register of the 6802 MPU indicates a negative result. Assume  $B_7$  is the sign bit of the accumulator. If the result of the last arithmetic, logical or data transfer operation is negative, the N flag is set to 1. If the result is positive, the N flag is resets to 0. The N flag reflects the MSB of the accumulator.

**Ex:** The following program adds two 1-byte signed numbers in memory locations  $(0120)_{\rm H}$  and  $(0121)_{\rm H}$ . After the addition, if the overflow flag is set, then  $10_{10}$  is stored into location  $(0040)_{\rm H}$ . Otherwise  $20_{10}$  is stored into the same location.

|        | ORG  | 0H    |                                                |

|--------|------|-------|------------------------------------------------|

|        | LDAA | 120H  | ; load the first number                        |

|        | ADDA | 121H  | ; add them                                     |

|        | BVS  | OVOCC | ; branch if overflow is set                    |

|        | LDAA | #20   | ; load $(10)_{10}$ to accumulator A            |

|        | STAA | 40H   | ; store it in memory location $(0040)_{\rm H}$ |

|        | BRA  | STOP  | ; jump to the end of the program               |

| OVOCC: | LDAA | #10   |                                                |

|        | STAA | 40H   |                                                |

| STOP:  | SWI  |       | ; end program                                  |

**Ex:** The following program adds two 1-byte unsigned numbers in memory locations  $(0120)_H$  and  $(0121)_H$  and stores the result, represented as a 2-byte number, into two consecutive memory locations  $(0122)_H$  and  $(0123)_H$ . After the addition operation accumulator A is stored at into address  $(0123)_H$ . If there is no carry, 0 is stored into the location  $(0122)_H$ . Otherwise carry flag is stored into  $(0122)_H$  (using ADC 122H and STAA 122H instructions).

|        | ORG  | 100H  |                                   |

|--------|------|-------|-----------------------------------|

|        | LDAA | #0H   | ; Clear the most significant bit  |

|        | STAA | 122H  |                                   |

|        | LDAA | 120H  | ; load the first number           |

|        | ADDA | 121H  | ; add them                        |

|        | STAA | 123H  | ; store result                    |

|        | BCS  | CROCC | ; branch if carry occurs          |

|        | LDAA | #0H   | ; clear the most significant bit  |

|        | STAA | 122H  |                                   |

|        | BRA  | STOP  | ; jump to the end of the program  |

| CROCC: | LDAA | #0H   | ; set accumulator to 0            |

|        | ADCA | 122H  | ; save carry bit in accumulator A |

|        | STAA | 122H  | -                                 |

| STOP:  | SWI  |       | ; end program                     |

# 4.2 Looping

Loops help to repeat a section of a program for a number of times. There are three main types of loops :

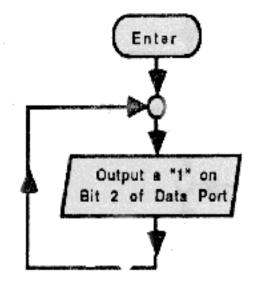

1. Repeating a program section indefinitely

Figure 4.1 - Infinite Loop. Above code outputs a "1" on bit 2 of a data port indefinitely.

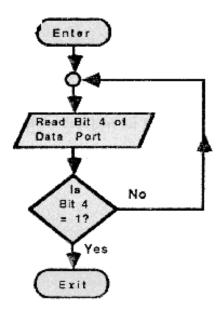

2. Repeating a program section until some predetermined condition becomes true (Figure 4.2)

Figure 4.2 - Conditional loop. The loop is repeated until a "1" appears at input bit 4 of the data port

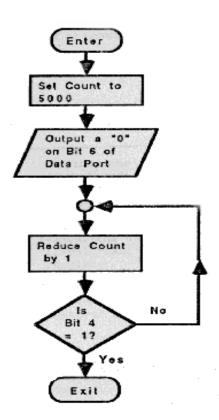

3. Repeating a program section for a predetermined number of passes.

Figure 4.3 - Loop with a loop count. Above code outputs a "0" on bit 6 of a data port 5000 times

For looping in assembly language programs, branch instructions are needed. Jump and branch instructions of the 6802 microprocessor are shown in Table A.2. These instructions transfer the control from one point to another in the program.

**Ex:** In the following program, accumulator A is incremented by 2 during each iteration of the loop. Accumulator B is used as a counter and decremented by 1 at each iteration, until it reduces to 0.

|             | ORG          | 100H         |                                                                               |

|-------------|--------------|--------------|-------------------------------------------------------------------------------|

|             | LDAA<br>LDAB | #00H<br>#10H | ; load $(00)_{\rm H}$ to accumulator A ; load $(10)_{\rm H}$ to accumulator B |

| COMPARISON: | BEQ          | STOP         | ; exit from the loop if accumulator B is 0                                    |

|             | ADDA         | #2H          | ; increment accumulator A by 2                                                |

|             | DECB         |              | ; decrement counter                                                           |

|             | BRA          | COMPARISON   | ; branch to the beginning of the loop                                         |

| STOP:       | STAA         | 150H         | ; store the number in accumulator A                                           |

|             | SWI          |              | ; end program                                                                 |

**Ex:** The index register is often used when the program must deal with data in the form of a table. The assembly language program listed in Figure 4.8(a) adds numbers from tables of the augends and addends in Figure 4.8(b) and places the sum in the table of sums to the bottom of this memory map. For instance, the program first adds  $01_{\rm H} + 02_{\rm H}$ , placing the sum  $03_{\rm H}$  in the "table of sums" to the memory location 0040H. Then it repeats this process by adding  $03_{\rm H} + 04_{\rm H}$ , placing the sum of  $07_{\rm H}$  in the "table of sums" to the memory location 0041<sub>H</sub>, etc. The program in Figure 4.6(a) also has a feature that supports the termination of the program if the sum of the numbers exceeds FF<sub>H</sub> (using BCS instruction).

|       |          | -       | <b>-</b>                             |

|-------|----------|---------|--------------------------------------|

| Label | Mnemonic | Operand | Comments                             |

|       | LDX      | #0020H  | ; Initialize index register at 0020H |

| LOOP  | LDAA     | 00H,X   | ; Load augend from first table in    |

|       |          |         | memory ( X + offset of 00H ) into    |

|       |          |         | accumulator A                        |

|       | ADDA     | 10H,X   | ; Add addend from second table       |

|       |          |         | in memory ( X + offset of 10H )      |

|       |          |         | into accumulator A                   |

|       | BCS      | STOP    | If C flag = 1, then branch forward   |

|       |          |         | to STOP ( end program if any sum     |

|       |          |         | is greater than FFH )                |

|       | STAA     | 20H,X   | ; Store accumulator A ( sum ) in     |

|       |          |         | third table in memory ( X + offset   |

|       |          |         | 20H )                                |

|       | INX      |         | ; Increment contents of index reg.   |

|       | CPX      | #0025   | ;Compare index register with 0025H   |

|       |          |         | (subtract 0025H from contents of     |

|       |          |         | index register)                      |

|       | BNE      | LOOP    | ; If Z flag = 0, then branch back to |

|       |          |         | symbolic address called LOOP         |

| STOP  | SWI      |         | ; End program                        |

# Program memory

| Address | Contents |          |

|---------|----------|----------|

| (hex)   | (hex)    |          |

| 0000    |          | Program  |

| •       | •        |          |

| · · ·   |          |          |

| 0011    |          |          |

| Data m  | emory    |          |

| 0020    | 01       |          |

| 0021    | 03       | Table of |

| 0022    | 05       | augends  |

| 0023    | FF       | (data)   |

| 0024    | 7F       |          |

|         |          |          |

| 0030    | 02       |          |

| 0031    | 04       | Table of |

| 0032    | 06       | addends  |

| 0033    | В        | (data)   |

| 0034    | 80       |          |

| 0040    |          |          |

| 0040    |          | Table of |

| 0042    |          | sums     |

| 0043    |          | (data)   |

| 0044    |          |          |

| Figure 4.8(a) - | Assembly    | language | program |

|-----------------|-------------|----------|---------|

| 1 - Bare(a)     | 1 100001101 | Bange    | program |

Figure 4.8(b) - Memory map

The first instruction in the program listed in Figure 4.8(a) initializes the index register to  $0020_{\rm H}$ . LDAA 00H, X instruction loads a number from the table of augends in data memory into accumulator A. The first number to be loaded is  $01_{\rm H}$  from the memory location  $0020_{\rm H}$  ( $0020_{\rm H} + 00_{\rm H} = 0020_{\rm H}$ ). Note that the instruction in line 2 has a label LOOP and is the target of a backward branch from the BNE LOOP operation towards the bottom of the program.

ADDA 10H,X instruction in line 3 adds the addend in data memory to the augend which is in accumulator A. The addend's memory location is  $0030_H (0020_H + 10_H = 0030_H)$ .

The fourth instruction (BCS STOP) checks whether the carry flag is set to 1. If C = 1, this indicates that the sum exceeded  $FF_H$  and the control is transferred to the end of the program. While C=0, execution continues from line 5. The STAA 20H,X instruction causes the sum in accumulator A to be stored in the "table of sums". In the first pass of the loop, the sum is stored into the memory location  $0040_H$  ( $0020_H + 20_H = 0040_H$ ).

The INX instruction in line 6 increments the contents of the index register. The CPX #0025H instruction in line 7 compares the current contents of the index register with  $0025_H$  to see whether the end of the table of augends is reached or not. The compare instruction is a subtract operation that is used to set or reset the Z flag. The BNE LOOP instruction in line 8 checks Z flag. If Z flag = 0, the branch test is true for the BNE instruction and the program branches back to the symbolic address LOOP in line 2. When the index register reaches  $0025_H$ , the compare operation sets the Z flag to 1, branch test of the BNE instruction becomes false, and the program continues with the next instruction in sequence. This is SWI instruction, which terminates the run.

# 5. 6802 ASSEMBLY LANGUAGE PROGRAMMING II

## 5.1 Increment and Decrement Instructions

Increment (INC) and decrement (DEC) instructions allow the contents of a register or memory location to be increased or decreased by 1 respectively.

## 5.2 Compare Instruction

Consider the problem of testing the accumulator contents, e.g., whether it contains  $37_{\rm H}$  or not. This can be achieved using substraction and BEQ instructions as shown in the following program.

|       | SUBA                | #37H         | ; Subtracts the value $37_{\rm H}$ from the AccumulatorA                        |

|-------|---------------------|--------------|---------------------------------------------------------------------------------|

|       | BEQ                 | PASS         | ; If the Zero Flag is set, branch to the label "PASS"                           |

| FAIL: | LDAB                | #01H         | ; Zero flag is not set so place 001 <sub>H</sub> in AccumulatorB                |

|       | BRA                 | STOP         | ; Returns to start                                                              |

| PASS: | LDAB                | #FFH         | ; Zero flag is set so place FF <sub>H</sub> in Acc B                            |

| STOP: | SWI                 |              |                                                                                 |

| PASS: | LDAB<br>BRA<br>LDAB | #01H<br>STOP | ; Zero flag is not set so place $001_{\rm H}$ in Accumulator ; Returns to start |

Subtracting  $37_{\rm H}$  from the accumulator causes the zero flag to be set if the accumulator containes  $37_{\rm H}$ . Accumulator B is loaded with either FF<sub>H</sub> or  $01_{\rm H}$ , to indicate an accumulator value of  $37_{\rm H}$  or non- $37_{\rm H}$  respectively. The difficulty with this technique is that it destroys the contents of the accumulator. Since this is a very common problem in assembly language programming, 6802 provides compare instructions (CMPA, CMPB, CBA, and CPX) which operate like subtraction but do not destroy the register contents.

Compare instructions subtract the contents of the accumulator or index register from the destination and change the condition of flags in CCR according to the result. Contents of the accumulator (or index register) and destination are unaffected by the execution of this instruction.

The above example program can be rewritten using CMPA instruction as follows:

| 5 |

|---|

|   |

| ) |

| [ |

|   |

|   |

The CMPA instruction subtracts the value  $37_{\rm H}$  from the Accumulator but does not place the result in the accumulator. It only changes the flags of the CCR.

| If the value $37_{\rm H}$ is equal to the contents of the Accumulator:     | Zero Flag = 1    |

|----------------------------------------------------------------------------|------------------|

|                                                                            | Carry Flag $= 0$ |

| If the value $37_{\rm H}$ is greater than the contents of the Accumulator: | Zero Flag = 0    |

|                                                                            | Carry Flag = 1   |

| If the value $37_{\rm H}$ is less than the contents of the Accumulator:    | Zero Flag = 0    |

|                                                                            | Carry Flag $= 0$ |

## 5.3 Logic and bit manipulation Instructions

## Logical Operators

Logical instructions (AND, OR, Exclusive OR) can be used to test or change group of bits. AND, OR and Exclusive OR are logical operators:

| AND         | OR           | Exclusive OR  |

|-------------|--------------|---------------|

| 0 AND 0 = 0 | 0  OR  0 = 0 | 0  XOR  0 = 0 |

| 0 AND 1 = 0 | 0  OR  1 = 1 | 0  XOR  1 = 1 |

| 1 AND 0 = 0 | 1  OR  0 = 1 | 1  XOR  0 = 1 |

| 1 AND 1 = 1 | 1  OR  1 = 1 | 1  XOR  1 = 0 |

Example:

Notice that any given bit in the result can only be 1 if both of the numbers have a 1 in that position. This property can be used to change specific bits in a register or memory location. In the following example the contents of a register is  $99_{\rm H}$ . To change the rightmost 4 bits to 0 and keep the other bits unchanged, the AND operation with  $F0_{\rm H}$  can be used.

$99_{\rm H} = 10011001$ F0<sub>H</sub> = 11110000 <u>AND</u> 10010000 = 90<sub>H</sub>

The 6802 AND instructions (ANDA, ANDB) can operate upon memory, register or immediate data:

| ANDA | 0FFH  | ; ANDs accumulator A with the contents of                   |

|------|-------|-------------------------------------------------------------|

|      |       | address location 00FF <sub>H</sub>                          |

| ANDA | 10H,X | ; ANDs accumulator A with the contents of                   |

|      |       | address location ( $10_{\rm H}$ + offset of index register) |

| ANDA | #20H  | ; ANDs accumulator A with the value $20_{\rm H}$            |

Other logical operations also use the same addressing modes:

| ANDA | AND with accumulator A |

|------|------------------------|

| ANDB | AND with accumulator B |

| ORAA | OR with accumulator B  |

| ORAB | OR with accumulator B  |

| EORA | XOR with accumulator A |

| EORB | XOR with accumulator B |

#### **Complement Instruction**

COMA, COMB and COM instructions complement the contents of the specified accumulator or a memory location. Complement instructions offer indexed and extended addressing modes.

COMA or COMB instruction complements the contents of the specified accumulator. No other status bit or register contents are affected. If accumulator B contains  $3A_H$  (00111010<sub>2</sub>), after the **COMB** instruction is executed, accumulator B contains  $C5_H$  (11000101<sub>2</sub>).

Complement instruction can also be used to complement the contents of the specified memory location. If the contents of the index register are  $0100_{\rm H}$  and contents of the memory location  $0113_{\rm H}$  is  $23_{\rm H}$  (00100011<sub>2</sub>), after **COM 13H,X** instruction is executed, the memory location  $0113_{\rm H}$  contains DC<sub>H</sub> (11011100<sub>2</sub>).

## The Bit Test Instruction

The Bit Test instruction (BIT) is similar to the logical Compare. The contents of the accumulator or memory location are ANDed with a mask. However, neither the accumulator nor the destination is modified by this instruction; only the Flags are affected.

BITA #07H tests the bits 1,2 and 3 of accumulator A and sets the zero flag if the condition is true

**Example:** Following program examines the byte at location  $120_{\text{H}}$ . If bit 1 of location  $120_{\text{H}}$  is set,  $55_{\text{H}}$  is stored in location  $130_{\text{H}}$ , otherwise program terminates.

| ORG 100H                      |                                  |

|-------------------------------|----------------------------------|

| LDAA 120H ; load byte         |                                  |

| BITA #01H ; is bit 1 set?     |                                  |

| BEQ STOP ; if not set, et     | nd program                       |

| LDAB $#55H$ ; store $55_H$ in | memory location 130 <sub>H</sub> |

| STAB 130H                     |                                  |

| SWI ; end program             | n                                |

.....

## 5.4 Arithmetic Operations

....

## 5.4.1 Addition Instructions

#### Add Accumulators

STOP:

ABA instruction adds the contents of accumulator B to the contents of accumulator A and stores the result in accumulator A. If accumulator A contains  $B4_H$  and accumulator B contains  $2D_H$ , after the ABA instruction is executed accumulator A contains  $E1_H$ .

#### Add Memory to Accumulator

ADDA, ADDB instructions add the contents of a memory location to accumulator A or B respectively without considering the carry status. The same memory addressing options as ADC instruction are supported.

**Ex (8-bit addition):** The following program adds the contents of memory locations  $0040_{\rm H}$  and  $0041_{\rm H}$ , and place the result in the memory location  $0042_{\rm H}$ .

| ORG  | 0H  |               |

|------|-----|---------------|

| LDAA | 40H |               |

| ADDA | 41H |               |

| STAA | 42H |               |

| SWI  |     | ; end program |

#### Add Memory, with carry, to Accumulator

ADCA or ADCB instructions add the contents of a memory location to accumulator A or B respectively. 4 addressing modes are supported:

- 1. Immediate

- 2. Direct

- 3. Extended

- 4. Indexed

#### Addition with carry using Immediate Data

This type of instruction adds the immediate data with the carry bit to accumulator A. If accumulator A contains  $3A_{H}$ , the carry bit is 1, after the instruction **ADCA #7CH** is executed, the accumulator A contains  $B7_{H}$ .

#### Addition with carry using Direct Memory Addressing.

This type of instruction adds the contents of a specified direct memory address and the carry bit to accumulator B. If accumulator B contains  $3A_H$  and memory address  $1F_H$  contains  $7C_H$  and carry bit contains 1. After the instruction **ADCB 1FH** is executed, accumulator B contains  $B7_H$ .

#### Addition with carry using Extended Addressing

This type of instruction is similar to the addition with carry using direct addressing. Only difference is that ADCA 3FF2<sub>H</sub> instruction allows extended addressing.

#### Addition with carry using Indexed Addressing

This type of instruction adds the carry bit and the contents of a memory location addressed by the sum of index register and the first operand of ADCA instruction to accumulator A. If accumulator A contains  $3A_{\rm H}$ , Index register contains  $50D_{\rm H}$ , memory address  $523_{\rm H}$  contains  $76_{\rm H}$ , and the carry bit is 1, After the instruction **ADCA 16H,X** is executed, accumulator A contains  $B1_{\rm H}$ .

**Ex (16-bit addition):** Following program adds 16-bit number in memory locations  $0040_{\rm H}$  and  $0041_{\rm H}$  to the 16-bit number in memory locations  $0042_{\rm H}$  and  $0043_{\rm H}$ . The most significant eight bits are in memory locations  $0040_{\rm H}$  and  $0042_{\rm H}$ . Then the result is stored into memory locations  $0044_{\rm H}$  and  $0045_{\rm H}$ , where the most significant bits are in  $0044_{\rm H}$ .

| ORG  | 0H  |                                        |

|------|-----|----------------------------------------|

| LDAA | 41H |                                        |

| ADDA | 43H | , add least significant bits           |

| STAA | 45H |                                        |

| LDAA | 40H |                                        |

| ADCA | 42H | ; add most significant bits with carry |

| STAA | 44H |                                        |

| SWI  |     | ; end program                          |

**ADCA 42H** adds the contents of accumulator A and the memory location 0042, plus the contents of Carry (C) bit. The carry from the addition of the least significant eight bits is thus included in the addition of the most significant eight bits.

## 5.4.2 Subtraction

#### Subtract Memory from Accumulator

SUBA, SUBB instructions subtract the contents of the selected memory byte from the contents of accumulator A  $\Theta$  and B respectively. The same addressing modes of ADC instruction are supported. If the memory address 0031<sub>H</sub> contains A0<sub>H</sub> and accumulator B contains E3<sub>H</sub>, after the **SUBB 31H** instruction is executed accumulator B contains 43<sub>H</sub>.

## 5.4.3 Shift Operations

#### Logical Shift Operations

LSRA, LSRB, LSR instructions perform a one-bit logical right shift on accumulator A, B or and a specified memory location respectively. The least significant bit is shifted into the carry bit in CCR and 0 is inserted as a most significant bit. If accumulator B contains  $7A_H$  (01111010<sub>2</sub>), after LSRB instruction is executed, accumulator B contains  $3D_H$  (00111101<sub>2</sub>) and the carry status bit is set to 0.

LSR instruction shifts the contents of the specified memory location towards right 1-bit. Indexed and extended addressing modes are available for LSR instruction. If the contents of the memory location  $04FA_{\rm H}$  is  $0D_{\rm H}$  (00001101<sub>2</sub>), after LSR 04FAH is executed, the carry bit is 1 and the contents of location  $04FA_{\rm H}$  is  $06_{\rm H}$  (00000110<sub>2</sub>).

**Ex:** Following program separates the contents of memory location  $0040_{\rm H}$  into two 4-bit numbers and stores them in memory locations  $0041_{\rm H}$  and  $0042_{\rm H}$ . It places the four consequitive most significant bits of memory location  $0040_{\rm H}$  into the four least significant bit positions of memory location  $0041_{\rm H}$ ; and the four least significant bit positions of memory location  $0041_{\rm H}$ ; and the four least significant bit positions of memory location  $0040_{\rm H}$  into the positions of memory location  $0041_{\rm H}$ ; and the four least significant bit positions of memory location  $0042_{\rm H}$ .

| LDAA | 40H  | ; load data                                                              |

|------|------|--------------------------------------------------------------------------|

| ANDA | #0FH | ; mask off four MSBs                                                     |

| STAA | 42H  | ; store at address 0042 <sub>H</sub>                                     |

| LDAA | 40H  | ; reload data                                                            |

| LSRA |      | ; shift accumulator to right 4 bits, clearing the most significant bits. |

| LSRA |      | ;                                                                        |

| LSRA |      | ;                                                                        |

| LSRA |      | ;                                                                        |

| STAA | 41H  | ; store at address 0041 <sub>H</sub>                                     |

| SWI  |      | ; end program                                                            |

## Arithmetic Shift Operations

ASLA or ASLB instructions perform a one-bit arithmetic left shift on the contents of accumulator A or B. If accumulator A contains  $7A_H$  (01111010<sub>2</sub>), after ASLA is executed F4<sub>H</sub> (11110100<sub>2</sub>) is stored in accumulator A, carry bit is set to 0, sign bit is set 1 (as the leftmost bit is 1) and Zero bit is set to 0.

ASL instruction performs a 1-bit arithmetic left shift on the contents of a memory location. The extended and indexed addressing modes are supported. If the Index register contains  $3F3C_{H}$ , and the memory address  $3F86_{H}$  contains  $CB_{H}$ , after the **ASL 4AH,X** instruction is executed, the memory address  $3F86_{H}$  contains  $96_{H}$  and Carry flag is set to 1. The ASL instruction is often used in multiplication routines. Note that execution of a single ASL instruction results with its operand multiplied by a factor of 2.

ASR instruction performs a one-bit arithmetic right shift on the contents of accumulator A or B or the contents of a selected memory byte. ASR is frequently used in division routines.

#### **Rotate Operations**

ROLA or ROLB instructions rotate the specified accumulator or a selected memory byte one bit towards left through the carry bit. ROLA or ROLB instructions rotate contents of the specified accumulator and the carry bit as a block towards left one bit. If accumulator A contains  $7A_H$  (01111010<sub>2</sub>) and the carry bit is 1, after **ROLA** instruction is executed, accumulator A contains  $F5_H$  (11110101<sub>H</sub>) and the carry bit is reset to 0.

ROL instruction rotates the contents of the specified memory location one bit to the left through the carry. Indexed and Extended addressing modes can be used with ROL instruction.

**Example:** If the contents of memory location  $1403_{\rm H}$  is  $2E_{\rm H}$  (00101110<sub>2</sub>) and the Carry bit is 0, after **ROL 1403H** is executed, memory location  $1403_{\rm H}$  contains  $5C_{\rm H}$  (01011100<sub>2</sub>).

RORA, RORB or ROR instructions rotate the specified accumulator or contents of a selected memory location and the carry bit as a block one bit towards right. These instructions operate similarly with the ROL instruction.

**Ex (8-bit binary multiplication):** Following program multiplies an 8-bit unsigned number in memory location  $0041_{\rm H}$  by another 8-bit unsigned number in the memory location  $0040_{\rm H}$  and places the most significant bits of the result in memory location  $0042_{\rm H}$  and eight least significant bits in memory location  $0043_{\rm H}$ .

Multiplying a number by zero results with zero, multiplying by one results with the number itself. Therefore the multiplication can be reduced to the following operation: If the current bit is 1, add the multiplicand to the partial product.

|        | CLRA<br>CLRB |       | ; product MSB = Zero<br>; product LSB = Zero              |

|--------|--------------|-------|-----------------------------------------------------------|

|        | LDX          | #8    | ; load number of bits of the multiplier to index register |

| SHIFT: | ASLB         |       | ; shift product left 1 bit                                |

|        | ROLA         |       |                                                           |

|        | ASL          | 40H   | ; shift multiplier left to examine next bit               |

|        | BCC          | DECR  |                                                           |

|        | ADDB         | 41H   | ; add multiplicand to the product if carry is 1           |

|        | ADCA         | #0    | ;                                                         |

| DECR:  | DEX          |       |                                                           |

|        | BNE          | SHIFT | ; repeat until index register is 0                        |

|        | STAA         | 42H   | ; store result                                            |

|        | STAB         | 43H   |                                                           |

|        | SWI          |       | ; end program                                             |

The following operations are performed to ensure that everything is lined up correctly every time:

1) Shift multiplier left one bit so that the bit to be examined is placed in the Carry.

2) Shift product left one bit so that the next addition is lined up correctly.

The complete process for binary multiplication is as follows:

Step 1 - Initialization

The Index register is used as a counter. CLRA and CLRB set the product and carry bit to 0.

Product=0 Counter=8 Step 2 - Shift Product to left so as to line up properly.

The instructions ASLB and ROLA together act as a 16-bit arithmetic left shift of the product in accumulators A and B (MSBs in A).

Step 3 - Shift Multiplier to left so the next bit goes to Carry to multiply.

The instruction ASL 40H shifts the contents of memory location 0040H left one bit, placing the most significant bit in the Carry and clearing the least significant bit.

Step 4- Add Multiplicand to Product if carry is 1

The instruction ADDB 41H adds the multiplicand to the product. The instruction ADCA #0 adds the carry flag from that 8-bit addition to the most significant eight bits of the product (in accumulator A).

If Carry=1, Product = Product + Multiplicand

Step 5 - Decrement counter and check for zero

Counter = Counter - 1 If Counter  $\neq 0$ , go to Step 2

If multiplier is  $61_{\rm H}$  and the multiplicand is  $6F_{\rm H}$ , the process works as follows:

Initialisation:

| Product      | 0000 |

|--------------|------|

| Multiplier   | 61   |

| Multiplicand | 6F   |

| Counter      | 08   |

After first iteration of steps:

| Product               | 0000 |

|-----------------------|------|

| Multiplier            | C2   |

| Multiplicand          | 6F   |

| Counter               | 07   |

| Carry from Multiplier | 0    |

After second iteration:

| Product               | 006F |

|-----------------------|------|

| Multiplier            | 84   |

| Multiplicand          | 6F   |

| Counter               | 06   |

| Carry from Multiplier | 1    |

After third iteration:

| Product               | 014D |

|-----------------------|------|

| Multiplier            | 08   |

| Multiplicand          | 6F   |

| Counter               | 05   |

| Carry from Multiplier | 1    |

Goes like this until counter is equal to 0.

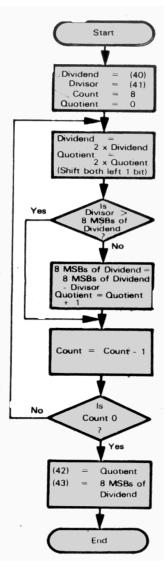

**Ex (8-bit binary division):** Following program divides an 8-bit unsigned number in memory location  $0040_{\rm H}$  by another 8-bit unsigned number in the memory location  $0041_{\rm H}$  and stores the quotient in memory location  $0042_{\rm H}$  and the remainder in memory location  $0043_{\rm H}$ . Initially accumulator A is cleared and dividend is loaded into accumulator B. During the division, the quotient replaces the dividend in accumulator B as the dividend is shifted left to accumulator A. At the end, remainder is found in accumulator A and quotient in accumulator B.

|         | LDX<br>CLRA  | #8     | ; load number of bits of the divisor into index register            |

|---------|--------------|--------|---------------------------------------------------------------------|

| DIVIDE: | LDAB<br>ASLB | 40H    | ; load dividend to accumulator B<br>; shift left dividend-quotient. |

|         | ROLA         |        | , shire tore divisional quotional                                   |

|         | CMPA         | 41H    | ; compare accumulator A and divisor                                 |

|         | BCS          | CHKCNT | ; branch if accumulator A is smaller than divisor                   |

|         | SUBA         | 41H    | ; subtract divisor from accumulator A                               |

|         | INCB         |        | ; increment quotient                                                |

| CHKCNT: | DEX          |        | ; decrement counter                                                 |

|         | BNE          | DIVIDE |                                                                     |

|         | STAB         | 42H    | ; store quotient                                                    |

|         | STAA         | 43H    | ; store remainder                                                   |

|         | SWI          |        | ; end program                                                       |

|         |              |        |                                                                     |

Figure 5.1 - Flowchart of division program

# 6. 6802 ASSEMBLY LANGUAGE PROGRAMMING III

## 6.1 STACK OPERATIONS

A "stack" is simply an area of memory where a list of data items is stored consecutively. It consists of any number of locations in RAM memory. The restriction in the list of the elements is that, the elements can be added or removed at one end of the list only. This end is usually called "top of stack" and the structure is sometimes referred to as a "push-down" stack. This type of storage mechanism is Last-In-First-Out "LIFO"; the last data item placed on the stack, is the first one removed when retrival begins.

PUSH operation places a new item on the stack. PULL operation removes the top item from the stack.

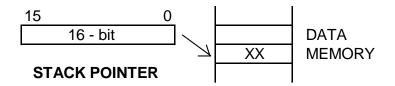

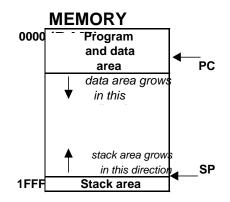

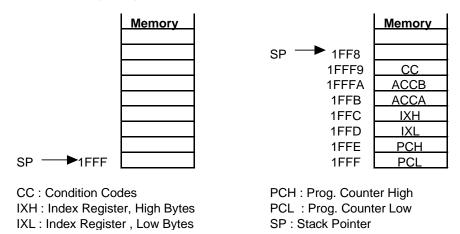

MC6802 microprocessor allows a porion of memory to be used as a stack. The microprocessing unit has a 16-bit stack pointer (Figure 6.1). When a byte of information is stored in the stack, it is stored at the address which is contained in the stack pointer. The stack pointer is decremented (by one) immediately following the storage of each byte of information in the stack. Conversely, the stack pointer is incremented (by one) immediately before retrieving each byte of information from the stack, and the byte is then obtained from the address contained in the stack pointer. The programmer must ensure that the stack pointer is initialized to the required address before the first execution of an instruction which manipulates the stack. Stack pointer can be initialized to use any portion of read-write memory, usually to the highest address of RAM (Figure 6.2).

Figure 6.1 - Stack Pointer

Figure 6.2 - Memory usage

Stack operations are used:

- while executing subroutines

- while handling interrupts

- while doing arithmetic operations

## 6.1.1 PUSH Operation

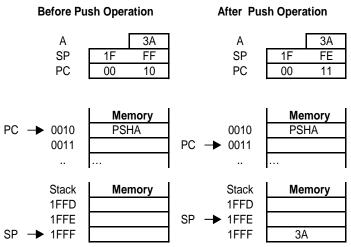

PSH instruction is used for storing a single byte of data in the stack. This instruction addresses either accumulator A or accumulator B (PSHA and PSHB respectively). The contents of the specified accumulator are stored in the stack. The address contained in the stack pointer is decremented. If accumulator A contains  $3A_H$  and the stack pointer contains  $1FFF_H$ . After the instruction **PSHA** is executed  $3A_H$  is stored into the location  $1FFF_H$  and the stack pointer is altered to  $1FFE_H$ , the PC is  $0011_H$  (Figure 6.3).

Figure 6.3 - Push (PSHA) instruction

## 6.1.2 PULL Operation

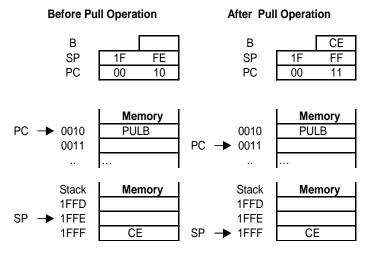

PUL instruction retrives data from the stack. This instruction addresses either accumulator A or accumulator B (PULA and PULB respectively). The address contained in the stack pointer is incremented. A single byte of data is then obtained from the stack and is loaded into the specified accumulator. If the stack pointer contains  $1FFE_H$  and location  $1FFF_H$  contains  $CE_H$ . After the instruction **PULB** is executed, accumulator B contains  $CE_H$  and the stack pointer contains  $1FFF_H$  (Figure 6.4).

Figure 6.4 - Pull (PULB) instruction

## 6.1.3 Other Stack Operations

The address stored in the stack pointer is affected by the execution of the instructions PSH, PUL, SWI, WAI, RTI, BSR, JSR, and RTS, and also by the servicing of a non-maskable interrupt or an interrupt request from a peripheral device.

The address in the stack pointer may also be changed without storing or retrieving information in the stack. This is carried out by the following instructions:

- DES decrement stack pointer

- INS increment stack pointer

- LDS load the stack pointer

- TXS transfer index register to stack pointer

The contents of the stack pointer is also involved in the execution of the following instructions:

- STS store the stack pointer

- TSX transfer stack pointer to index register

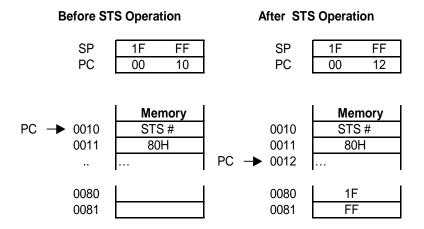

**STS** instruction stores the contents of the stack pointer into two contiguous memory locations. This instruction offers direct, indexed and extended addressing modes. The **STS** instruction stores the high byte of the stack pointer into the specified memory address and the low byte into the memory address immediately following it. In figure 6.5, the contents of the stack pointer is  $1FFF_H$  and the memory address to store the stack pointer is given as  $0080_H$  in the **STS #80H** instruction. After **STS** instruction is executed, memory location  $0080_H$  contains the high byte of stack pointer  $(1F_H)$  and memory location  $0081_H$  contains the low byte of stack pointer (FF\_H).

Figure 6.5 - Store Stack Pointer (STS) instruction

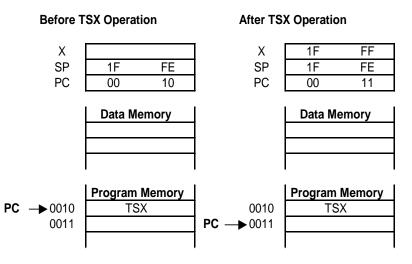

**TSX** instruction moves the contents of the stack pointer plus one to the index register so that the index register points directly to the bottom of the stack. In Figure 6.6, SP is  $1FFE_{H}$ . After the execution of **TSX** instruction, index register contains  $1FFF_{H}$ . The MC6802 employs a decrement after write, increment before read stack implementation scheme.

Figure 6.6 - TSX Instruction

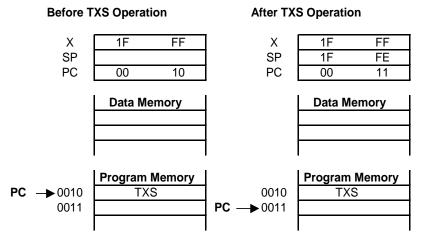

**TXS** instruction moves the contents of the index register minus 1 to the stack pointer. In Figure 6.7, contents of the index register is  $1FFF_{H}$ . After **TXS** is executed, stack pointer contains  $1FFE_{H}$ .

Figure 6.7 - Move From Index Register to Stack Pointer (TXS) instruction

**Example:** In the following program, the contents of the accumulators are stored in the stack before branching to a routine and at the end of routine, the original values of the accumulator are restored from the stack.

ORG 100H LDAA #03H LDAB #04H LDS #1FFFH PSHA PSHB BRA LDRT

| CONT: | PULA |      |

|-------|------|------|

|       | PULB |      |

|       | ABA  |      |

|       | STAA | 61H  |

|       | SWI  |      |

|       |      |      |

| LDRT: | LDAA | #01H |

|       | LDAB | #02H |

|       | ABA  |      |

|       | STAA | 60H  |

|       | BRA  | CONT |

At the beginning of the program accumulator A and B is loaded with  $03_H$  and  $04_H$  and stack pointer is initialized to point the end of memory (1FFF<sub>H</sub>). Then, before branching to the routine LDRT these numbers are stored in the stack using PSH instructions. In LDRT routine,  $01_H$  and  $02_H$  are added using ABA instruction and  $(03_H)$  is stored in memory location  $0060_H$  and CONT is branched. Then the original values of the accumulators are loaded from the stack using PUL instructions, and the result  $(07_H)$  is stored in  $0061_H$  and the program ends with the execution of SWI instruction.

## 6.2 SUBROUTINES

In a given program it is often necessary to perform a particular task a number of times on the same or on different data values (such as subroutines to obtain time delay, subroutine to sort a list of values, etc.) including the block of instructions to perform the task at every place where it is needed in the program causes a waste of memory. Instead, it is better to place only one copy of this block of machine instructions in the main memory as a subroutine, and in the program branch to the beginning of the subroutine whenever required.

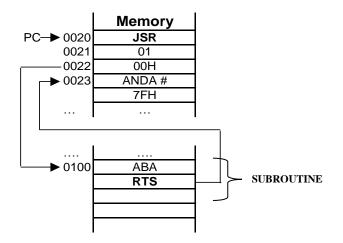

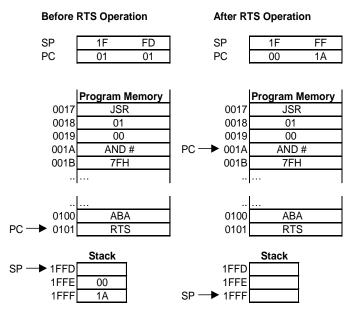

In figure 6.8, the execution of a jump to subroutine instruction (JSR) and return from subroutine instruction (RTS) are given. After JSR 0100H instruction is executed, PC is set to the defined address and execution continues with the ABA instruction. The program returns from this subroutine after the RTS instruction is executed. Program counter (PC) is set to  $0023_{\rm H}$  and the program execution continues with ANDA #7FH instruction.

Figure 6.8 - A subroutine execution process

## 6.2.1 Jump to a subroutine

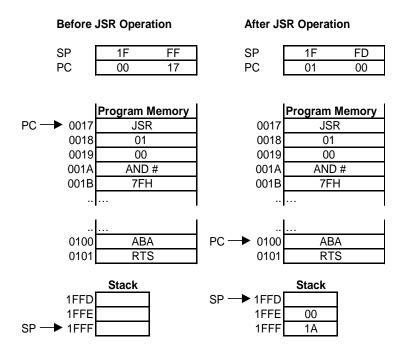

**JSR** instruction uses extended and indexed addressing modes. After **JSR** instruction is executed, program counter is decremented by 3 (if extended addressing is used) or 2 (if indexed addressing is used), and then is pushed onto the stack. The stack pointer is adjusted to point to the next empty location in the stack. The specified memory address is then loaded into the program counter and execution continues with the first instruction in the subroutine.

## Using Extended Addressing

Execution of JSR instruction with extended addressing mode is shown in Figure 6.9. After **JSR 0100H** instruction is executed, address of the next instruction (**AND #7FH** instruction) is stored on top of the stack, and SP is decremented by 2. Address of the first instruction in the subroutine  $(0100_{\rm H})$  is stored into the program counter, and the program continues from this point. ABA instruction is the next instruction to be executed.

Figure 6.9 - Jump to subroutine (JSR) instruction, using extended addressing

#### Using Indexed Addressing

Execution of JSR instruction with indexed addressing mode is shown in Figure 6.10. After **JSR 30H,X** instruction is executed, address of the next instruction  $(0019_{\rm H})$  is stored on top of the stack and SP is decremented by 2. Jump address is calculated as the value of the index register plus the address part of the instruction  $(1100_H + 30_H = 1130_H)$  and it is stored in PC. The program continues with the ABA instruction in the subroutine.

Х

| Before JSR Operation |

|----------------------|

|----------------------|

After JSR Operation

| Х  | 11 | 00 |

|----|----|----|

| SP | 1F | FF |

| PC | 00 | 17 |

00 11 SP 1F FD PC 11 30

|                           | Program Memory |                            | Program Memory           |

|---------------------------|----------------|----------------------------|--------------------------|

| PC - 0017                 | JSR            | 0017                       | JSR                      |

| 0018                      | 30H,X          | 0018                       | 30H,X                    |

| 0019                      | AND #          | 0019                       | AND #                    |

| 001A                      | 7FH            | 001A                       | 7FH                      |

| [                         |                |                            |                          |

|                           |                |                            | I                        |

| 1130                      | ABA            | PC - 1130                  | ABA                      |

| 1131                      | RTS            | 1131                       | RTS                      |

| 1FFD<br>1FFE<br>SP → 1FFF | Stack          | SP ─► 1FFD<br>1FFE<br>1FFF | <b>Stack</b><br>00<br>19 |

Figure 6.10 - Jump to subroutine (JSR) instruction, using indexed addressing

## 6.2.2 Return from a subroutine

RTS instruction moves the contents of the top two stack bytes (which is the address of the next instruction after JSR) to program counter. These two bytes provide the address of the next instruction to be executed. Previous program counter contents are lost. RTS instruction also increments the stack pointer by 2 (Fig 6.11). Every subroutine must contain at least one Return instruction; which is the last instruction to be executed in the subroutine.

Figure 6.11 - Return from subroutine (RTS) instruction

## **Example:**

Determine the lengths of two strings of ASCII characters. Starting addresses of the strings are  $43_{\rm H}$  and  $63_{\rm H}$ . End of a string is marked by a carriage return character (0D<sub>H</sub>). Write a subroutine which calculates the length of a string (excluding carriage return character) and places it in accumulator B. Also write a calling program which calls this subroutine to calculate the lengths of two strings and stores the results (in accumulator B) in memory addresses 42H and 62H.

#### **Calling Program:**

|             | ORG  | 0H    |                                            |

|-------------|------|-------|--------------------------------------------|

|             | LDS  | #500H | ; Start stack at location 500H             |

|             | LDX  | #43H  | ; Get starting address of the first string |

|             | JSR  | STLEN | ; Determine string length                  |

|             | STAB | 42H   | ; Store string length                      |

|             | LDX  | #63H  | ; Get starting address of second string    |

|             | JSR  | STLEN | ; Determine string length                  |

|             | STAB | 62H   | ; Store string length                      |

|             | SWI  |       |                                            |

| Subroutine: |      |       |                                            |

|             |      |       |                                            |

|             | ORG  | 100H  |                                            |

| STLEN:      | CLRB |       | ; String length $= 0$                      |

|             | LDAA | #0DH  | ; Get 'CR' for comparison                  |

| CHKCR:      | CMPA | Х     | ; Is character 'CR'?                       |

|             | BEQ  | DONE  | ; Yes, end of string                       |

|             | INCB |       | ; No, add 1 to string length               |

|             | INCX |       |                                            |

|             | BRA  | CHKCR |                                            |

| DONE:       | RTS  |       |                                            |

The calling program initializes the stack pointer to  $500_{\rm H}$  and then performs the following steps for each string:

- 1. places the starting address of the string in the Index register

- 2. calls the subroutine

- 3. stores the result in accumulator B to memory.

The stack pointer must be initialized to an appropriate area in memory (in this example  $500_{\rm H}$ ) so that the stack does not use the addresses in the program area.

The subroutine determines the length of a string of ASCII characters and places the length in accumulator B. Starting address of the string is a parameter to the subroutine. It is placed in the index register before the subroutine is jumped. The result is returned in accumulator B.

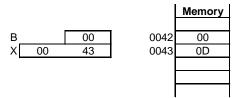

If the first string is only a carriage return character and index register (X) contains  $0043_{\rm H}$ , after the first call of the subroutine, contents of the registers and memory are as follows:

Figure 6.12 - Memory allocated for the first string

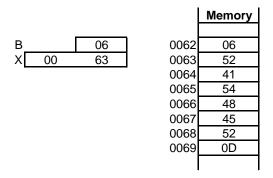

If the second string is 'RATHER' and index register contains  $0063_{\rm H}$ , after the second call of the subroutine, contents of the registers and memory are as follows:

Figure 6.13 - Memory allocated for the second string

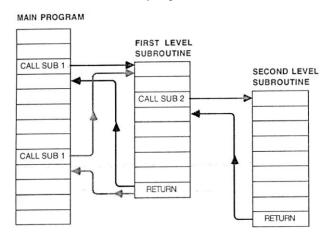

## 5.2.3 Subroutine Nesting

A subroutine may jump to another subroutine as shown in Figure 6.14. This situation can be extended to the case where the second subroutine jumps to a third subroutine and so on. This is called *subroutine nesting*, and can be carried out to any depth.

Figure 6.14 - Subroutine nesting

**Example :** The following program uses subroutine nesting to write the number  $FF_H$  into a memory block. Starting address of the memory block is  $00_H$  and the end of the block is determined by the number in accumulator B. Subroutine FILL, in a loop, stores  $00_H$  to the memory location pointed by the index register (X) and calls subroutine DECR to decrement accumulator B.

|       | ORG<br>LDS<br>LDX<br>LDAA<br>LDAB<br>JSR<br>SWI | 100H<br>#1FFFH<br>#00H<br>#0FFH<br>#25H<br>FILL | ; initialize stating address of stack area<br>; initialize index register<br>; keep $FF_H$ in accumulator A<br>; length of the memory block is $25_H$<br>; start filling                                                                                      |

|-------|-------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILL: | ORG<br>STAA<br>INX<br>JSR<br>CMPB<br>BNE<br>RTS | 500H<br>0H,X<br>DECR<br>#0H<br>FILL             | ;<br>; store FF <sub>H</sub> in the memory address pointed by X<br>; increment X to point to the next location<br>; jump to DECR subroutine<br>; Is the end of memory block reached?<br>; No, continue with the filling procedure<br>; Yes, end of subroutine |

| DECR: | ORG<br>DECB<br>RTS                              | 1000FH                                          | ;<br>; decrement accumulator B<br>; return to FILL subroutine                                                                                                                                                                                                 |

## 5.3 MACROS

In source programs, particular sequences of instructions may occur many times. Programmer can avoid repeatedly writing out the same instruction sequence by using a macro.

Macros allow the programmer to assign a name to an instruction sequence. This macro name is then used in the source program in the place of the related instruction sequence. Before assembling macroprocessor replaces the macro name with the appropriate sequence of instructions.

Macros are not the same as subroutines. A subroutine occurs in a program, and program execution branches to the subroutine. A macro is expanded to an actual instruction sequence each time the macro occurs; thus a macro does not cause any branching. Figure 6.15 shows the source program with macro calls and the object program after the macro expansion.

| MAC1 MACRO (macro definition)   instruction M1<br>instruction M2<br>instruction M3 (end of macro definition)   Instruction M3 (end of macro definition)   instruction P2<br>instruction P3 (main program)   MAC1 (instruction P1<br>instruction P3   MAC1 (instruction P3<br>instruction P4<br>instruction P6<br>instruction P7   MAC1 (instruction P4<br>instruction P6<br>instruction P7   MAC1 (instruction P4<br>instruction P6<br>instruction P7   MAC1 (instruction P7<br>instruction P8<br>instruction P9   MAC1 (instruction P8<br>instruction P10<br>instruction P11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | Source Prog                      | iram                      | Object Program                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|---------------------------|----------------------------------|

| instruction M2<br>instruction M3<br>ENDM (end of macro definition)<br>instruction P2<br>instruction P2<br>instruction P3<br>MAC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MAC1 | MACRO                            | (macro definition)        |                                  |

| instruction P2<br>instruction P3<br>MAC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | instruction M2                   |                           |                                  |

| instruction P2<br>instruction P3<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1<br>MAC1 |      | ENDM                             | (end of macro definition) |                                  |