#### DELFIM LUIZ TOROK

# PROJETO VISANDO A PROTOTIPAÇÃO DO PROTOCOLO DE ACESSO AO MEIO EM REDES ETHERNET

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre.

Curso de Pós-Graduação em Ciência da Computação, Faculdade de Informática,

Pontificia Universidade Católica do Rio Grande do Sul.

Orientador: Prof. Ney Dr. Laert Vilar Calazans

PORTO ALEGRE

**AGOSTO DE 2001**

# Dados Internacionais de Catalogação na Publicação (CIP)

T686p Torok, Delfim Luiz

Projeto visando a prototipação do protocolo de acesso ao meio em redes ethernet / Delfim Luiz Torok. – Porto Alegre, 2001.

135 f.

Diss. (Mestrado) – Fac. de Informática, PUCRS, 2001.

1. Redes de Computadores. 2. Redes Locais de Computadores. 3. Ethernet. 4. VHDL (Linguagem de Programação). I. Título.

> CDD 004.6 004.68

> > Fone: 0 (xx) 51 3320-3544

FAX: 0 (xx) 51 3320-3548

e-mail: bceadm@pucrs.br

Ficha Catalográfica elaborada pelo Setor de Processamento Técnico da BC-PUCRS

#### **AGRADECIMENTOS**

Agradeço aos meus pais, Delfim e Angelina Torok, pelo constante apoio e incentivo, que me permitiram a conclusão de mais esta etapa.

Ao professor Ney Laert Vilar Calazans, pela incansável orientação, constante dedicação e valiosos ensinamentos, ao longo do desenvolvimento deste trabalho e de todo o curso, suportando pacientemente os problemas das versões "beta".

Ao professor Fernando Gehm Moraes pelo seu oportuno apoio, antes e durante todo o desenvolvimento deste projeto, fornecendo ensinamentos e técnicas práticas para solução dos problemas encontrados no caminho.

Ao amigo, colega e parceiro de mestrado Ewerton Artur Capelati, que de certa forma participou do desenvolvimento deste projeto, com desenvolvimento correlato do seu trabalho de conclusão, pelo companheirismo e amizade dedicados ao longo desta jornada.

Aos professores e funcionários da Faculdade de Informática – FACIN da PUCRS, suporte fundamental ao longo destes anos de preparação. Em especial aos alunos, bolsistas e colegas do Grupo de Apoio ao Projeto de Hardware - GAPH, sempre atenciosos e dispostos a ajudar na busca de informações.

Aos amigos e colegas de mestrado, que de uma forma ou de outra forneceram estímulos para que este trabalho fosse realizado.

E ao Centro Universitário FEEVALE em Novo Hamburgo. Especialmente ao então Diretor do Centro de Ciência da Computação, Dr professor Cleber Cristiano Prodanov, que na época possibilitou meu ingresso no programa qualificação do Corpo Docente, desenvolvido nesta Instituição, promovendo a parceria PUCRS/FEEVALE na realização do curso de Mestrado em Informática da Pontificia Universidade Católica do Rio Grande do Sul e por acreditar sinceramente neste projeto.

# SUMÁRIO

| LIST  | A DE FIGURAS                                                            | VII  |

|-------|-------------------------------------------------------------------------|------|

| LIST  | A DE TABELAS                                                            | XII  |

| LIST  | A DE ABREVIATURAS                                                       | XIII |

| RES   | UMO                                                                     | XVI  |

| ABS   | TRACT                                                                   | XVII |

|       | TRODUÇÃO                                                                |      |

| 1.1   | Objetivos                                                               |      |

| 1.2   | Motivação                                                               |      |

| 1.3   | A Estrutura do Volume                                                   | 3    |

| 2. H  | ARDWARE RECONFIGURÁVEL                                                  | 4    |

| 2.1   | Introdução                                                              |      |

| 2.2   | Formas de Configurar FPGAs                                              | 5    |

| 2.2.1 | Tecnologia de Configuração SRAM                                         | 5    |

| 2.2.2 | Tecnologia de Configuração Antifusível.                                 | 5    |

|       | Tecnologia de Configuração de Porta Flutuante                           |      |

| 2.3   | Arquiteturas de Blocos Lógicos                                          | 7    |

| 2.3.1 | Arquiteturas de Grão Pequeno                                            | 8    |

| 2.3.2 | Arquiteturas de Grão Grande                                             | 10   |

| 2.4   | Arquiteturas de Roteamento                                              | 13   |

| 2.5   | Granularidade, Densidade e Desempenho de FPGAs                          | 14   |

| 2.6   | Núcleos de Propriedade Intelectual (IP Cores)                           | 16   |

|       | Classificação de IP Cores                                               |      |

| 2.7   | Famílias Recentes de FPGAs e CPLDs                                      | 17   |

| 2.7.1 | Blocos Lógicos do tipo Cluster e Módulos com Funcionalidade Específica  | 18   |

|       | Capacidades Especiais e IP Hard/Soft Cores                              |      |

| 3. Al | RQUITETURAS RECONFIGURÁVEIS/PROTOTIPAÇÃO RÁPIDA                         | 25   |

| 3.1   | Definições Básicas                                                      |      |

| 3.2   | Classificações das Arquiteturas Reconfiguráveis                         | 26   |

| 3.2.1 | Introdução                                                              |      |

|       | Classificação de Page                                                   |      |

|       | Classificação de Sanchez.                                               |      |

|       | Proposta de Novos Critérios de Classificação                            |      |

|       | Estudos de Caso de Arquiteturas Reconfiguráveis                         |      |

|       | PRISM - Processor Reconfiguration through Instruction-Set Metamorphosis |      |

|       | DISC - Dynamic Instruction-Set Computer                                 |      |

|       | SPLASH                                                                  |      |

|       | DEC-Perle                                                               |      |

| 3.4   | Plataformas de Prototipação Rápida para Sistemas Digitais               |      |

|       | Introdução                                                              |      |

|       | Plataforma de Prototipação Virtual Workbench                            |      |

|       | Plataforma HOT2-XL                                                      |      |

|       |                                                                         |      |

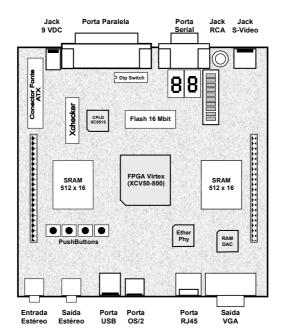

| 3.4.4  | Plataforma XSV                                              | 40  |

|--------|-------------------------------------------------------------|-----|

| 4. RI  | EDES DE COMPUTADORES                                        | 43  |

| 4.1    | Introdução                                                  | 43  |

| 4.2    | Redes Locais (LANs)                                         |     |

| 4.3    | O Modelo OSI-RM                                             |     |

| 4.4    | A Tecnologia Ethernet e o Padrão IEEE 802.3                 |     |

|        | Protocolo da Camada MAC                                     |     |

|        | Detecção de Colisões e Backoff no CSMA/CD                   |     |

| 4.5    | Atividades do Subnível MAC                                  |     |

| 4.6    | Estudo de Caso de um Controlador de Acesso a Rede (CS8900A) | 53  |

| 5. DI  | ESENVOLVIMENTO DE NICS ETHERNET SOBRE FPGAS                 |     |

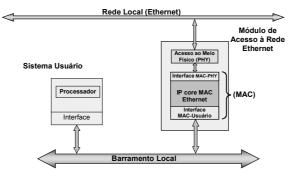

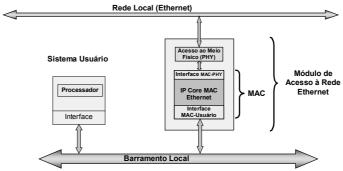

| 5.1    | Ambiente do IP Soft Core Proposto                           |     |

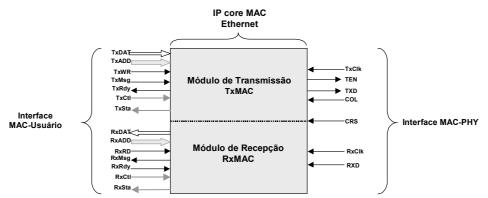

| 5.2    | Especificação e Projeto Geral do IP Core MAC Ethernet       |     |

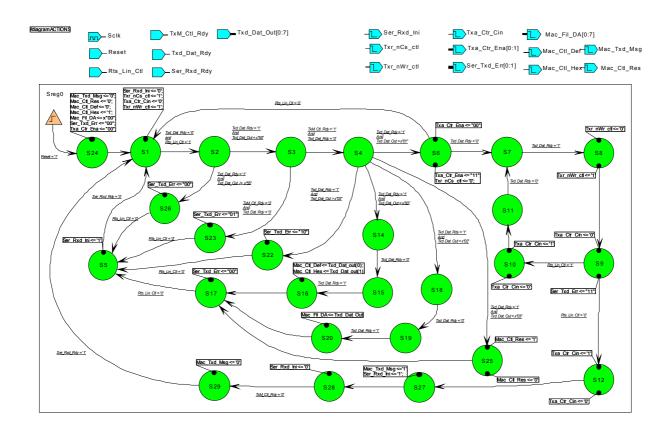

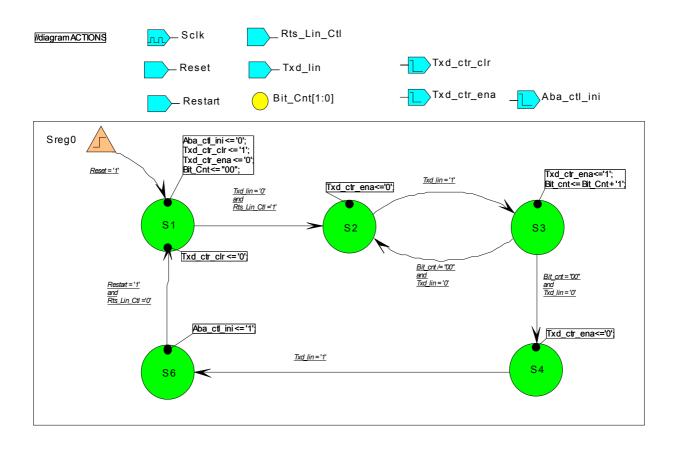

| 5.3    | Especificação e Projeto do Controle de Transmissão (TxMAC)  | 58  |

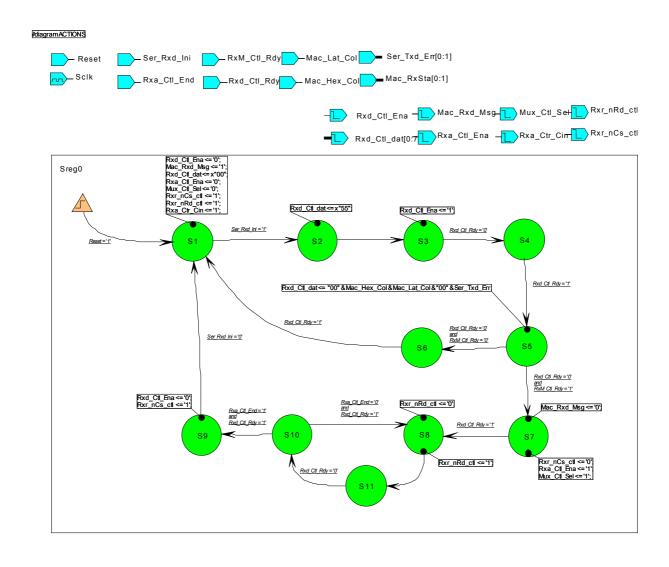

| 5.4    | Especificação e Projeto do Controle de Recepção (RxMAC)     | 64  |

| 6. ES  | STRATÉGIA DE VALIDAÇÃO FUNCIONAL DO PROJETO                 | 73  |

| 6.1    | Fase de Validação Funcional do TxMAC                        | 74  |

| 6.2    | Fase de Validação Funcional do RxMAC                        |     |

| 6.3    | Conclusão                                                   | 82  |

| 7 PF   | ROTOTIPAÇÃO DO IP SOFT CORE PARA O MAC ETHERNET             | 84  |

| 7.1    | Plataforma de Prototipação                                  |     |

|        | Limitações de Software e Hardware                           |     |

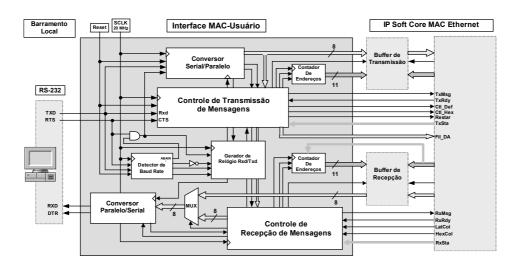

| 7.2    | Módulo MAC-Usuário do Protótipo                             |     |

| 7.3    | Proposta de Montagens para Validação a Nível de Protótipo   |     |

| 7.4    | Resultados Preliminares da Prototipação                     |     |

| 8. C   | ONCLUSÕES E TRABALHOS FUTUROS                               | 91  |

| A NI E | XO A                                                        | 94  |

|        | AO A                                                        |     |

| ANE    | XO B                                                        | 95  |

| ANE    | XO C                                                        | 96  |

| ANE    | XO D                                                        | 97  |

|        |                                                             |     |

| ANE    | XO E                                                        | 103 |

| ANE    | XO F                                                        | 112 |

| REF    | ERÊNCIAS BIBLIOGRÁFICAS                                     | 115 |

# **LISTA DE FIGURAS**

| Figura 2.1 - Arquitetura de um FPGA genérico.                                                                          | 4  |

|------------------------------------------------------------------------------------------------------------------------|----|

| Figura 2.2 – Duas opções de tecnologia de configuração de FPGAs.                                                       | 5  |

| Figura 2.3 - Tecnologia de programação antifusível.                                                                    | 6  |

| Figura 2.4 - Tecnologia de programação porta flutuante.                                                                | 6  |

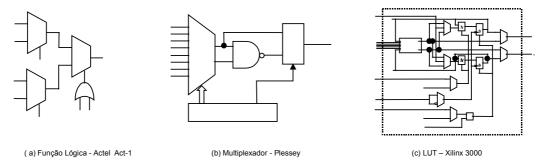

| Figura 2.5 - Exemplos das estruturas de blocos lógicos.                                                                | 7  |

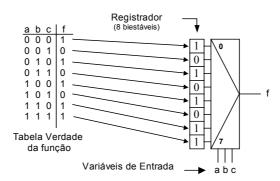

| Figura 2.6 - LUT para tabelas de 3 variáveis, implementando a função $f = ab + \overline{c}$                           | 8  |

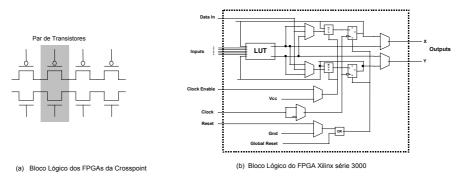

| Figura 2.7 - Blocos lógicos (a) Crosspoint e (b) Xilinx série 3000.                                                    | 8  |

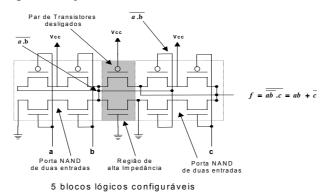

| Figura 2.8 - FPGA Crosspoint configurado para a função $f = ab + \overline{c}$ implementando $f = \overline{ab.c}$     | 9  |

| Figura 2.9 - Bloco lógico do FPGA ERA60100 da Plessey Semiconductor.                                                   | 9  |

| Figura 2.10 – Implementações estruturais da função $f = ab + \overline{c}$ . (a) Direta. (b) Equivalente               | 9  |

| Figura 2.11 – Blocos lógicos Actel (a) Bloco lógico da Act-1. (b) Função $f = ab + \overline{c}$ implementada no Bloco | Э  |

| Act-1. (c) Bloco lógico da Act-2.                                                                                      | 10 |

| Figura 2.12 - Bloco lógico da QuickLogic.                                                                              | 10 |

| Figura 2.13 - Bloco lógico Xilinx série 4000.                                                                          | 12 |

| Figura 2.14 - Bloco lógico Altera série 5000 e seu emprego.                                                            | 12 |

| Figura 2.15 - Arquitetura de roteamento genérica.                                                                      | 13 |

| Figura 2.16 - Arquitetura de roteamento Xilinx 4000.                                                                   | 14 |

| Figura 2.17 - Implementação da função lógica $f = abd + bc\overline{d} + \overline{a}\overline{b}\overline{c}$ .       | 14 |

| Figura 2.18 - Número de blocos e área do bloco para um circuito [ROS93]                                                | 15 |

| Figura 2.19 - Número de blocos e área de roteamento versus tamanho do bloco para um circuito exemplo                   | 0  |

| [ROS93].                                                                                                               | 15 |

| Figura 2.20 – Estrutura interna de blocos lógicos em FPGAs modernos: (a) elemento lógico básico e (b) cluste           | r  |

| lógico.                                                                                                                | 18 |

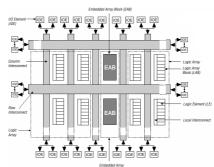

| Figura 2.21 –Arquitetura da família FLEX 10K da Altera.                                                                | 19 |

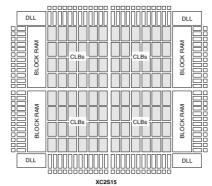

| Figura 2.22 - Planta baixa básica da família de FPGAs Spartan-II da Xilinx. ilustrada com o dispositivo                | )  |

| XC2S15                                                                                                                 | 20 |

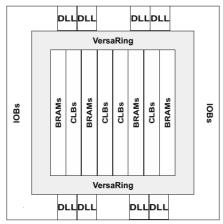

| Figura 2.23 – Planta baixa da família de FPGAs APEX 20K da Altera.                                                     | 20 |

| Figura 2.24 – Planta baixa típica dos dispositivos da família Virtex da Xilinx. Exemplo é a subfamília Virtex-E        | 21 |

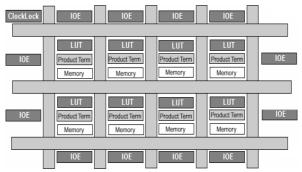

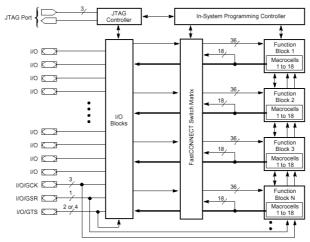

| Figura 2.25 – Arquitetura da família XC9500 da Xilinx.                                                    | 21    |

|-----------------------------------------------------------------------------------------------------------|-------|

| Figura 2.26 – Bloco de funções (FB) da família XC9500 da Xilinx.                                          | 22    |

| Figura 2.27 – Família AT6000 da Atmel utiliza a tecnologia SRAM e permite reconfiguração parcial          | 23    |

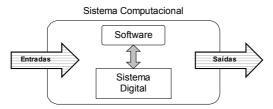

| Figura 3.1 - Sistema computacional.                                                                       | 25    |

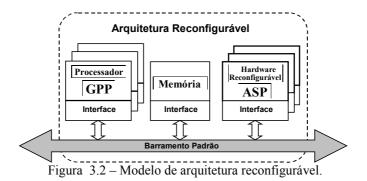

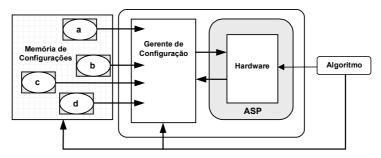

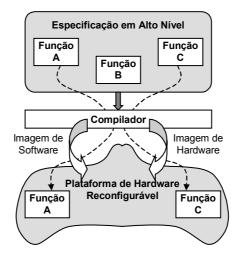

| Figura 3.2 – Modelo de arquitetura reconfigurável.                                                        | 26    |

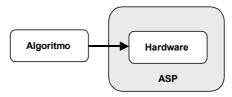

| Figura 3.3 – Classificação de arquiteturas reconfiguráveis segundo o critério forma de execução do algor  | ritmo |

| pelo ASP: Hardware puro                                                                                   | 28    |

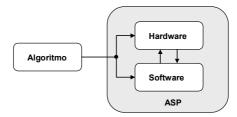

| Figura 3.4 - Classificação de arquiteturas reconfiguráveis segundo o critério forma de execução do algor  | ritmo |

| pelo ASP: Processador de aplicação específica                                                             | 29    |

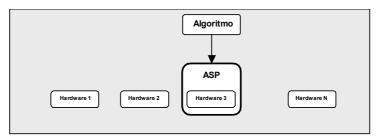

| Figura 3.5 - Classificação de arquiteturas reconfiguráveis segundo o critério forma de execução do algor  | ritmo |

| pelo ASP: Reuso seqüencial.                                                                               | 29    |

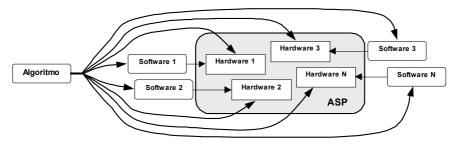

| Figura 3.6 - Classificação de arquiteturas reconfiguráveis segundo o critério forma de execução do algor  | ritmo |

| pelo ASP: Uso múltiplo simultâneo.                                                                        | 29    |

| Figura 3.7 - Classificação de arquiteturas reconfiguráveis segundo o critério forma de execução do algor  | ritmo |

| pelo ASP: Uso sob demanda.                                                                                | 30    |

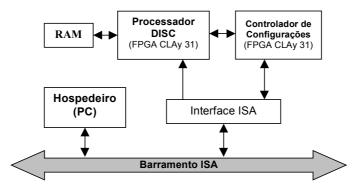

| Figura 3.8 - Arquitetura reconfigurável PRISM.                                                            | 33    |

| Figura 3.9 - Estrutura geral arquitetura DISC                                                             | 34    |

| Figura 3.10 - Descrição física da distribuição interna de recursos de hardware do processador DISC        | 35    |

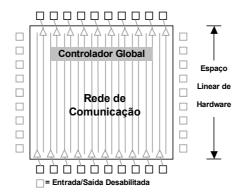

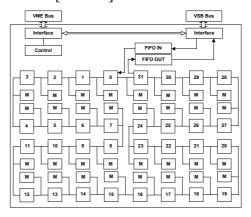

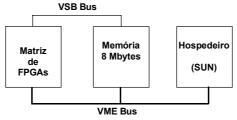

| Figura 3.11 - Arquitetura SPLASH, mostrando as interfaces VME, VSB e a matriz de 32 estágios              | 35    |

| Figura 3.12 - Sistema SPLASH.                                                                             | 35    |

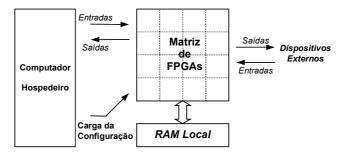

| Figura 3.13 - Arquitetura da célula básica da arquitetura DEC-Perle, mostrando a matriz de FPGAs e detalh | ne da |

| célula PAB                                                                                                | 36    |

| Figura 3.14 - Arquitetura genérica de um processador baseado em PAMs.                                     | 37    |

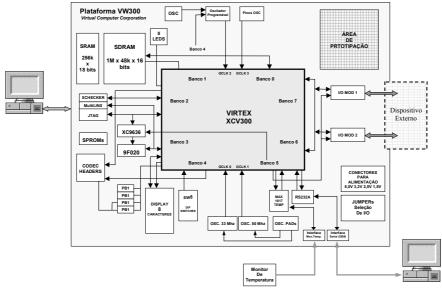

| Figura 3.15. Diagrama de blocos da plataforma VW300.                                                      | 39    |

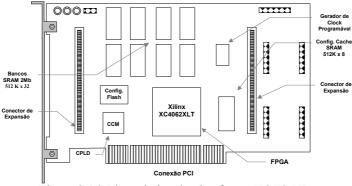

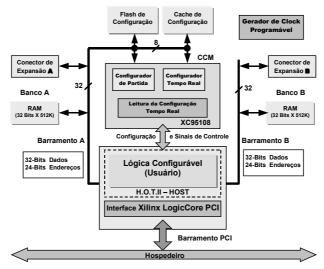

| Figura 3.16. Planta baixa da plataforma HOT2-XL.                                                          | 39    |

| Figura 3.17. Diagrama de blocos da plataforma HOT2-XL.                                                    | 40    |

| Figura 3.18. Vista simplificada da plataforma XSV.                                                        | 41    |

| Figura 4.1 - Topologia (a) Ponto a Ponto e (b) Multiponto.                                                | 44    |

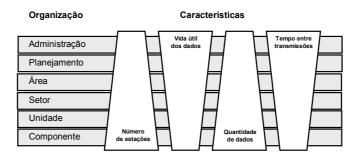

| Figura 4.2 - Característica das comunicações em redes de computadores.                                    | 45    |

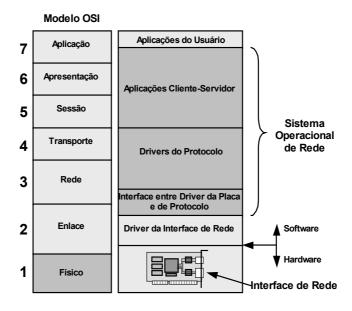

| Figura 4.3 - O OSI-RM e um exemplo típico de sistema operacional de rede.                                 | 46    |

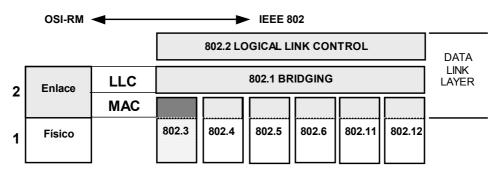

| Figura 4.4 - Relação entre os padrões IEEE 802 e o OSI-RM                                                 | 47    |

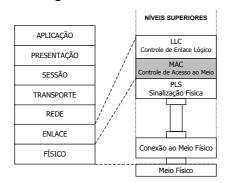

| Figura 4.5. O Padrão IEEE 802.3 e sua relação com o OSI-RM.                                               | 48  |

|-----------------------------------------------------------------------------------------------------------|-----|

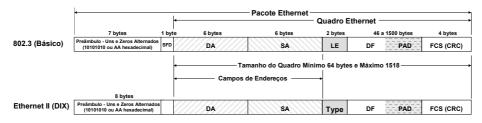

| Figura 4.6. Quadros IEEE 802.3 (básico) e Ethernet II (DIX).                                              | 48  |

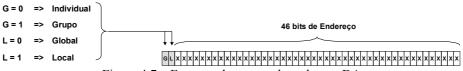

| Figura 4.7 – Formato do campo de endereço DA.                                                             | 50  |

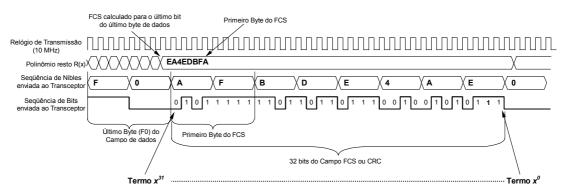

| Figura 4.8 – Montagem do CRC no final do quadro.                                                          | 51  |

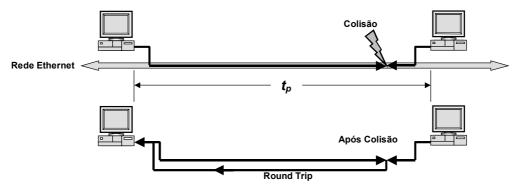

| Figura 4.9 – Colisão e pós colisão na rede Ethernet.                                                      | 52  |

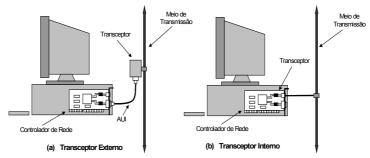

| Figura 4.10 - Duas formas de conexão de NICs Ethernet ao meio físico de transmissão                       | 54  |

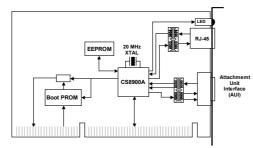

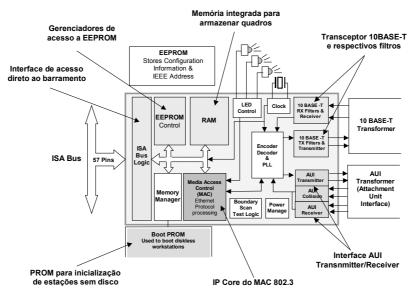

| Figura 4.11 - NIC Ethernet construído em torno do CI CS8900A da Cirrus Logic, Inc                         | 54  |

| Figura 4.12 - CS8900A mostrando uma configuração básica de NIC Ethernet                                   | 54  |

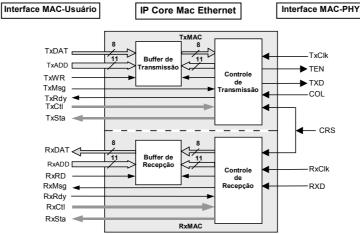

| Figura 5.1 –Diagrama de blocos mostrando o ambiente típico de emprego do IP core desenvolvido             | 55  |

| Figura 5.2 – Entradas e Saídas do IP core MAC Ethernet.                                                   | 56  |

| Figura 5.3 – Diagrama de blocos do IP core e interfaces.                                                  | 57  |

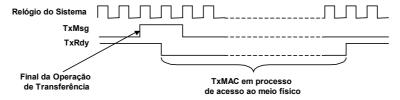

| Figura 5.4 - Diagrama de tempos da operação de transferência de mensagens do sistema usuário ao TxMAC     | 57  |

| Figura 5.5 - Fluxograma da fase deferimento.                                                              | 58  |

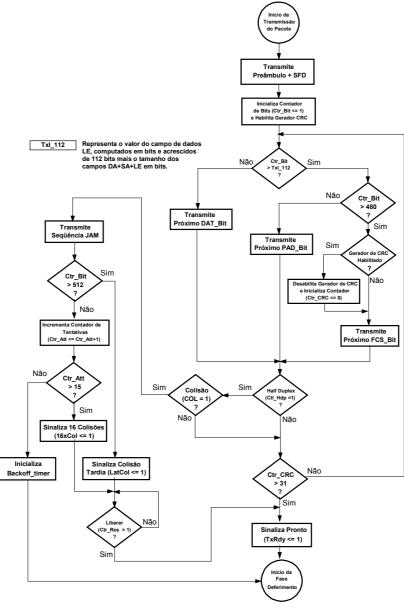

| Figura 5.6 – Fluxograma da fase de transmissão.                                                           | 60  |

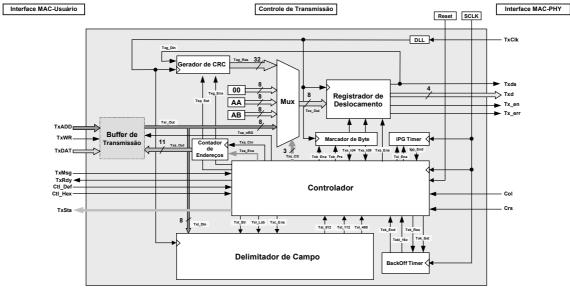

| Figura 5.7 – Diagrama de blocos do controle de transmissão do IP Soft Core MAC Ethernet.                  | 62  |

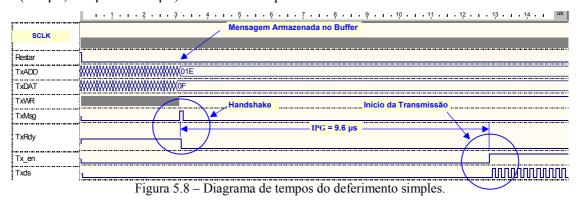

| Figura 5.8 – Diagrama de tempos do deferimento simples.                                                   | 62  |

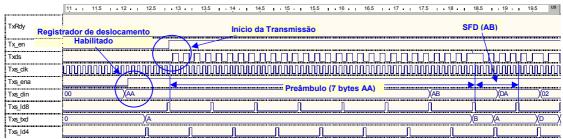

| Figura 5.9 – Diagrama de tempos do início da transmissão, preâmbulo e SFD.                                | 63  |

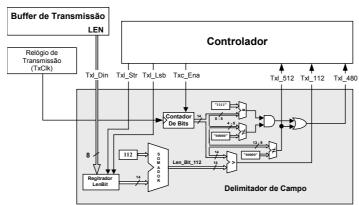

| Figura 5.10 - Diagrama de blocos do delimitador de campo do módulo de transmissão                         | 63  |

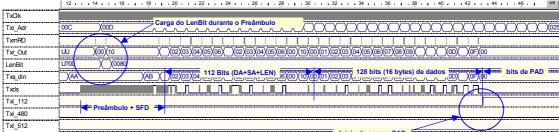

| Figura 5.11 – Diagrama de tempos da carga do registrador LenBit.                                          | 64  |

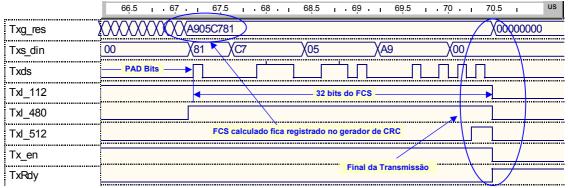

| Figura 5.12 – Diagrama de tempos do final da transmissão: final do campo PAD, transmissão do FCS e libera | ção |

| do buffer de transmissão                                                                                  | 64  |

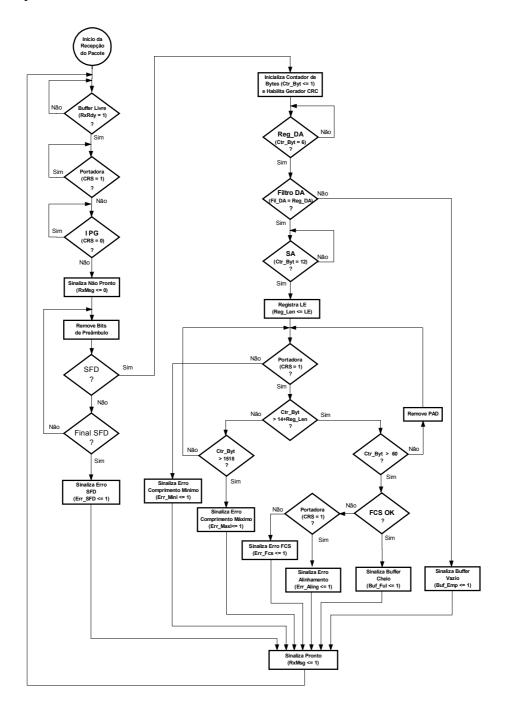

| Figura 5.13 – Diagrama de fluxo do módulo receptor.                                                       | 66  |

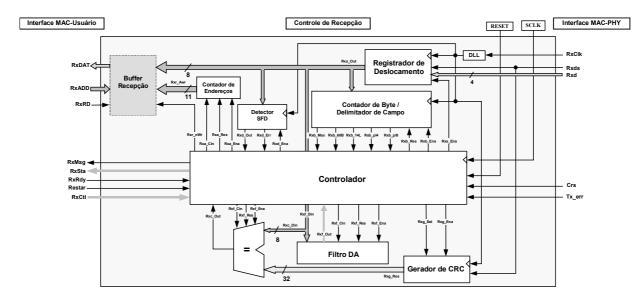

| Figura 5.14 - Diagrama de blocos do módulo de recepção do IP Core MAC Ethernet.                           | 68  |

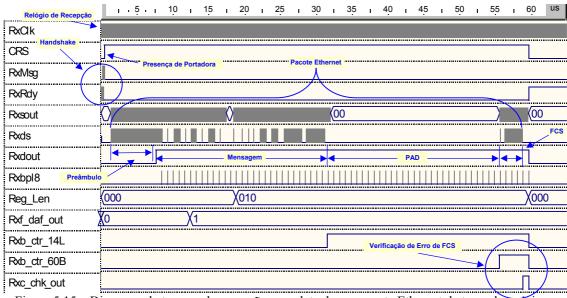

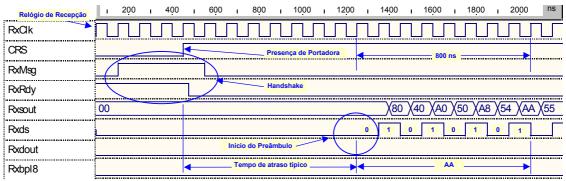

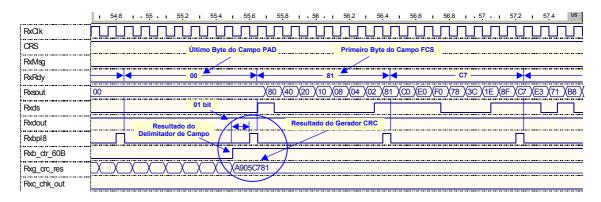

| Figura 5.15 – Diagrama de tempos da recepção completa de um pacote Ethernet de tamanho mínimo             | 68  |

| Figura 5.16 – Diagrama de tempos do início da recepção.                                                   | 69  |

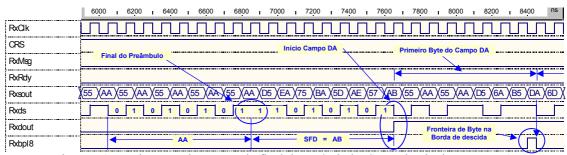

| Figura 5.17 – Diagrama de tempos do final do preâmbulo, SFD e início do campo DA.                         | 69  |

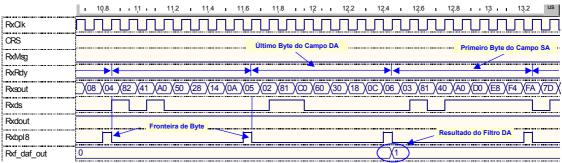

| Figura 5.18 – Diagrama de tempos do final do campo DA, resultado do filtro DA e início do campo SA        | 70  |

| Figura 5.19 – Diagrama de tempos do final do campo SA, armazenamento do campo LE no registrador Reg_l     | Len |

| e início do campo DF.                                                                                     | 70  |

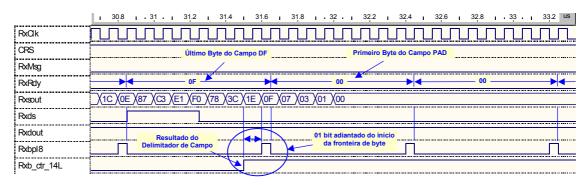

| Figura 5.20 – Diagrama de tempos do final do campo DF, resultado do delimitador de campo e início do can  | npo |

| PAD                                                                                                       | 71  |

| Figura 5.21 – Diagrama de tempos do final do campo PAD, resultado do delimitador de campo e início        | ) do |

|-----------------------------------------------------------------------------------------------------------|------|

| campo FCS.                                                                                                | 71   |

| Figura 5.22 - Diagrama de tempos do resultado do CRC gerado comparado com os bytes do FCS e término       | o da |

| recepção                                                                                                  | 72   |

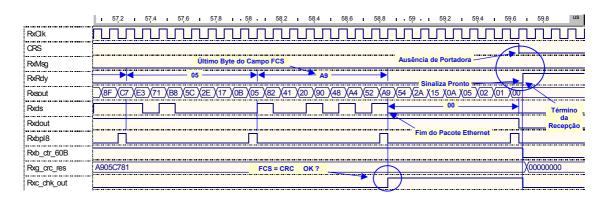

| Figura 6.1 – Diagrama de blocos do método testbench.                                                      | 73   |

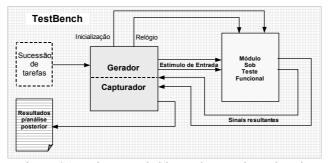

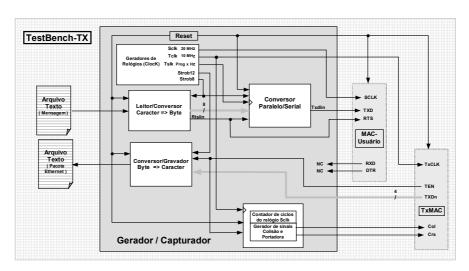

| Figura 6.2 – Diagrama de blocos do TestBench_TX na fase de validação do TxMAC.                            | 75   |

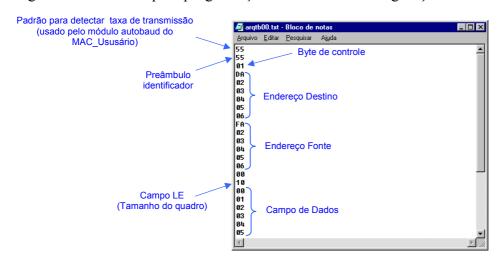

| Figura 6.3 – Arquivo texto com a mensagem a ser transferida                                               | 75   |

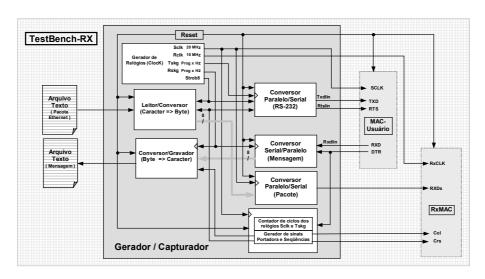

| Figura 6.4 – Diagrama de blocos do módulo Gerador/Capturador doTestbench-TX.                              | 76   |

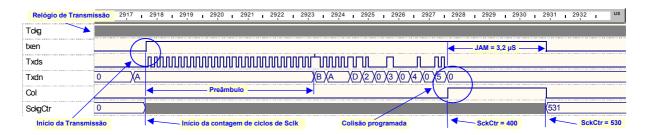

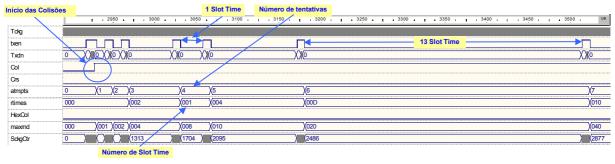

| Figura 6.5 – Diagrama de tempos da simulação de colisão.                                                  | 76   |

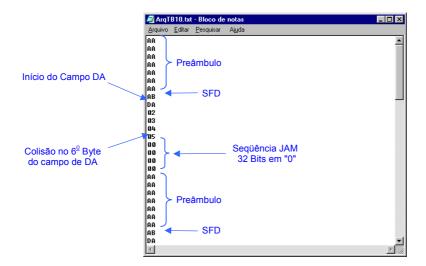

| Figura 6.6 – Arquivo texto com pacote transmitido e retransmitido após colissão.                          | 77   |

| Figura 6.7 – Diagrama dos seis primeiros tempos de espera aleatória exponencial truncada                  | 77   |

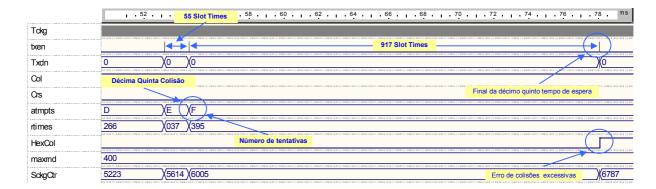

| Figura 6.8 – Diagrama dos dois últimos tempos de espera aleatória exponencial truncada.                   | 78   |

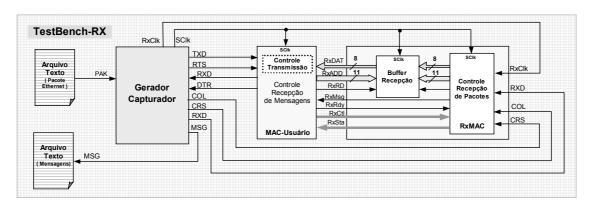

| Figura 6.9 – Diagrama de blocos do TestBench-RX na fase de validação do RxMAC                             | 78   |

| Figura 6.10 – Diagrama de blocos do módulo Gerador/Capturador do TestBench-RX.                            | 79   |

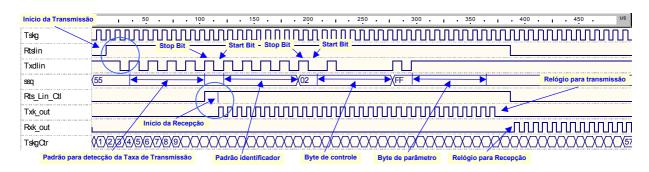

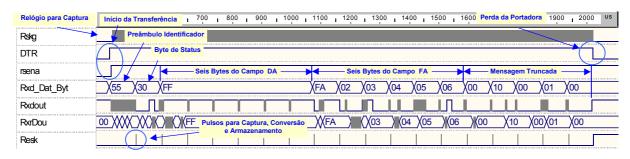

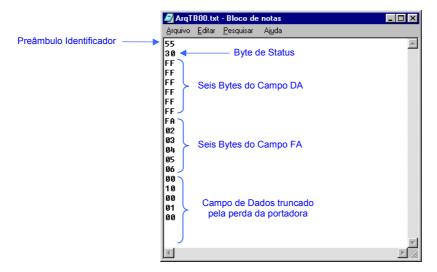

| Figura 6.11 – Diagrama de tempos da simulação da transmissão de inicialização do módulo MAC-Usuário       | 80   |

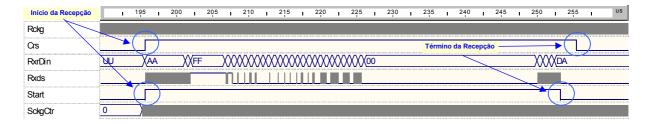

| Figura 6.12 – Diagrama de tempos da recepção do pacote pelo RxMAC.                                        | 80   |

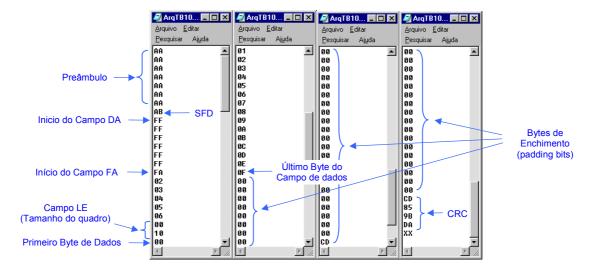

| Figura 6.13 – Arquivo texto com o pacote Ethernet a ser recebido pelo RxMAC                               | 80   |

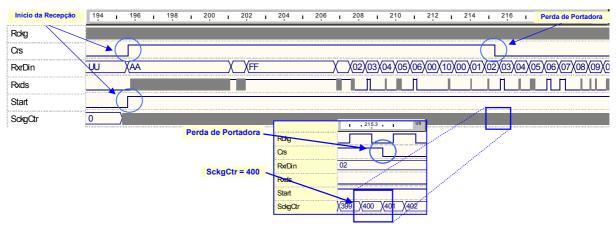

| Figura 6.14 – Diagrama de tempos na recepção do pacote pelo RxMAC com perda de portadora                  | 81   |

| Figura 6.15 – Diagrama de tempos da tranferência do byte de status e a mensagen truncada                  | 81   |

| Figura 6.16 – Arquivo texto com a mensagem (truncada) armazenada pelo módulo Gerador/Capturador           | 82   |

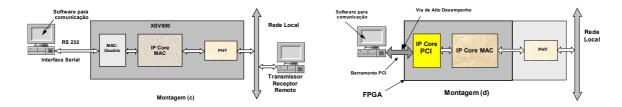

| Figura 7.1 – Diagrama de blocos mostrando o ambiente típico de emprego do IP core desenvolvido            | 84   |

| Figura 7.2 – Diagrama de blocos da Interface MAC-Usuário.                                                 | 86   |

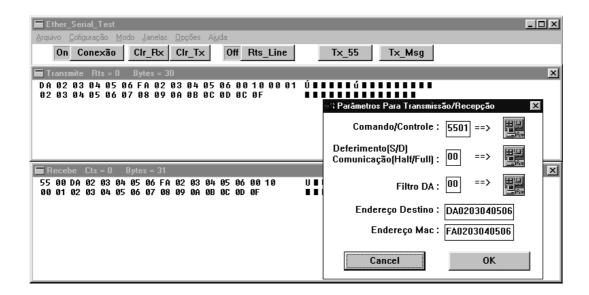

| Figura 7.3 – Tela mostrando a execução do software de interação entre o hospedeiro (PC) e o protótipo do  | o IP |

| Core MAC Ethernet                                                                                         | 88   |

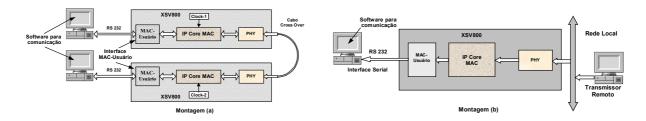

| Figura 7.4 – Duas montagens de validação do protótipo do IP Core MAC Ethernet. (a) Valida transmissã      | ão e |

| recepção internamente ao projeto. (b) Valida recepção em rede local real com estação ren                  | nota |

| transmitindo quadros para o protótipo com grande espaçamento entre estes.                                 | 88   |

| Figura 7.5 - Duas outras montagens de validação do protótipo do IP core MAC Ethernet. (c) Valida transmis | ssão |

| e recepção em rede local real com estação remota transmitindo quadros para o protótipo o                  | com  |

| grande espaçamento entre estes. (d) Plataforma com IP core Ethernet combinado com IP co                   | core |

| PCI para implementar via de alto desempenho.                                                              | 89   |

# LISTA DE TABELAS

| Tabela 2.1 – Três classificações de IP cores baseado em quatro critérios.                          | . 17 |

|----------------------------------------------------------------------------------------------------|------|

| Tabela 3.1 - Classificação de arquiteturas reconfiguráveis baseadas nos novos critérios propostos. | .32  |

| Tabela 7.1 – Parâmetros de comando para transmissão e recepção via interface serial                | .87  |

#### LISTA DE ABREVIATURAS

ADCCP Advanced Data Communication Control Proceedings

AMBA Advanced Microcontroller Bus Architecture

AMD Advanced Micro Devices

ANSI American National Standards Institute

API Application Program Interface (Hardware Object Technology)

**SA** Source Address

ASP Application Specific Processor

ATM Asynchronous Transfer Mode

AUI Attachment Unit Interface

BLE Basic Logic Element

BRAM Block Random Access Memory

BSC Binary Synchronous Protocol (IBM)

**CAM** Content Addressable Memory

CCITT Comité Consultatit International Télégraphique et Téléphonique

CCITT Consultative Committee for International Telegraph and Telephone

**CCM** Configuration Cache Manager

CI Circuito Integrado

**CLB** Configurable Logic Block

**CMOS** Complementary Metal Oxide Semiconductor

**CRC** Cyclic Redundancy Check

**CSI** Configurable System Interconnect Bus

**CSMA-CD** Carrier Sense Multiple Acess with Collision Detection

**DA** Destination Address

**DDCMP** Digital Data Communications Message Protocol (DEC)

**DEC** Digital Equipment Corporation

**DEC PRL** Paris Research Lab Digital Equipment Corporation

**DF** Data Field

**Dip** Dual In Line Package

**DISC** Dynamic Instruction-Set Computer

**DIX** Digital Equipment Corporation/Intel Corporation/Xerox Corporation

DLL Delay Locked LoopDMA Direct Memory AccessDNA Desoxiribonucleic Acid

**DPGA** Dynamically Programmable Gate Array

**DQDB** Distributed Queue Dual Bus

**EAB** Embedded Array Block

**EEPROM** Electrically Erasable Programmable ROM

**EIA** Electronic Industries Association

**EPROM** Erasable Programmable ROM

**ESB** Embedded System Block

**FB** Function Block

FCS Frame Check Sequence

**FIFO** First-In-First-Out

FPLD Field-Programmable Gate Array

FPLD Field Programmable Logic Device

FSM Finite State Machine

FTP File Transfer Protocol

GPP General Purpose Processor

GRM General Routing Matrix

**HDLC** High Level Data Link Control

IBM International Business Machines

IEEE Institute of Electrical and Electronic Engineers

IOB Input-Output BlockIP Intellectual Property

IP Core Intellectual Property Core

IPG Inter Packet Gap

ISA Industry Standard Architecture

ISO International Standards Organization

ISP Instruction Set Processor

JTAG Joint Test Action Group

LAB Logic Array Block

LAN Local Area Network

**LE** Logic Element

LED Light Emitting Diode

LLC Logical Link Control

LSB Least Significant Bit

LUT Look-Up Table

**LVDS** Low Voltage Differential Signaling

MAC Medium Access Control

MAN Metropolitan Area Network

MIPS Millions of Instructions Per Second

MOS Metal Oxide Semiconductor

MPGA Mask-Programmable Gate Array

NIC Network Interface Controller/Card

NTSC National Television Standards Committee

ONO Oxygen-Nitrogen-Oxygen

OSI Open Systems Interconnect

OSI-RM Open Systems Interconnect Reference Model

PAL Programmable Array Logic

**PAM** Programmable Active Memory

PCI Peripheral Component Interconnect

PLS Phase Locked Loop

PLS Physical Signaling

**PRISM** Processor Reconfiguration through Instruction-Set Metamorphosis

**PROM** Programmable Read Only Memory

PSM Programmable Switch Matrix

RAM Random Access Memory

RAMDAC Random Access Memory Digital Analog Converter

**RENCO** Reconfigurable Network Computer

RGB Red-Green-Blue

ROM Read Only Memory

RPC Remote Procedure Call

SDLC Synchronous Data Link Control

**SECAM** Séquentielle Couleur Avec Mémoire

SERDESSerializer/DeserializerSFDStart Frame DelimiterSLISystem-Level Integration

**SMTP** Simple Mail Transfer Protocol

SOC System-On-a-Chip

SORCSystem-on-a-Reconfigurable ChipSRAMStatic Random Access MemorySRCSupercomputing Research Center

**USB** Universal Serial Bus

**Utopia** Universal Test & Operations PHY Interface for ATM

VCC Virtual Computer Corporation

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

**VLSI** Very Large Scale Integration

VME Versa Module Europa

VSB VME Subsystem Bus

WAN Wide Area Network

WWW World Wide Web

#### **RESUMO**

Este trabalho descreve as estratégias de projeto e validação de um Núcleo de Propriedade Intelectual (IP Soft Core) destinado a desempenhar o papel de protocolo de Controle de Acesso ao Meio para redes locais do tipo Ethernet. O projeto deste IP Soft Core foi completamente implementado na linguagem VHDL, sendo assim flexível, portável e personalizável para aplicações específicas. A implementação foi especialmente desenvolvida para adaptar-se bem a ambientes onde o IP Core reside em dispositivos de hardware reconfigurável tais como FPGAs baseados em RAM. Também se descreve aqui a estratégia de validação funcional do projeto do IP Core Ethernet em detalhe. Finalmente, o trabalho introduz uma proposta para vários ambientes de validação, mediante uso de plataformas de prototipação rápida comerciais, visando testar e caracterizar completamente o IP Soft Core Ethernet em redes locais reais.

Palavras-chave - Redes de Computadores, redes locais, LAN, Ethernet, dispositivos reconfiguráveis, sistemas digitais, FPGAs, modelo de referência OSI, protocolo de acesso ao meio, MAC, IP Core, Soft Core.

#### **ABSTRACT**

This work describes the design and validation strategies for an Intellectual Property (IP) Soft Core deemed to fulfill the role of Medium Access Control protocol for Ethernet local area networks. The design of the IP Core was implemented in the VHDL language, being thus flexible, portable and customizable to specific applications. The implementation was specifically developed to fit in environments where the IP Core resides in reconfigurable hardware devices like RAM-based FPGAs. The functional validation strategy of the Ethernet IP Soft Core using commercial reconfigurable boards is described in detail. Finally, the work introduces a proposal for several validation environments, in order to fully test and characterize the Ethernet IP Soft Core in real world local networks.

Keywords – Computer networks, local networks, LAN, Ethernet, reconfigurable devices, digital systems, FPGAs, OSI reference model, medium access protocol, MAC, IP Core, Soft Core.

## 1. Introdução

Provavelmente, o grande avanço na primeira metade do século XX foi a introdução de sistemas computadores como um novo recurso para geração e troca de informações. O computador e a comunicação através de sinais elétricos, que na época alcançava considerável evolução, veio revolucionar o mundo em que vivemos. Da conjunção destas duas tecnologias surgiu uma nova forma de comunicação entre pessoas e até mesmo entre máquinas. Com esta nova forma de comunicação, nasce o conceito de *rede de computadores*, que atualmente é definido por um conjunto de módulos processadores capazes de trocar informações e compartilhar recursos interligados por um sistema de comunicações [SOA95].

Dentro deste novo contexto, a diversificação das atividades e recursos cresceu, passou-se a considerar o uso das redes de computadores como um meio para distribuir com maior eficácia a utilização informações espalhadas por todo planeta. Quando a distância entre os módulos processadores estão na faixa de metros até alguns poucos quilômetros, as redes de computadores são denominadas de Redes Locais (Local Area Networks – LANs). Redes locais surgiram, assim, para viabilizar a troca e o compartilhamento de informações e dispositivos periféricos, preservando a independência das várias estações ou módulos processadores, e permitindo a integração em ambientes de trabalho cooperativo [SOA95]. Quando a distância de ligação entre os vários módulos processadores atinge distâncias metropolitanas, as redes de computadores são denominadas de Redes Metropolitanas (Metropolitan Area Networks – MANs). Por outro lado, as Redes de Longo Alcance (Wide Area Networks – WANs) surgiram da necessidade de se compartilhar recursos especializados por uma maior quantidade de usuários geograficamente dispersos [SOA95]. Por terem um custo associado dos seus meios de comunicação bastante elevado, tais redes são em geral públicas, isto é, o sistema de comunicação é mantido, gerenciado e de propriedade de grandes operadoras. Como exemplo temos a rede mundial de computadores, a *Internet*, que interliga redes da maioria dos países, oferecendo uma série de recursos, tais como: o protocolo de transferência de arquivos (FTP), o correio eletrônico e as "páginas" da internet.

Diversas tecnologias para a implementação de redes locais foram desenvolvidas e/ou estão em desenvolvimento. Exemplos são as redes *ATM* (modo de transferência assíncrono), *Token Ring* (passagem de permissão em anel), *Token Bus* (passagem de permissão em barra) e *CSMA/CD* (acesso múltiplo por sensoriamento de portadora e detecção de colisões). Todas estas tecnologias constituem-se como protocolos de acesso ao meio ou *MAC* (em inglês, Medium Access Control).

Uma das tecnologias habilitadoras de redes de computadores são os protocolos de comunicação de equipamentos fisicamente conectados, tais como o protocolo *Ethernet* [MET76]. O protocolo Ethernet foi projetado para transferência de dados em alta velocidade, limitado a pequenas distâncias. Atualmente, a tecnologia Ethernet é aplicada nas redes locais, que são redes de computadores restritas a uma sala, um prédio ou uma corporação. Redes Ethernet não têm tamanho físico determinado, porém seu alcance é restrito ao local de operação. Assim, embora possam interligar, em tese, qualquer quantidade e computadores, normalmente um número limitado provê melhor desempenho na comunicação. Este protocolo surgiu no ambiente de institutos de pesquisa e universidades, com o objetivo de viabilizar a troca e o compartilhamento de informações e dispositivos periféricos (recursos de hardware e software), permitindo a integração em ambientes de trabalho cooperativo [SOA95]. O protocolo CSMA/CD é a base do protocolo Ethernet.

Observando-se as diferentes aplicações que utilizam redes locais, percebemos a grande importância dos *controladores* utilizados nestas redes. Atualmente, grande parte destes controladores são baseados na tecnologia Ethernet. Esta tecnologia tornou-se um padrão internacional e a partir deste

padrão foram desenvolvidos módulos de hardware em dispositivos eletrônicos específicos, para executarem as funções necessárias aos controladores de redes.

Há uma tendência no desenvolvimento de módulos de hardware reutilizáveis e portáveis a diferentes tecnologias de implementação, que permitam a rápida construção de sistemas digitais, denominados por *Núcleo de Propriedade Intelectual* reutilizável (do inglês, Intellectual Property core, ou IP core). Estes módulos de hardware reutilizáveis são desenvolvidos em *dispositivos reconfiguráveis*. Os dispositivos reconfiguráveis, conhecidos como *FPLDs* (Dispositivos Lógicos Programáveis no campo, em inglês, *Field Programmable Logic Devices* ou *FPLDs*), são componentes eletrônicos digitais cujo comportamento pode ser definido pelo usuário após a fabricação, num processo denominado *configuração*. Estes componentes habilitam a construção de sistemas digitais eletrônicos de uma forma mais flexível. Isto é devido à característica de reconfigurabilidade, que permite resolver, em alguns casos de forma mais eficiente, os problemas encontrados no desenvolvimento e implementação de um sistema digital.

#### 1.1 Objetivos

Motivado pela crescente importância da tecnologia de redes locais e da rápida evolução de dispositivos com características de reconfigurabilidade, propõe-se aqui o projeto e a prototipação do protocolo de acesso ao meio em redes Ethernet, sob forma de um núcleo processador de propriedade intelectual reutilizável. Este núcleo processador executará parte do protocolo de comunicação em uma rede local de tecnologia Ethernet.

O presente trabalho teve como objetivo estratégico dominar a tecnologia de implementação de controladores de redes Ethernet, concentrando-se nos níveis inferiores de abstração (hardware e software básico mínimo). Ênfase foi colocada, como indicado no título do trabalho, no projeto e prototipação de protocolos de acesso ao meio em redes Ethernet usando como estudo de caso o MAC Ethernet. Para tal, os objetivos específicos alocados ao longo desenvolvimento deste controlador consistiram em:

- Projetar e validar a parte fundamental de um controlador de rede local para o padrão Ethernet, endereçando procedimentos de software e hardware no nível de enlace do modelo OSI-RM¹;

- 2. Implementar um controlador baseado no módulo mencionado no item anterior sobre componentes reconfiguráveis em uma plataforma de prototipação escolhida, fazendo-a interagir com um computador hospedeiro e com uma rede local;

- 3. Disponibilizar o módulo resultante sob forma de um núcleo processador de propriedade intelectual do tipo Soft (IP Soft Core) reutilizável;

- 4. Prover subsídios para efetuar migrações entre software e hardware dos módulos em questão, com o intuito de maximizar desempenho e/ou minimizar custos dos sistemas digitais e respectivo software.

#### 1.2 Motivação

As justificativas para empreender o presente trabalho, malgrado a disponibilidade de circuitos integrados (CIs) comerciais que desempenham a função de controle de acesso ao meio Ethernet, e até mesmo de outros trabalhos de pesquisa [FRA00] e desenvolvimentos comerciais já possuem disponíveis IP Soft Cores deste tipo, são múltiplas. Além dos benefícios acadêmicos de dominar

<sup>1</sup> O modelo OSI-RM é apresentado em mais detalhes no Capítulo 4.

uma tecnologia importante na área estratégica de transmissão de dados, existem benefícios potenciais para empresas nacionais usuárias da tecnologia Ethernet. Para estas, o custo de CIs em geral, e controladores para Ethernet é relativamente alto. Além disso, os CIs comerciais são inflexíveis quanto às funções que podem desempenhar, ou seja, funções a mais não podem ser acrescentadas, exceto pela adição de outros CIs ao sistema, e funções desnecessárias presentes no CI não podem deste ser removidas. O desenvolvimento de um IP Soft Core para a camada MAC Ethernet remove a inflexibilidade dos CIs comerciais, permitindo adaptar o hardware ao subconjunto de funções estritamente necessárias no produto que o emprega, melhorando a relação custo benefício de produtos tecnológicos. Por outro lado, o acesso à tecnologia de implementação de IP cores Ethernet permite, por exemplo, liberar empresas da necessidade de importar parte dos insumos de seus produtos, aumentando a competitividade destes produtos num mercado globalizado.

#### 1.3 A Estrutura do Volume

O presente trabalho está estruturado em três partes. A primeira parte, contituida dos Capítulos 2 e 3, mostra um estudo do estado da arte de dispositivos e arquiteturas reconfiguráveis, apresentando os conhecimentos necessários para a prototipação do IP Soft Core. Na segunda parte, que envolve os Capítulos 4 e 5, introduz-se o Modelo de Referência OSI-RM da ISO, e estuda-se redes locais Ethernet. Na continuação da segunda parte, o Capítulo 5 apresenta o projeto IP Soft Core para o MAC Ethernet, descrevendo sua estrutura e a funcionalidade dos módulos básicos. Na terceira parte, que consiste nos Capítulos 6 ,7 e 8, apresenta-se, no Capítulo 6, a estratégia de validação funcional do projeto IP Soft Core. No Capítulo 7, mostra-se detalhes do processo de prototipação e uma proposta de ambientes de teste sugeridos para prototipação do núcleo processador de propriedade intelectual. Finalmente, o Capítulo 8 apresenta algumas conclusões e sugere trabalhos futuros.

## 2. Hardware Reconfigurável

#### 2.1 Introdução

Muitas aplicações computacionais necessitam alteração freqüente de sua funcionalidade ou grande flexibilidade de comportamento. Isto é atualmente possível não apenas via implementação em software, mas também em hardware, graças à existência de dispositivos de hardware reconfigurável.

No caso de implementações em software existe um hardware subjacente normalmente composto por um processador de conjunto de instruções (em inglês, *instruction set processor* ou ISP) associado a uma memória. ISPs podem ser programados para executar uma ou mais aplicações específicas preenchendo a memória de instruções com software que implementa as aplicações.

No caso de implementação em hardware, as aplicações flexíveis são obtidas principalmente através de uso de dispositivos tais como FPGAs. De fato, os FPGAs modificaram a tradicional distinção entre hardware e software, visto que sua funcionalidade em hardware pode ser alterada de forma total ou parcial ou até mesmo dinâmica.

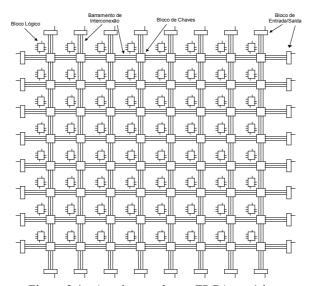

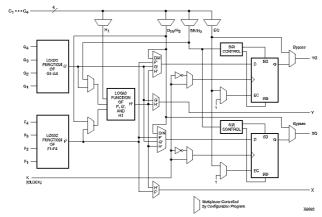

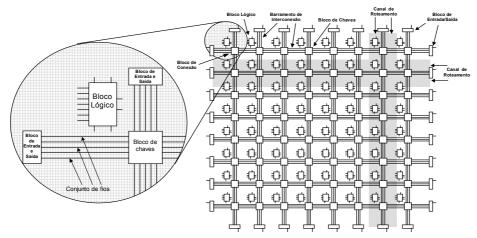

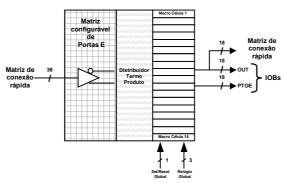

A arquitetura genérica de FPGAs, ilustrada pela Figura 2.1, consiste em uma matriz de elementos agrupados em *blocos lógicos* configuráveis, que podem ser interconectados, por *barramentos de interconexão* configuráveis. Semelhante a uma PAL (*Programmable Array Logic*), as interconexões entre os elementos são implementadas por *blocos de chaves* configuráveis pelo usuário. Através de *blocos de entrada/saída* configuráveis é realizado o interfaceamento com o mundo externo. Os FPGAs foram introduzidos em 1985 pela empresa Xilinx. Desde então, grande variedade de FPGAs foi desenvolvida por várias outras companhias, entre elas: Actel, Altera, Atmel, Plessey, Plus Logic, Advanced Micro Devices (AMD), Quicklogic, Algotronix, Concurrent Logic, e Crosspoint Solutions.

Figura 2.1 - Arquitetura de um FPGA genérico.

Nas Seções seguintes são apresentadas as formas de configurar FPGAs, as arquiteturas de blocos lógicos e de roteamento, bem como as noções de granularidade, densidade e desempenho de FPGAs. Apresenta-se também a definição de Núcleos de Propriedade Intelectual e uma visão do estado da arte em FPGAs.

#### 2.2 Formas de Configurar FPGAs

Em um FPGA, a matriz de blocos lógicos é configurada e interconectada eletricamente através de chaves eletrônicas configuráveis. As propriedades destas chaves, tais como tamanho, resistência (em ohms), e capacitância (em farads), delimitam as características elétricas destes circuitos integrados. Nas três seções a seguir serão descritas as tecnologias de chaves mais comumente utilizadas [ROS93].

#### 2.2.1 Tecnologia de Configuração SRAM

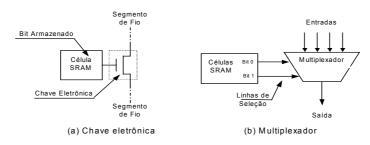

A tecnologia SRAM (*Static Random Access Memory*) usa bits de memória RAM estática para programar e controlar as chaves eletrônicas, baseadas em transistores de tecnologia CMOS (*Complementary Metal Oxide Semiconductor*) ou multiplexadores como ilustra a Figura 2.2.

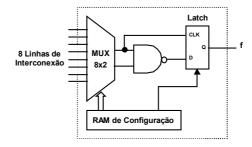

Figura 2.2 – Duas opções de tecnologia de configuração de FPGAs.

Quando um bit é armazenado na célula SRAM vista na Figura 2.2(a), a chave eletrônica funciona como um circuito aberto ou fechado, conforme o valor lógico ("0" ou "1") do bit armazenado. Desta forma a chave é usada para fazer uma conexão entre dois segmentos de fio. Quando um "0" é armazenado, a chave está aberta, e o transistor apresenta uma resistência que tende ao infinito, a qual impede a conexão entre os dois segmentos.

No caso de multiplexador, (Figura 2.2(b)), as saídas das células SRAM estão conectados às linhas de seleção, escolhendo uma das entradas do multiplexador para ser conectada à saída. Considerando que a SRAM é volátil, o FPGA deverá ser configurado a cada vez que for alimentado. Isto exige uma memória externa permanente como PROM, EPROM, EEPROM ou outro meio de armazenamento, para prover o vetor de configuração.

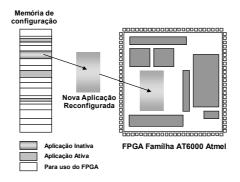

A tecnologia SRAM é usada em dispositivos da Xilinx [XIL99], Plessey [PLE89], Algotronix [ALG89], Altera [ALT01a], Concurrent Logic [CON91], Toshiba [MUR91] e Atmel [ATM99].

A necessidade de uma grande área na pastilha de silício que compõe o circuito integrado FPGA é a maior desvantagem da tecnologia de programação SRAM. Consome-se cinco transistores para implementar uma célula de SRAM e um transistor para a chave programável. Porém, esta tecnologia tem duas vantagens importantes, a reconfigurabilidade rápida e ilimitada devida às características das SRAMs e a possibilidade de utilizar um processo relativamente simples de fabricação do circuito integrado.

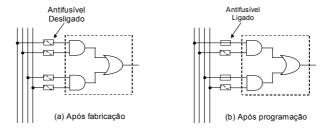

#### 2.2.2 Tecnologia de Configuração Antifusível

Um *antifusível* é um dispositivo que apresenta uma resistência muito alta entre seus terminais. Quando uma tensão de 11 a 20 volts (dependendo do tipo de antifusível) é aplicada entre de seus terminais, o antifusível "queima," criando uma ligação de baixa de resistência (contrário ao fusível

convencional que se interrompe), tornando esta ligação permanente, conforme ilustrado na Figura 2.3.

Figura 2.3 - Tecnologia de programação antifusível.

A programação de um antifusível requer um circuito extra para fornecer a tensão de configuração e uma corrente de 5 mA ou mais. Isto é uma desvantagem, pois exige transistores de maior potência para prover a queima de cada antifusível. Uma vantagem do antifusível é seu tamanho pequeno em relação a componentes de outras tecnologias de configuração. Outra é sua resistência série relativamente baixa e uma pequena capacitância parasita (para o antifusível não configurado), significativamente mais baixa que em outras tecnologias de configuração. Dois tipos de antifusíveis são mais utilizados, os fabricados pelo processo Oxigênio-Nitrogênio-Oxigênio (ONO) e o de Silício amorfo. A tecnologia de antifusível é usada nos dispositivos FPGAs da Actel [GAM89], Quicklogic [BIR91] e Crosspoint [MAR92].

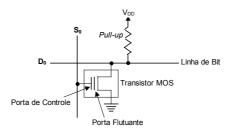

#### 2.2.3 Tecnologia de Configuração de Porta Flutuante

Esta tecnologia é baseada em configuração por armazenamento de cargas, da mesma forma que utilizada nas memórias EPROM (*Erasable Programmable ROM*), EEPROM (*Electrically Erasable Programmable ROM*) e Flash RAMs. Cada bit da memória, conforme ilustra a Figura 2.4, possui um transistor MOS (*Metal Oxide Semiconductor*) com duas portas, uma delas flutuante, não conectada ao barramento da memória (S<sub>0</sub>) e isolada por material de alta impedância.

Figura 2.4 - Tecnologia de programação porta flutuante.

Em estado "desligado", como são fabricados, esses transistores não conduzem quando selecionados (via linha  $S_0$ ) e o conteúdo das posições de memória (via linha  $D_0$ ) é levado a "1" por resistores de *pull-up*. Para gravar um valor "0" em determinada posição, aplica-se uma tensão elevada, entre a porta de controle (não flutuante) e o dreno, o que causa uma ruptura no material isolante e permite o acúmulo de cargas na porta flutuante, as quais permanecem, mesmo após o término do pulso de tensão, devido à alta impedância do material isolante. A presença dessas cargas na porta flutuante mantém o transistor em condução quando a posição daquele bit for selecionada. Com isso, a linha de bit é levada para "0". Estas cargas podem ser removidas da porta flutuante expondo o componente à luz ultravioleta, desfazendo-se desta forma a configuração.

Como no caso de uso de SRAM, a vantagem principal da tecnologia de porta flutuante é sua reconfigurabilidade. Entretanto, esta tecnologia tem uma vantagem a mais, não é necessária memória externa permanente para programação do conjunto de bits de configuração no momento da

inicialização. Porém, a tecnologia de construção de dispositivos de porta flutuante requer três passos a mais do que o processo usual de fabricação CMOS. Duas outras desvantagens são: a alta resistência do transistor quando no estado de condução, e o alto consumo de energia devido ao resistor de *pull-up*, que é conectado à fonte de alimentação do dispositivo FPGA.

A tecnologia de porta flutuante baseada em EEPROM é usada em dispositivos fabricados pela AMD [AMD90], Lattice [BAK91] e Altera [WON89]. Esta tecnologia é semelhante a das EPROMs, a não ser pela remoção das cargas da *porta flutuante*, que pode ser feita eletricamente, no circuito, sem luz ultravioleta. Isto dá uma vantagem a mais, a fácil e mais rápida reconfigurabilidade, que pode ser muito útil em algumas aplicações. Porém, existe uma desvantagem, a célula de EEPROM é aproximadamente duas vezes o tamanho de uma célula de EPROM.

Desenvolvimentos de transistores MOS com base na tecnologia "double-poly silicon" habilitaram o uso de memórias eletricamente apagáveis com células de tamanho equivalente às EPROMs. A velocidade de acesso destes novos dispositivos de memória também é comparável com o desempenho de EPROMs CMOS, com tempos de acesso na ordem de 110 ns [KYN88]. Estes novos dispositivos de memória são denominados de *RAM Flash*. A tecnologia RAM Flash utiliza o processo de fabricação *CMOS Flash*, derivada do mesmo processo padrão das EPROMs CMOS. Por exemplo, a tecnologia FastFLASH, com espessura característica de 0,35 micron, utilizada no dispositivo FPGAs XC9500XL da Xilinx [XIL00], proporciona maior resistência na retenção da configuração (estimada em 20 anos) e uma durabilidade na ordem de 10 000 ciclos de configurações.

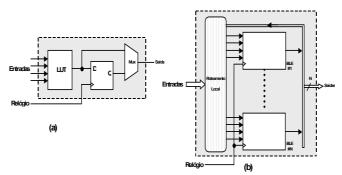

### 2.3 Arquiteturas de Blocos Lógicos

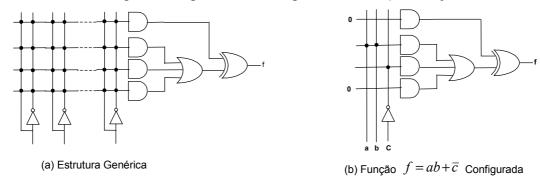

Uma definição possível para o *bloco lógico* é uma estrutura complexa contendo vários circuitos combinacionais, de múltiplas entradas e uma ou mais saídas. A maioria dos blocos lógicos também contém algum tipo de dispositivo de armazenamento, para viabilizar a implementação de circuitos seqüenciais. A Figura 2.5 ilustra exemplos de blocos lógicos.

Figura 2.5 - Exemplos das estruturas de blocos lógicos.

Como ilustram os exemplos da Figura 2.5, em alguns FPGAs os blocos lógicos possuem estrutura bastante simples, tal como um multiplexador e uma porta NAND de duas entradas. Em outros, são uma estrutura bem mais complexa, tais como tabelas verdade de 3, 4 ou 5 entradas, denominadas de *look-up tables* (LUTs) e outros módulos. Em alguns FPGAs, um bloco lógico configurável corresponde a uma estrutura semelhante a uma PAL (Programmable Array Logic) [BOS96].

Uma LUT de *n* entradas é implementada como um registrador com 2<sup>n</sup> biestáveis e um esquema de seleção de um dos bits deste registrador para colocar na saída. O controle desta seleção é realizado pelas variáveis de entrada da função, como ilustrado na Figura 2.6 para o caso de LUTs de 3 variáveis. Este tipo de bloco lógico possui dimensão relativamente elevada, mas fornece a máxima

flexibilidade, muito maior que a dos blocos implementados com lógica de dois níveis ou com multiplexadores.

Figura 2.6 - LUT para tabelas de 3 variáveis, implementando a função  $f = ab + \overline{c}$ .

Rose, em [ROS93], observa que os blocos lógicos em FPGAs, como ilustra a Figura 2.7, diferem em tamanho e capacidade de implementação. O bloco lógico de dois transistores usado no FPGA da Crosspoint [MAR92], pode implementar apenas um inversor, porém é muito pequeno em tamanho, enquanto que o bloco lógico implementado com LUTs, usado nos FPGAs da Xilinx série 3000 pode implementar qualquer função lógica de até cinco variáveis, mas é significativamente maior em tamanho.

Figura 2.7 - Blocos lógicos (a) Crosspoint e (b) Xilinx série 3000.

Observando as diferentes estruturas que constituem os blocos lógicos, Rose [ROS93] classifica as arquiteturas dos FPGAs pela sua granularidade. *Granularidade* é um termo que pode ser definido usando vários critérios. Exemplos de critérios são o número de funções booleanas que o bloco lógico pode implementar, o número equivalente de portas NAND de duas entradas, o número total de transistores, o total de área normalizada, ou o número de entradas e saídas.

O assunto da granularidade da arquitetura FPGA é bastante complexo, porque em algumas arquiteturas, tais como a dos FPGAs Altera [WON89] ou a dos FPGAs AMD [AMD90], a lógica e o roteamento estão fortemente mesclados e é difícil separar as diferentes características de granularidade. Para simplificar, Rose escolhe classificar a granularidade das arquiteturas comerciais em duas categorias: grão pequeno e grão grande. Ver-se-á a seguir sua proposta de classificação de arquiteturas de FPGAs.

#### 2.3.1 Arquiteturas de Grão Pequeno

O FPGA fabricado pela Crosspoint [MAR92], por exemplo, usa um único par de transistores no bloco lógico, como ilustrado na Figura 2.7(a). A função  $f = ab + \overline{c}$  é implementada com pares de transistores conforme mostrado na Figura 2.8. Considerando que os transistores são conectados lado

a lado, alternando filas de transistores P e transistores N, portas lógicas CMOS quaisquer podem ser configuradas, bastando desligar um par de transistores nos seus limites laterais para criar uma região de isolamento entre portas adjacentes.

Figura 2.8 - FPGA Crosspoint configurado para a função  $f = ab + \overline{c}$  implementando  $f = \overline{ab.c}$ .

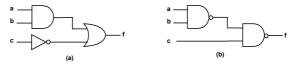

Um segundo exemplo de uma arquitetura de grão pequeno é o FPGA ERA60100 da Plessey Semiconductor [PLE89]. Neste, o bloco básico é uma porta NAND de duas entradas como ilustrado na Figura 2.9. A lógica é formada do modo habitual, conectando-se as entradas da NAND por meio de um multiplexador 8x2 para implementar a função  $f = ab + \overline{c}$  desejada. Esta função é definida na Figura 2.10(a), e o bloco lógico é configurado para implementar, a função equivalente, mostrada na Figura 2.10(b). Se o *Latch* na saída do bloco não é necessário, então a RAM de configuração é programada para mantê-lo permanentemente transparente.

Figura 2.9 - Bloco lógico do FPGA ERA60100 da Plessey Semiconductor.

Figura 2.10 – Implementações estruturais da função  $f = ab + \overline{c}$ . (a) Direta. (b) Equivalente.

Vários outros fabricantes usam blocos de grão pequeno. A Algotronix [ALG89] usa um bloco lógico que pode executar qualquer função de duas variáveis de entrada. Isto é implementado usando um conjunto de multiplexadores configuráveis. Os blocos lógicos dos FPGAs da Concurrent Logic [CON91] e Toshiba [MUR91] contêm portas AND e NAND de duas entradas.

A vantagem principal de uso de blocos lógicos de grão pequeno é que os blocos usados para implementar as funções projetadas são utilizados com muita freqüência de forma completa. A exemplo dos blocos utilizados em tecnologias MPGAs (*Mask-Programmable Gate Arrays*) convencionais e/ou de células padronizadas (*standard cells*) [MIC96], blocos lógicos pequenos podem ser usados mais eficazmente, pois as técnicas de síntese lógica e física, para tais blocos, são semelhantes. A desvantagem principal de blocos lógicos de grão pequeno é que eles exigem um número relativamente grande de segmentos de fíos e chaves programáveis para o roteamento. Estes recursos de roteamento são dispendiosos em atraso e área do circuito integrado. Como resultado,

FPGAs empregando blocos de grão pequeno são em geral mais lentos e têm mais baixas densidades em relação aos que empregam blocos de grão grande.

#### 2.3.2 Arquiteturas de Grão Grande

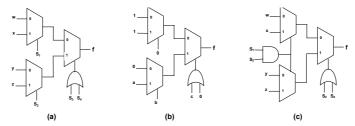

O bloco lógico da família Act-1 da Actel está baseado em multiplexadores para implementar diferentes funções lógicas. Ele funciona conectando cada de suas entradas a uma constante ou a um sinal. Este bloco consiste em três multiplexadores e uma porta OR. O Act-1, conforme é ilustrado na Figura 2.11(a), tem um total de 8 entradas  $(S_1, S_2, S_3, S_4, x, y, z e w)$  e uma saída (f), e implementa a

função genérica  $f = (s_3 + s_4)(s_1w + s_1x) + (s_3 + s_4)(s_2y + s_2z)$ .

Figura 2.11 – Blocos lógicos Actel (a) Bloco lógico da Act-1. (b) Função  $f = ab + \overline{c}$  implementada no Bloco Act-1. (c) Bloco lógico da Act-2.

Conectando cada variável a um sinal de entrada, ou a uma constante, 702 funções lógicas diferentes podem ser implementadas [LIN94]. Por exemplo, a função lógica  $f = ab + \overline{c}$  é implementada fixando-se as variáveis como mostrado na Figura 2.11(b): w = 1, x = 1,  $S_1 = 0$ , y = 0, z = a,  $S_2 = b$ ,  $S_3 = c$ , e  $S_4 = 0$ . O bloco lógico da família Act-2 [AHR90] é semelhante ao da Act-1. A diferença é que a seleção dos dois multiplexadores que configuram as entradas do bloco são unidas e conectadas à saída de uma porta AND de duas entradas, como mostrado em Figura 2.11(c). Esta mudança na estrutura do bloco lógico da família Act-2 permite implementar 766 funções lógicas, ou seja, 64 a mais que na Act-1.

Figura 2.12 - Bloco lógico da QuickLogic.

Semelhante à lógica da Actel, o bloco lógico dos FPGAs da QuickLogic [BIR91] empregam multiplexadores 2x1. Cada entrada do multiplexador é alimentada por uma porta AND, como ilustra a Figura 2.12. Estes blocos baseados em multiplexadores têm a vantagem de permitir um alto grau de funcionalidade para um número relativamente pequeno de transistores. Porém, isto é alcançado às custas de um número grande de entradas (variáveis), 8 no caso da Actel e 14 no caso da QuickLogic estas entradas, quando utilizadas, impõem elevada exigência nos recursos de roteamento. Assim, este tipo de bloco é mais adequado para FPGAs que usam chaves programáveis de pequeno tamanho, tais como antifusíveis.

#### Hardware Reconfigurável

Os blocos lógico das famílias 3000, 4000 e Virtex da Xilinx [XIL99] entre outras, são células baseadas em tecnologia de configuração SRAM. Os blocos lógicos de FPGAs da Xilinx usam LUTs. Uma tabela verdade, para funções lógicas de K entradas, é armazenada em uma SRAM  $2^K x$  1 bit. As linhas de endereço da SRAM funcionam como entradas, e a saída da SRAM fornece o valor da função lógica. Por exemplo, considere a tabela verdade da função lógica  $f = ab + \overline{c}$ . Esta função lógica é implementada utilizando uma LUT de 3 entradas conforme representado na Figura 2.6, para tal a SRAM armazena "1" nos endereços "000," "010," "100," "110", "111" e "0" nos demais como, especificado pela tabela verdade.

Uma LUT de K entradas pode implementar qualquer  $2^{2^K}$  funções de K variáveis. A vantagem de LUTs é que estas exibem alta funcionalidade. A desvantagem é que elas tornam-se muito grandes para funções de mais de cinco entradas. Além disso são necessárias  $2^K$  células de memória para uma LUT de K entradas. Mesmo que o número de funções que podem ser implementadas cresça rapidamente, muitas das funções adicionais não são usadas freqüentemente em projetos práticos, além de serem de difícil utilização por ferramentas de síntese lógica. Desta forma, é freqüente o caso que uma LUT grande ser em grande parte subtilizada. A Seção 2.5 apresenta algumas informações quantitativas sobre este assunto.

O bloco lógico da família 3000 de FPGAs da Xilinx [XIL99] contém uma LUT de 5 entradas e 1 saída. Este bloco pode ser reconfigurado em duas LUTs de quatro entradas, possibilitando uma maior flexibilidade na utilização do bloco lógico, visto que funções lógicas frequentemente não exigem mais de quatro variáveis de entrada. O bloco também permite a implementação de lógica seqüencial e possui vários multiplexadores. Estes últimos permitem conectar as entradas combinacionais com as saídas diretamente ou passando por elementos biestáveis. Os multiplexadores são controlados por células de SRAM carregadas durante a configuração do FPGA.

Na família 4000 de FPGAs Xilinx o bloco lógico contém duas LUTs de 4 entradas e suas saídas são conectadas a uma outra LUT de 3 entradas, como apresentado na Figura 2.13. Este bloco introduz duas mudanças significativas comparadas ao bloco lógico da série 3000. A primeira, dois tamanhos de LUTs são utilizadas, permitindo um melhor compromisso entre desempenho e densidade lógica (ver mais detalhes na Seção 2.5). A segunda é o uso de duas conexões diretas, que ligam as saídas das duas LUTs de quatro entradas para as entradas da LUT de três entradas. Estas duas conexões são significativamente mais rápidas que qualquer interconexão programável, pois nenhuma chave programável é utilizada em série. Com o uso adequado destas conexões rápidas, pode-se melhorar o desempenho do FPGA. Porém há uma desvantagem para este tipo de conexão. Já que a conexão é permanente, a LUT de três entradas tem sua flexibilidade limitada e freqüentemente não pode ser utilizada, reduzindo a densidade lógica global.

O bloco lógico Xilinx 4000 incorpora várias características adicionais. Cada LUT pode ser utilizada diretamente como um bloco de SRAM de pequenas dimensões (32x1 bits com porta simples ou 16x2 ou 16x1 bits porta dupla). Isto permite implementar memórias pequenas mais eficazmente. Outra característica é a inclusão de circuitos dedicados para a implementação de somadores rápidos, via linha de propagação rápida de vai uns (fast carry addition circuits).

#### Hardware Reconfigurável

Figura 2.13 - Bloco lógico Xilinx série 4000.

A arquitetura da maioria dos CPLDs e FPGAs Altera [WON89] evoluiu da arquitetura PLA baseada em PLDs tradicionais de baixa densidade [LAL90]. Seu bloco lógico possui um grande número de entradas (de 20 a mais de 100). Este é constituído de portas AND que alimentam portas OR. A Figura 2.14(a) ilustra o bloco lógico do CPLD Altera MAX série 5000. As entradas das portas AND podem ser conectadas a qualquer linha vertical do barramento por meio de chaves eletrônicas com tecnologia de configuração de porta flutuante, vista na Seção 2.2.3. A Figura 2.14(b) ilustra a implementação da função lógica  $f = ab + \overline{c}$ . As conexões na figura indicam quais chaves eletrônicas estão fechadas para configurar o bloco lógico com a função desejada.

Figura 2.14 - Bloco lógico Altera série 5000 e seu emprego.

A vantagem deste tipo de bloco é que o grande número de entradas pode ser usado para formar funções complexas com poucos blocos lógicos, reduzindo a necessidade de muitas interconexões programáveis. Isto porém, resulta em perda de densidade, pois é difícil fazer uso eficiente de todas entradas e todas portas. Esta perda não é tão significativa, pois é compensada pela alta densidade das portas *Wired-AND*. As próprias conexões servem também para o roteamento, diferente do que ocorre em outras arquiteturas, onde a configuração da lógica e o roteamento estão separados. Uma desvantagem das portas *Wired-AND* é o uso de resistores *pull-up*, que apresentam alto consumo de energia na configuração.

O bloco lógico dos CPLDs Altera MAX 7000 [VIJ92] é semelhante ao dos MAX 5000. Os blocos lógicos são implementados com dois termos produto a mais que os da série 5000 e também maior flexibilidade, porque blocos adjacentes podem utilizar termos produto um do outro. Vários outros FPGAs fazem o uso de grandes blocos lógicos, estilo AND-OR, entre os quais alguns produzidos pela Concurrent Logic [CON91], AMD [AMD90] e Lattice [BAK91].

#### 2.4 Arquiteturas de Roteamento

A arquitetura de roteamento de um FPGA é a maneira através da qual são configuradas as chaves e segmentos de fios para realizar as interconexões dos blocos lógicos. Nesta Seção apresenta-se uma arquitetura utilizada comercialmente como referência para o estudo das arquiteturas de roteamento de forma genérica, observando-se que cada fabricante possui um modelo particular.

A Figura 2.15 define um modelo genérico de arquiteturas de roteamento de FPGAs comerciais. Neste modelo podemos identificar várias características. Primeiro, um *segmento de fio* é contínuo. Uma ou mais chaves podem ser ligadas a segmentos de fio; Cada final de um segmento de fio está tipicamente ligado a uma chave programável; Uma *trilha* é uma sucessão em linha de um ou mais segmentos de fio e um *canal de roteamento* é um grupo de trilhas paralelas.

Figura 2.15 - Arquitetura de roteamento genérica.

A partir da Figura 2.15, nota-se que o modelo contém três estruturas básicas. A primeira é o *bloco de conexão* (não mostrado na figura) que aparece em todas as arquiteturas. Um bloco de conexão provê a interligação entre entradas e saídas de um bloco lógico e os segmentos de fio no canal de roteamento. Embora não mostrado na figura, podem haver blocos de conexão tanto na vertical como na horizontal. A segunda estrutura é o *bloco de chaves*, o qual provê a conectividade dos segmentos horizontais com os segmentos verticais. O bloco de chaves provê conectividade entre os segmentos incidentes em seus quatro lados. Em algumas arquiteturas, o bloco de chaves é intercalado com o bloco de conexão, e em outros eles são combinados em uma única estrutura. Um último bloco de relevante importância é o *bloco de entrada/saída*. Através deste é realizada a conexão do FPGA com o mundo externo. Neste bloco, os pinos terminais do componente FPGA são configurados para a transferência de sinais do interior do componente ou para o exterior do componente.

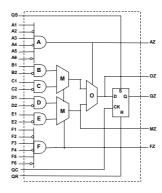

Um exemplo típico de arquitetura de roteamento é a utilizada na família 4000 de FPGAs da Xilinx. As conexões entre os blocos lógicos são feitas no canal de roteamento com segmentos de metal unidos por uma matriz de chaves programáveis. A Figura 2.16, obtida do manual do fabricante [XIL99], ilustra um conjunto de linhas horizontais e verticais interconectadas em um bloco PSM (Programmable Switch Matrix), onde cada matriz de chaves consiste em transistores de passagem configuráveis, utilizada para estabelecer a conexão entre as linhas. O CLB (Configurable Logic Block) executa as funções lógicas do circuito. As interconexões dos recursos são configuradas para formar trilhas de fios, que transportam os sinais lógicos entre os blocos, semelhante às trilhas em placas de circuito impresso convencionais. As funções dos blocos lógicos são implementadas em LUTs, estabelecidas via um arquivo de configuração. Este arquivo é carregado para o interior da matriz, onde é armazenado em células de memória SRAM de configuração.

#### Hardware Reconfigurável

Figura 2.16 - Arquitetura de roteamento Xilinx 4000.

#### 2.5 Granularidade, Densidade e Desempenho de FPGAs

Quando o tamanho do grão do bloco lógico aumenta, espera-se que o número de blocos necessários para implementar um projeto diminuia. Por outro lado, um bloco lógico mais poderoso (de grão maior) exige mais interconexões configuráveis para implementá-lo, e por consequência, ocupa mais área. Este situação antagônica sugere a existência de um ponto ótimo para a granularidade de bloco lógico, no qual a área de FPGA dedicada à implementação da lógica é minimizada. A porção de área para a implementação da lógica é relativamente fácil calcular, enquanto que o efeito de granularidade no roteamento não é tão simples, e tem grande influência na área de roteamento de todo o FPGA.

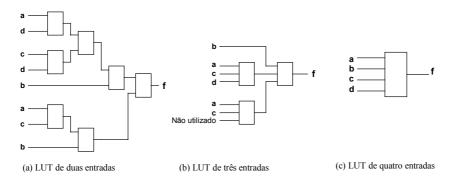

O efeito da funcionalidade do bloco sobre a área de lógica é facilmente observado, por exemplo, a implementação da função de lógica  $f = abd + bc\overline{d} + \overline{a}\overline{b}\overline{c}$ , utilizando blocos lógicos de três tamanhos do grão diferentes, como ilustrado na Figura 2.17, supondo que cada bloco lógico contém uma LUT.

Figura 2.17 - Implementação da função lógica  $f = abd + bc\overline{d} + \overline{a}\overline{b}\overline{c}$ .

Cada um dos blocos lógicos são LUTs de duas entradas, na Figura 2.17(a), três entradas, na Figura 2.17(b) e quatro entradas, na Figura 2.17(c). A implementação da função com LUTs de duas entradas requer sete blocos lógicos, com LUTs de três entradas requer três blocos, e com LUTs de quatro um único bloco. Considera-se como uma medida de área o número de *bits* de memória necessários para implementar a função lógica *f*, utilizando LUTs de **K** entradas. Considera-se ainda que cada LUT de **K** entradas requer  $2^{\mathbf{K}}$  *bits*, a implementação da função com tabelas de duas

entradas exige um total de 28 *bits*, as de três exigem 24 *bits* e as de quatro 16 *bits*. Conclui-se que, utilizando esta medida de área como referência, as LUTs de quatro entradas exigem menor área de lógica para a implementação da função.

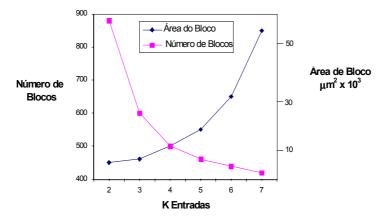

A Figura 2.18 dá um exemplo de resultados experimentais que apontam para um determinado tamanho de grão de bloco lógico, tamanho este que requer a menor área de lógica para a implementação da função [ROS93, ROS90]. Um determinado número de projetos foram mapeados em FPGAs com diferentes tamanhos de grão de bloco. A área total do bloco lógico, bem como a área de roteamento são determinadas para cada mapeamento. São calculadas ainda as médias dos resultados, que então são comparados.

Figura 2.18 - Número de blocos e área do bloco para um circuito [ROS93].

O número de blocos lógicos diminui rapidamente como o aumento de **K** (número de entradas do bloco lógico), enquanto que o tamanho de bloco aumenta exponencialmente com **K**. A área total do bloco lógico (o produto das duas curvas) alcança um mínimo em **K=4**. A área mínima total do bloco lógico possui uma fraca dependência com tamanho da chave programável discutido em detalhes nas referências [GAM89] e [ROS93].

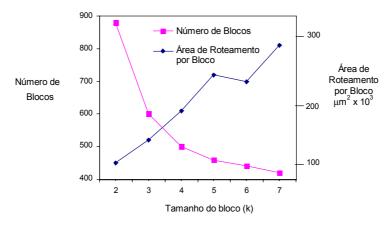

A Figura 2.19 mostra dois parâmetros de um circuito exemplo variando em função do tamanho de LUT empregado. Estes parâmetros são o número total de blocos do circuito e a área de roteamento por bloco. A área de lógica ativa é parte da área total. A área para o roteamento é normalmente maior que a área ativa. Em FPGAs, o roteamento representa de 70 a 90% da área total.

Figura 2.19 - Número de blocos e área de roteamento versus tamanho do bloco para um circuito exemplo [ROS93].

#### 2.6 Núcleos de Propriedade Intelectual (IP Cores)

Um *Núcleo de Propriedade Intelectual* é um sistema digital complexo pré-projetado e pré-validado, cuja utilização como módulo componente de um sistema maior é licenciado a terceiros pelo desenvolvedor [VAH01]. O nome deriva da nomeclatura em inglês, Intellectual Property core, ou IP core.

Tecnologias de implementação submicrônicas introduziram a possibilidade de integrar todo um sistema complexo em um único CI, criando o conceito de Integração a nível de sistema (em Inglês, System-Level Integration – SLI, ou mais coloquialmente, System-On-a-Chip – SOC). O conceito de IP core surgiu [CAS97] como forma de reduzir o tempo de desenvolvimento de produtos complexos viabilizados pela crescente taxa de integração de CIs VLSI (do inglês, *Very Large Scale Integration*) em SOCs.

A comercialização de propriedade intelectual sob a forma de IP cores é hoje uma alternativa à comercialização de CIs complexos para os desenvolvedores de componentes. Para aquele que adquire um IP core, existem vantagens importantes. Primeiro, a melhoria do desempenho do produto final pode ser importante, devido à integração de diversos componentes poder ocorrer em um único CI. Segundo, aumentando-se o sigilo do projeto, pela implementação de CIs dedicados. Terceiro e mais importante, o uso de IP cores pode levar a uma redução significativa no tempo de desenvolvimento do projeto, capitalizando na pré-validação do IP core licenciado.

Contudo, também podem haver desvantagens para quem licencia a para quem desenvolve sistemas a serem comercializados sob a forma de propriedade intelectual. O desenvolvedor, por um lado, expõe seu projeto até certo ponto, sem o que pode inviabilizar a integração do IP core por quem licencia. Esta exposição implica um risco maior ao sigilo do projeto do IP core que a comercialização dos CIs. No lado do licenciador de um IP core, as desvantagens principais são o alto custo, comprado com um CI encapsulado equivalente e a eventual inflexibilidade do IP core a adaptar-se aos requisitos de um projeto específico. O alto custo deriva do fato de se tratar de propriedade intelectual reutilizável. Assim, considerações de volume de produção e número de produtos que podem empregar um dado IP core são importantes antes do compromisso de adquirir tais módulos. A necessidade de flexibilidade de um IP core, por outro lado, leva os desenvolvedores a criar compromissos de grau de validação, grau de sigilo e custo do IP core, gerando diferentes formas de disponibilizar estes componentes.

Os FPGAs habilitam o desenvolvimento de SOCs mediante arquiteturas reconfiguráveis e/ou plataformas de prototipação. O desenvolvedor pode fazer uso de IP cores da mesma forma dos que estão disponíveis para o desenvolvimento de CIs complexos. Estes IP cores também podem ser disponibilizados visando o uso em dispositivos FPGAs. Na Seção a seguir, explora-se uma classificação das formas de disponibilização de IP cores.

#### 2.6.1 Classificação de IP Cores

Conforme Case em [CAS97], quatro critérios podem ser usados para diferenciar e classificar os IP cores. Um destes é a rigidez (hardness) dos blocos, ou seja o grau em que o IP core pode ser modificado para um processo de implementação particular. Outros três critérios são: a modelagem; a flexibilidade e a previsibilidade. Estes critérios são usados na Tabela 2.1, produzindo três classes de IP cores. Estas classes são:

a) **Hard Core:** otimizado para uma tecnologia específica, não podendo ser modificado pelo projetista. Possui uma organização pré-definida e uma planta baixa (do inglês,

#### Hardware Reconfigurável

Floorplaning) incluída com a arquitetura do projeto. As vantagens são uma temporização garantida e poder ser tratado como célula elemento de uma biblioteca durante o projeto. A desvantagem é que o usuário poderá não ser capaz de personalizar as funções ou sintonizar a temporização do módulo ao restante do projeto.

- b) **Firm Core:** apresentado como uma mistura de código fonte e código objeto (sob forma de um Netlist) que depende de uma determinada tecnologia. Neste tipo de core, o código fonte é aberto ao projetista e partes específicas podem ser personalizadas. Contudo a parte especializada com netlist possui tecnologia específica e o usuário não pode facilmente substituir o dispositivo de hardware pelo de outro fabricante.

- c) **Soft Core:** fornecido normalmente sob a forma de uma descrição em com uma linguagem para descrição de hardware (HDL do inglês, Hardware Description Language). Um IP Soft Core oferece liberdade quanto à tecnologia do fabricante, permite grande flexibilidade ao projetista. Este pode facilmente modificá-los ou resintetizá-los para diferentes tecnologias, por exemplo substituindo o dispositivo de hardware pelo de outro fabricante, de acordo com a conveniência do projeto. A desvantagem deste tipo de core é que a temporização é um aspecto crítico. Não é garantido que o IP core possa ser sintetizado, mapeado, localizado e tenha suas rotas definidas para cada uma das possíveis implementações.

|                 | Hard core                                      | Firm core                                                                                 | Soft Core                                                                     |

|-----------------|------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Rigidez         | A organização é<br>predefinida.                | Combinação de código fonte e netlist dependente de tecnologia.                            | Apresenta um código fonte comportamental independente da tecnologia.          |

| Modelagem       | Modelado como um elemento de biblioteca.       | Combinação de blocos sintetizáveis fixos. Permite compartilhar recursos com outros cores. | Sintetizável com<br>diversas tecnologias.                                     |

| Flexibilidade   | Não pode ser<br>modificado pelo<br>projetista. | A personalização de funções específicas é dependente da tecnologia.                       | O projeto pode ser<br>modificado e independe<br>da tecnologia.                |

| Previsibilidade | Temporização é<br>garantida.                   | Caminhos críticos com temporizações fixas.                                                | A temporização não é garantida, podendo não atender os requisitos do projeto. |

Tabela 2.1 – Três classificações de IP cores baseado em quatro critérios.

Um exemplo típico de um IP core comercial bastante difundido é o PCI LogiCORE da Xilinx, comentado na Seção 3.4.3 Este IP core permite ao projetista construir e personalizar um sistema de barramento compatível com o padrão PCI de 32 bits e frequência de operação de 33 MHz.

#### 2.7 Famílias Recentes de FPGAs e CPLDs

FPGAs têm evoluído de forma acelerada, em geral de forma mais acelerada que os segmentos de mercado de memória ou processadores. Novas famílias surgem a todo momento para endereçar os mais diferentes aspectos de sistemas eletrônicos tais como alta capacidade, baixo custo, sistemas completos em um único CI (em inglês, *System On a Chip* ou SOC), dotação de módulos especiais, etc.