# PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL - PUCRS FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

### Reconfiguração Parcial e Dinâmica para Núcleos de Propriedade Intelectual

por

Eduardo Wenzel Brião

Dissertação de mestrado submetida como requisito parcial à obtenção do grau de Mestre em Ciência da Computação.

Orientador: Prof. Dr. Ney Laert Vilar Calazans

Porto Alegre, janeiro de 2004.

# Sumário

| LISTA  | DE F   | TIGURAS                                               | 7   |

|--------|--------|-------------------------------------------------------|-----|

| LISTA  | DE T   | CABELAS                                               | ix  |

| LISTA  | DE S   | ÍMBOLOS E ABREVIATURAS                                | x   |

| RESU:  | MO     |                                                       | xix |

| ABST   | RACT   |                                                       | xx  |

| Capíti | ulo 1: | Introdução                                            | 1   |

| 1.1    | Motiv  | ração                                                 | 4   |

| 1.2    | Objet  | ivos                                                  | 5   |

| 1.3    | Organ  | nização do Volume                                     | 5   |

| Capíti | ulo 2: | Estado da Arte em SDRs                                | 7   |

| 2.1    |        | ições Básicas de Reconfiguração                       | 7   |

| 2.2    | Propo  | ostas de SDRs                                         | 8   |

|        | 2.2.1  | Reconfiguração parcial em nível de circuito integrado | g   |

|        | 2.2.2  | Reconfiguração parcial em nível de placa              | 14  |

| 2.3    | Forma  | as de Reconfiguração                                  | 17  |

|        | 2.3.1  | Reconfiguração baseada em alterações incrementais     | 17  |

|        | 2.3.2  | Reconfiguração baseada na inserção/remoção de núcleos | 18  |

| 2.4    | Requi  | sitos para Habilitar SDRs                             | 18  |

| 2.5    | Supor  | te de Software para Reconfiguração Parcial            | 20  |

|        | 2.5.1  | Conjunto de classes JBits                             | 20  |

|        | 2.5.2  | Ferramenta JRTR (Java Run-Time Reconfiguration)       | 22  |

|        | 2.5.3  | Ferramenta PARBit                                     | 22  |

|        | 2.5.4  | Gerador de arquivo de configuração - JPG              | 24  |

|        | 2.5.5  | Ferramentas alternativas desenvolvidas por Möller     | 26  |

ii SUMÁRIO

| Capíti | ulo 3: Reconfiguração Baseada em Núcleos e Interconexão de Nú-  |    |

|--------|-----------------------------------------------------------------|----|

| cleos  |                                                                 | 31 |

| 3.1    | Métodos Habilitadores                                           | 31 |

|        | 3.1.1 Barramento proposto por Palma                             | 31 |

|        | 3.1.2 Reconfiguração parcial via Projeto Modular                | 33 |

| 3.2    | Métricas para Avaliação de SDRs                                 | 34 |

| 3.3    | Padronização da Comunicação Intra-chip                          | 36 |

|        | 3.3.1 Abordagem centrada no meio de comunicação                 | 36 |

|        | 3.3.2 Abordagem centrada na interface de comunicação            | 37 |

|        | 3.3.3 Protocolo OCP                                             | 38 |

| 3.4    | Contexto do Trabalho                                            | 44 |

| Capíti | ulo 4: Fluxo de Projeto Modular                                 | 47 |

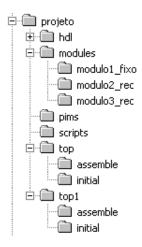

| 4.1    | Preparação dos Módulos e Fases do Projeto Modular               | 48 |

|        | 4.1.1 Preparação da entrada do fluxo                            | 48 |

|        | 4.1.2 Ferramental para a execução do fluxo                      | 53 |

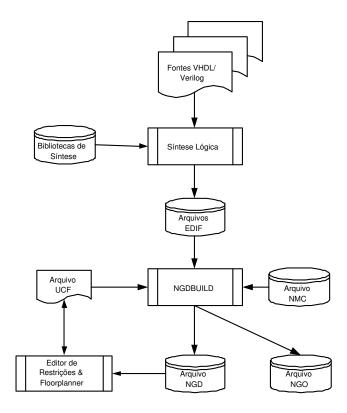

|        | 4.1.3 Fase Orçamento Inicial                                    | 55 |

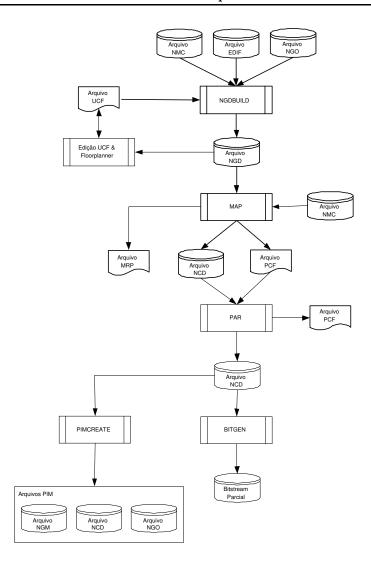

|        | 4.1.4 Fase Implementação do Módulo Ativo                        | 56 |

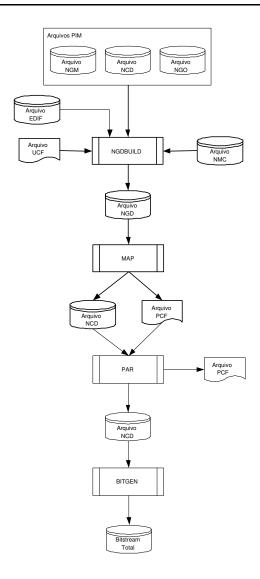

|        | 4.1.5 Fase Montagem Final                                       | 57 |

| 4.2    | Contribuições                                                   | 58 |

| 4.3    | Crítica do Processo                                             | 60 |

| 4.4    | Proposta de Ferramental                                         | 61 |

| Capíti | ulo 5: Validação do Fluxo Modular de Projeto                    | 65 |

| 5.1    | Descrição da Plataforma de Reconfiguração Alvo                  | 65 |

| 5.2    | Estudos de Caso                                                 | 66 |

|        | 5.2.1 Calculadora reconfigurável                                | 67 |

|        | 5.2.2 Contador reconfigurável                                   | 68 |

|        | 5.2.3 Contador reconfigurável com interface OCP                 | 69 |

|        | 5.2.4 Contador com duas áreas reconfiguráveis                   | 70 |

|        | 5.2.5 Controlador de memória SRAM                               | 71 |

| 5.3    | Análise do tempo de reconfiguração                              | 71 |

|        | 5.3.1 Tempos de reconfiguração                                  | 71 |

| Capíti | ulo 6: Processador Reconfigurável                               | 77 |

| 6.1    | O Processador R8                                                | 77 |

| 6.2    | Características Adicionadas ao Processador R8 - Processador R8R | 80 |

| SUMÁRIO | iii |

|---------|-----|

|---------|-----|

| 6.3    | Validação por Simulação                                         | 83  |

|--------|-----------------------------------------------------------------|-----|

| 6.4    | Prototipação                                                    | 89  |

| 6.5    | Análise dos Resultados na Execução do Processador R8R           | 93  |

|        | 6.5.1 Coprocessador de multiplicação                            | 93  |

|        | 6.5.2 Coprocessador de divisão                                  | 94  |

|        | 6.5.3 Coprocessador de raiz quadrada                            | 94  |

| Capítı | ılo 7: Conclusão e Trabalhos Futuros                            | 97  |

| REFEI  | RÊNCIAS BIBLIOGRÁFICAS                                          | 101 |

| Apênd  | lice A: Códigos-fonte para o Processador R8R                    | 109 |

| A.1    | Software para teste de todos os coprocessadores reconfiguráveis | 109 |

| A.2    | Multiplicação em software                                       | 112 |

| A.3    | Divisão em software                                             | 113 |

| A.4    | Raiz quadrada em software                                       | 115 |

| Apênd  | lice B: Considerações quanto a Erros de Roteamento              | 117 |

| B.1    | Impossibilidade da Geração de Sinais de Lógica Global           | 117 |

| B.2    | Comportamento Indesejável do Projeto: Escorregamento de Relógio | 120 |

iv SUMÁRIO

# Lista de Figuras

| 1.1  | Arquitetura genérica de um SoC                                                        | 3  |

|------|---------------------------------------------------------------------------------------|----|

| 2.1  | Estrutura de interconexão das células no interior do FPGA Xilinx XC6200               | 10 |

| 2.2  | FPGA AT40K da ATMEL, onde núcleos IP armazenados em memória confi-                    |    |

|      | guram o FPGA em tempos diferentes                                                     | 11 |

| 2.3  | Esquema de um CLB do FPGA XCV300                                                      | 11 |

| 2.4  | Disposição em colunas dos elementos do FPGA Virtex XCV300                             | 12 |

| 2.5  | Arquitetura de um dispositivo da Família VirtexII                                     | 12 |

| 2.6  | Arquitetura do SPLASH 2                                                               | 15 |

| 2.7  | Arquitetura CHESS constituída por um arranjo matricial de ULAs conectadas             |    |

|      | entre si                                                                              | 16 |

| 2.8  | Arquitetura do sistema reconfigurável Amalgam                                         | 16 |

| 2.9  | Arquitetura do Cluster Reconfigurável                                                 | 17 |

| 2.10 | Núcleos IP reconfiguráveis conectados a uma interface de comunicação                  | 18 |

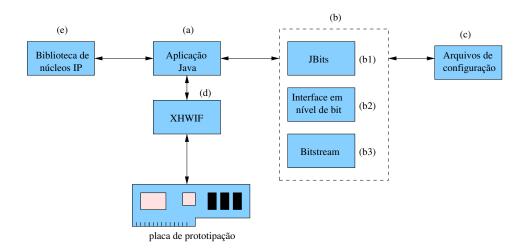

| 2.11 | Fluxo de projeto do JBits para prover controle e dados de configuração                | 21 |

| 2.12 | Aplicação escrita em JAVA desenvolvida pelo usuário. Percebe-se que há dife-          |    |

|      | rentes níveis de abstração para a geração de arquivos de configuração parciais,       |    |

|      | ocultando detalhes do usuário                                                         | 21 |

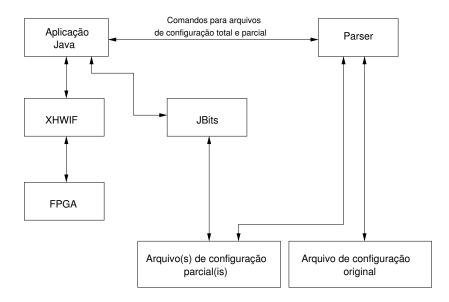

| 2.13 | Fluxo de projeto do JRTR                                                              | 23 |

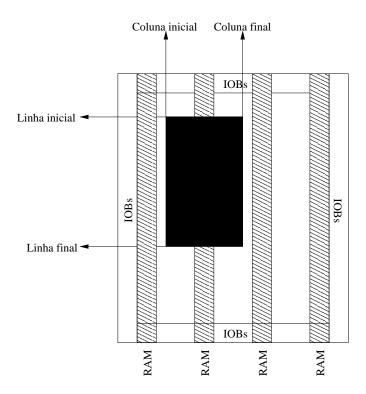

| 2.14 | FPGA com uma área hachurada, a qual contem um módulo que será gerado                  |    |

|      | no arquivo reconfigurável pela ferramenta PARBIT                                      | 23 |

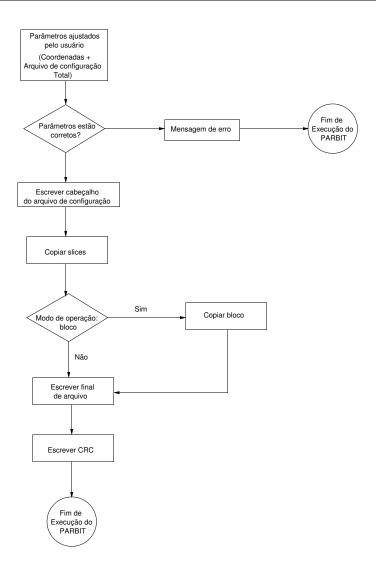

| 2.15 | Fluxo de projeto e execução da ferramenta PARBIT                                      | 25 |

| 2.16 | Fluxo de projeto do gerador de arquivos de configuração JPG                           | 26 |

| 2.17 | Interface gráfica do Core Unifier                                                     | 28 |

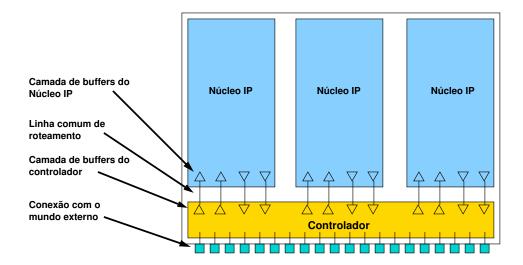

| 3.1  | Estrutura de um SoC usando o método proposto por Palma [PAL02]. Neste,                |    |

|      | duas camadas de $\mathit{buffers}$ que possibilitam a implementação do controlador no |    |

|      | FPGA                                                                                  | 32 |

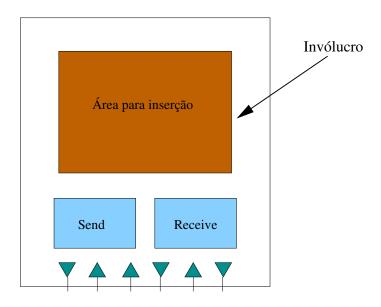

| 3.2  | Estrutura do invólucro para inserção de núcleos IP no método proposto por             |    |

|      | Palma [PAL02]                                                                         | 32 |

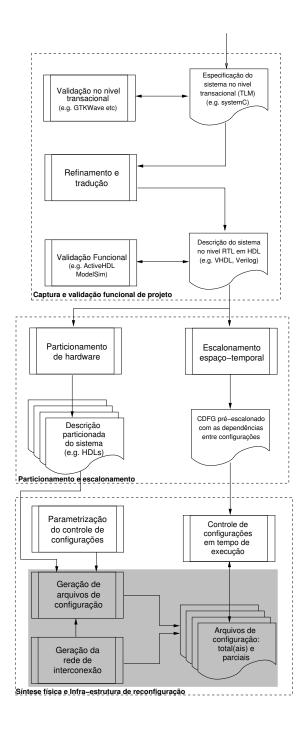

| 3.3                             | Visão geral do fluxo de reconfiguração dinâmica e parcial baseada no Projeto Modular                                                             | 33                               |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

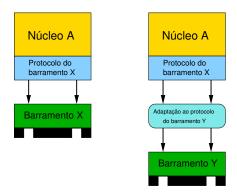

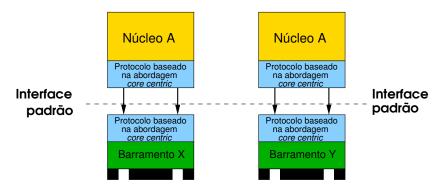

| 3.4                             | Exemplo da desvantagem principal de comunicação baseada na abordagem cen-                                                                        | 00                               |

|                                 | trada no meio de comunicação. Neste modelo [OCP02], um núcleo IP denomi-                                                                         |                                  |

|                                 | nado $A$ com protocolo de comunicação adaptado a um barramento $X$ pode ser                                                                      |                                  |

|                                 | conectado diretamente ao barramento $X$ . No entanto, para conectar o mesmo                                                                      |                                  |

|                                 | núcleo a um barramento $Y$ , (protocolo de comunicação diferente do barramento                                                                   |                                  |

|                                 | X) são necessárias alterações no protocolo deste núcleo para adaptar este ao                                                                     |                                  |

|                                 | barramento $Y$                                                                                                                                   | 36                               |

| 3.5                             | Exemplo de uma arquitetura baseada na abordagem core-centric                                                                                     | 37                               |

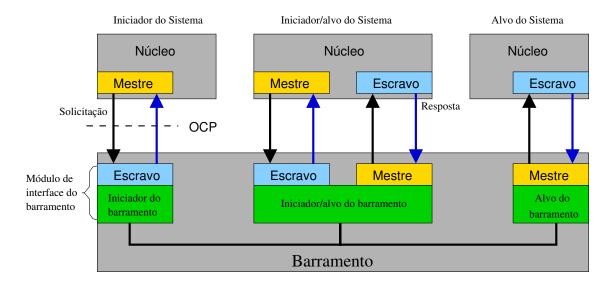

| 3.6                             | Sistema usando um barramento e núcleos empacotados com instâncias OCP                                                                            | 39                               |

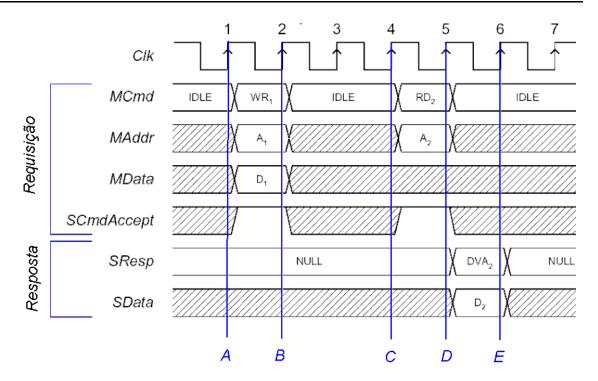

| 3.7                             | Diagrama do protocolo de comunicação de uma transferência de escrita e leitura                                                                   |                                  |

|                                 | de dados.                                                                                                                                        | 42                               |

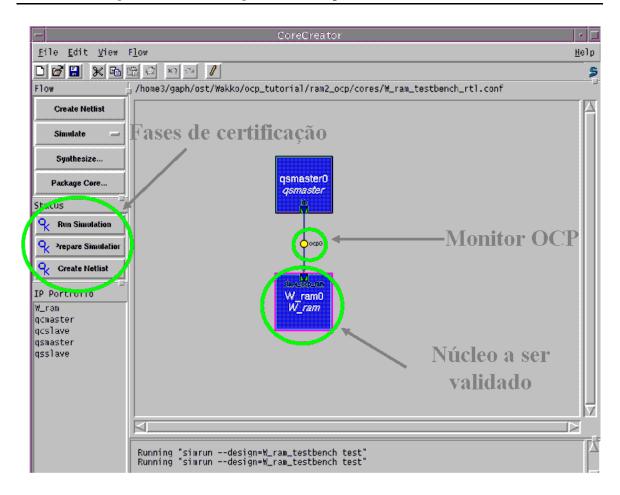

| 3.8                             | Ferramenta Core Creator para validação e certificação do protocolo OCP apli-                                                                     |                                  |

|                                 | cado em núcleos IP ou sistemas. A ferramenta valida os módulos com OCP                                                                           |                                  |

|                                 | através da geração de tráfego de dados                                                                                                           | 43                               |

| 3.9                             | Fluxo de desenvolvimento e implementação de sistemas dinamicamente recon-                                                                        |                                  |

|                                 | figuráveis de acordo com o arcabouço PADREH proposto. A área hachurada                                                                           |                                  |

|                                 | representa o agrupamento das tarefas propostas neste trabalho                                                                                    | 45                               |

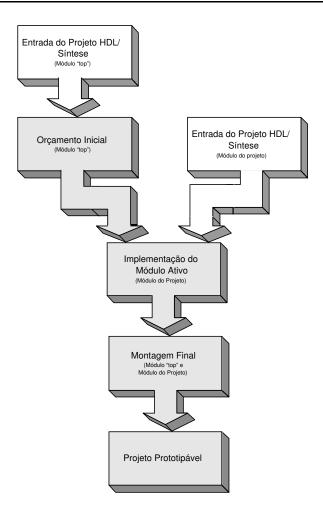

| 4.1                             | Visão geral das fases do Projeto Modular                                                                                                         | 48                               |

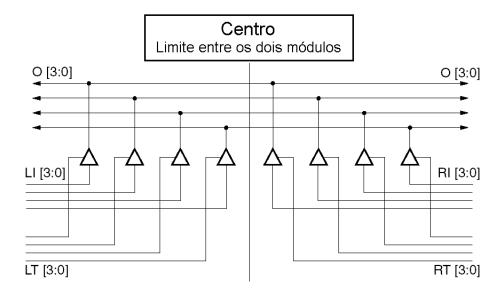

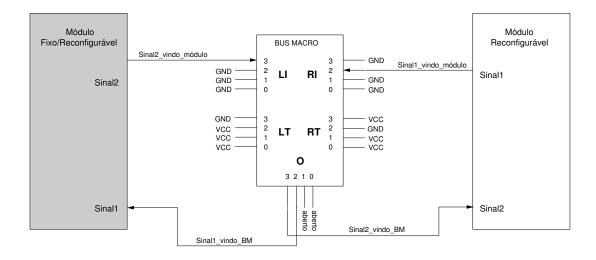

| 4.2                             | Esquemático de uma bus macro, formada por 8 tristates. Os sinais LT e RT                                                                         |                                  |

|                                 | são responsáveis pelo controle de acesso aos fios compartilhados pelos módulos,                                                                  |                                  |

|                                 | denominados O[3:0]. Um dos conjuntos de sinais LI e RI pode ser usado a cada                                                                     |                                  |

|                                 |                                                                                                                                                  |                                  |

|                                 | instante como fonte de informação a enviar para o módulo do outro lado da                                                                        |                                  |

|                                 | instante como fonte de informação a enviar para o módulo do outro lado da bus macro. Cada bus macro provê um barramento de comunicação de 4 bits |                                  |

|                                 | bus macro. Cada <i>bus macro</i> provê um barramento de comunicação de 4 bits entre os módulos                                                   | 49                               |

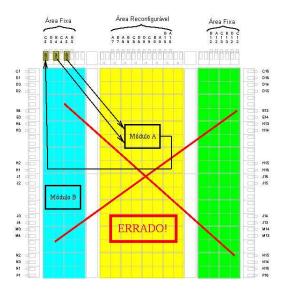

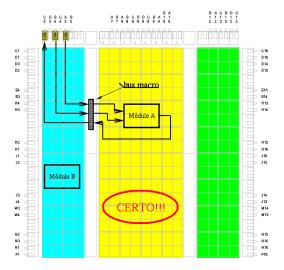

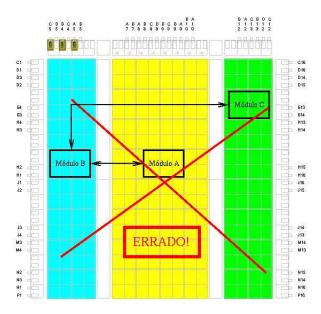

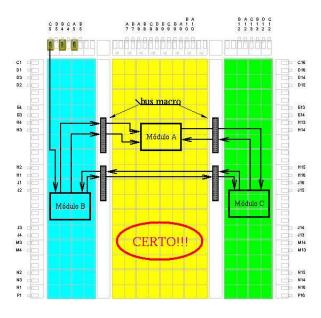

| 4.3                             | bus macro. Cada <i>bus macro</i> provê um barramento de comunicação de 4 bits entre os módulos                                                   |                                  |

|                                 | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50                               |

| 4.4                             | bus macro. Cada $bus$ $macro$ provê um barramento de comunicação de 4 bits entre os módulos                                                      | 50<br>51                         |

| 4.4<br>4.5                      | bus macro. Cada $bus$ $macro$ provê um barramento de comunicação de 4 bits entre os módulos                                                      | 50                               |

| 4.4                             | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51                   |

| 4.4<br>4.5<br>4.6               | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51<br>52             |

| 4.4<br>4.5<br>4.6               | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51                   |

| 4.4<br>4.5<br>4.6               | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51<br>52<br>52       |

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8 | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51<br>52<br>52<br>53 |

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8 | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51<br>52<br>52       |

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8 | bus macro. Cada bus macro provê um barramento de comunicação de 4 bits entre os módulos                                                          | 50<br>51<br>51<br>52<br>52<br>53 |

|      | Fluxo de execução da fase Implementação do Módulo Ativo do Projeto Modular.   | 58<br>59 |

|------|-------------------------------------------------------------------------------|----------|

|      | Fluxo de execução da fase Montagem Final do Projeto Modular                   |          |

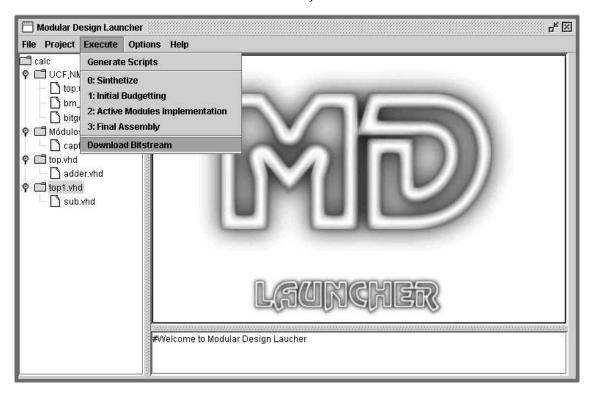

| 4.13 | Interface gráfica da ferramenta MDLaucher                                     | 62       |

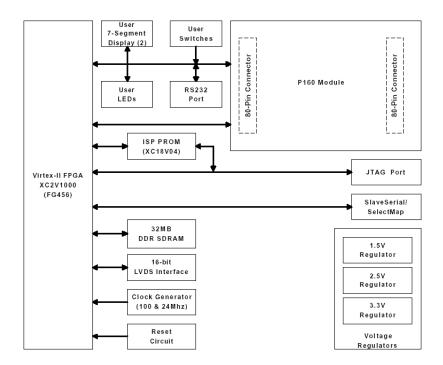

| 5.1  | Diagrama de blocos da plataforma V2MB1000                                     | 66       |

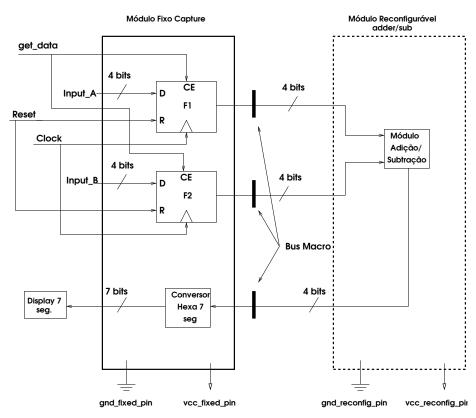

| 5.2  | Bloco lógico de uma calculadora reconfigurável de duas operações              | 67       |

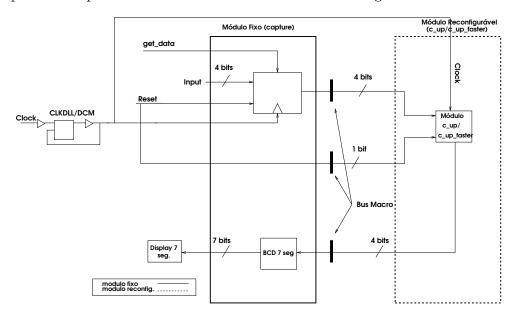

| 5.3  | Diagrama de blocos de um contador reconfigurável                              | 69       |

| 5.4  | Diagramas de tempos do contador OCP                                           | 70       |

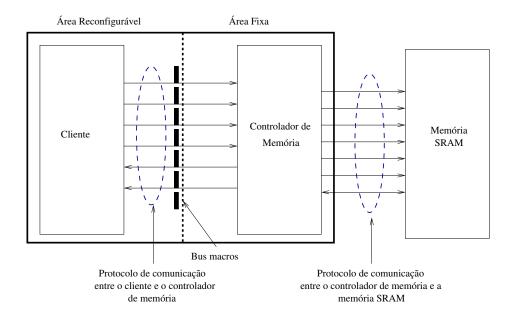

| 5.5  | Diagrama de blocos de um controlador de memória SRAM conectada a um           |          |

|      | módulo cliente                                                                | 72       |

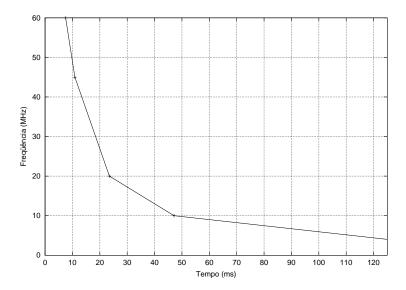

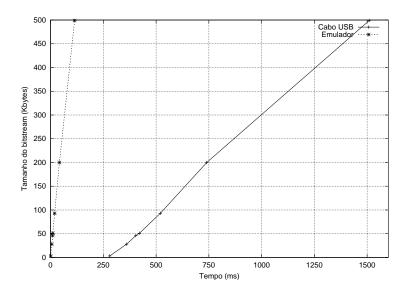

| 5.6  | Gráfico das medidas dos tempos de reconfiguração do modo de configuração      |          |

|      | mais rápida suportada pelo FPGA Virtex II (tempo de reconfiguração versus     |          |

|      | freqüência para transmissão de dados)                                         | 72       |

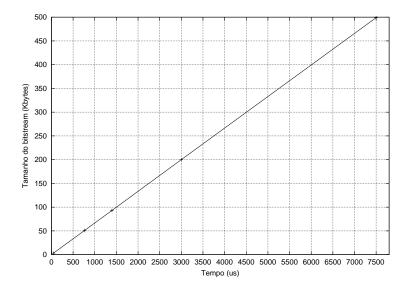

| 5.7  | Gráfico da estimativa dos tempos de reconfiguração para o modo de confi-      |          |

|      | guração mais rápido suportado pelo FPGA Virtex II XC2V1000 (tempo de          |          |

|      | reconfiguração em microssegundos versus tamanho dos bitstreams em kilobytes). | 73       |

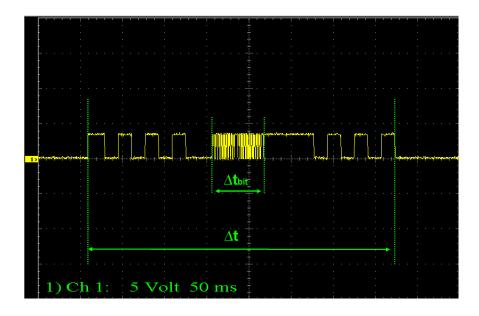

| 5.8  | Amostragem do sinal CCLK durante uma configuração de FPGA usando o            |          |

|      | cabo Multilinx                                                                | 74       |

| 5.9  | Ganho obtido no tempo de reconfiguração utilizando o emulador desenvolvido    |          |

|      | por Carvalho em relação ao modo slave selectMAP. Nota-se que houve uma        |          |

|      | redução, em média, de 94.4% do tempo de reconfiguração em relação ao modo     |          |

|      | slave selectMAP                                                               | 76       |

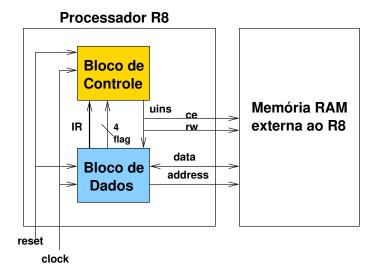

| 6.1  | Diagrama de blocos da relação entre o processador R8 e a memória              | 79       |

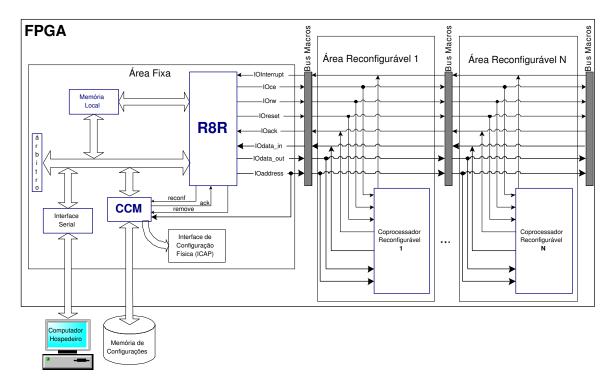

| 6.2  | Uma visão geral do sistema R8R                                                | 81       |

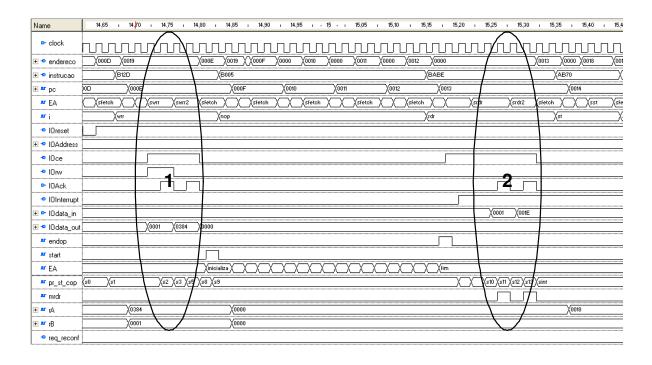

| 6.3  | Simulação funcional do coprocessador 4-avg                                    | 84       |

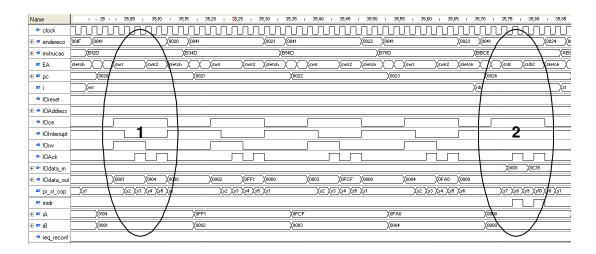

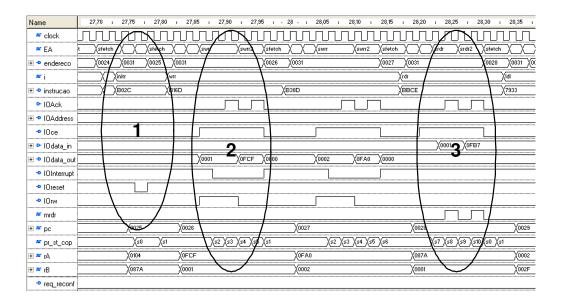

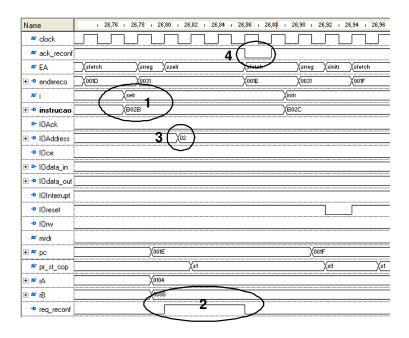

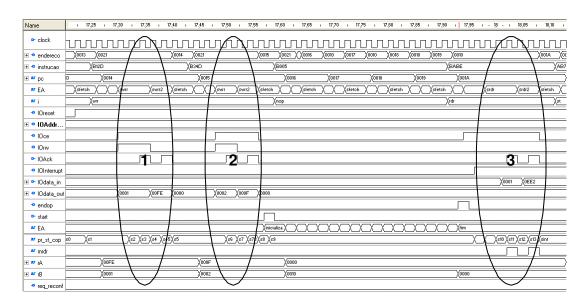

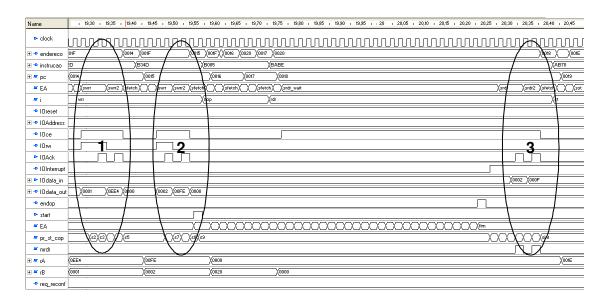

| 6.4  | Diagrama de tempos do coprocessador 2-avg                                     | 85       |

| 6.5  | Diagrama de tempos da execução da instrução SELR                              | 87       |

| 6.6  | Diagrama de tempos da execução da do módulo sqrt                              | 87       |

| 6.7  | Diagrama de tempos da execução da do módulo multi                             | 88       |

| 6.8  | Diagrama de tempos da execução da do módulo $\mathit{div}.$                   | 89       |

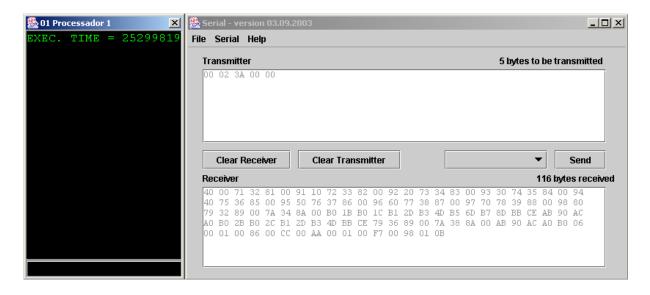

| 6.9  | Telas de aplicação do software que envia dados oriundos de um PC hospedeiro   |          |

|      | para o processador R8R                                                        | 90       |

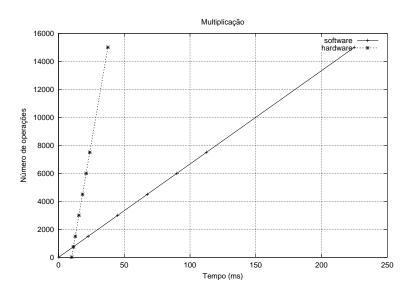

| 6.10 | Gráfico comparativo entre os tempos de reconfiguração e execução do coproces- |          |

|      | sador de multiplicação com o tempo de execução do software ambos em relação   |          |

|      | ao número de operações                                                        | 94       |

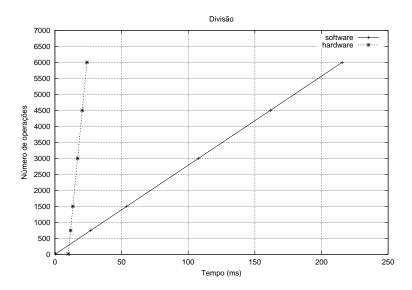

| 6.11 | Gráfico comparativo entre os tempos de reconfiguração e execução do copro-    |          |

|      | cessador de divisão e o tempo de execução do software ambos em relação ao     | <u> </u> |

|      | número de operações                                                           | 95       |

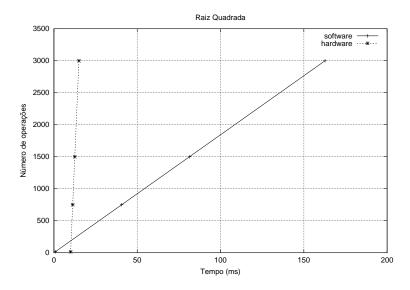

| 6. | 12 Gráfico comparativo entre os tempos de reconfiguração e execução do coprocessador de raiz quadrada e o tempo de execução do software ambos em relação |     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | ao número de operações                                                                                                                                   | 95  |

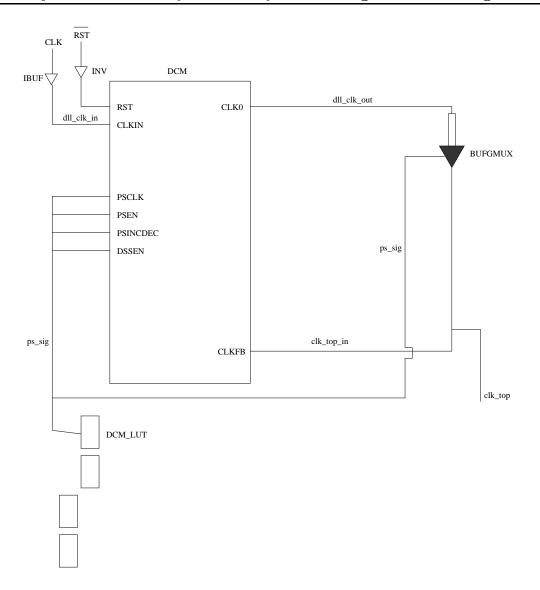

| В. | 1 Esquemático esquivalente do código VHDL apresentado para a ferramenta de                                                                               |     |

|    | posicionamento e roteamento possa realizar as conexões entre os componentes.                                                                             | 121 |

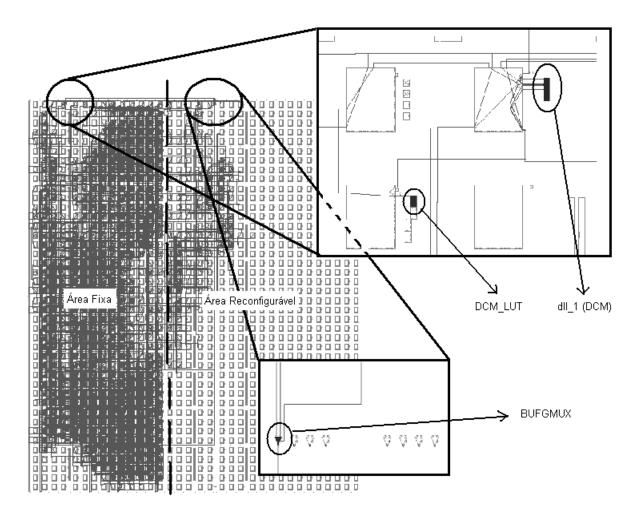

| В. | 2 Um projeto hipotético onde o módulo fixo está "espremido" à esquerda do                                                                                |     |

|    | FPGA. Os sinais que conectam os componentes DCM e BUFGMUX atravessam                                                                                     |     |

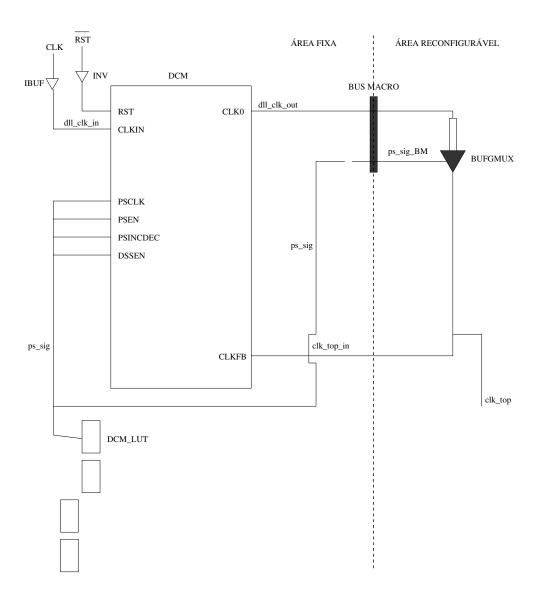

|    | a o limite entre a área reconfigurável e a área fixa.                                                                                                    | 122 |

| В. | 3 Esquemático mostrando como devem ser fixadas as bus macros no FPGA para                                                                                |     |

|    | permitir que os sinais possam interconectar os componentes DCM e buffer sem                                                                              |     |

|    | comportamentos indesejáveis na prototipação.                                                                                                             | 123 |

# Lista de Tabelas

| 2.1 | Características das ferramentas de suporte a reconfiguração parcial e dinâmica.     | 29 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.1 | Sinais básicos do OCP                                                               | 40 |

| 3.2 | Comandos de codificação do sinal MCmd                                               | 41 |

| 3.3 | Comandos de codificação do sinal $SResp.$                                           | 41 |

| 5.1 | Tempos de reconfiguração de bitstreams de tamanhos diferentes usando cabo           |    |

|     | USB                                                                                 | 74 |

| 6.1 | Instruções adicionadas para executar funções associadas ao(s) coprocessador(es)     |    |

|     | $reconfigurável(is). \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                         | 82 |

| 6.2 | Identificação dos coprocessadores reconfiguráveis através de endereços específicos. | 84 |

| 6.3 | Exemplo de sequência de instruções reconfiguráveis utilizado no software de         |    |

|     | teste (Apêndice A.1)                                                                | 91 |

| 6.4 | Conteúdo da memória do R8R logo após feita a reconfiguração parcial e exe-          |    |

|     | cucão do software.                                                                  | 93 |

## Lista de Símbolos e Abreviaturas

ACU Array Control Unit

**AMBA** Advanced Microcontroller Bus Architecture

**API** Application Programming Interface

**ASIC** Application Specific Integrated Circuit

**BRAM** Block Random Access Memory

CAD Computer Aided Design

CLB Configurable Logic Block

CPLD Complex Programmable Logic Device

CRC Cyclic Redundancy Check

$\textbf{DCM} \hspace{1cm} \textit{Digital Clock Manager}$

**DCR** Device Control Register

**DHP** Dynamic Hardware Plugin

**DISC** Dynamic Instruction Set Computer

**DSP** Digital Signal Processor

FPGA Field Programmable Gate Array

GAPH Grupo de Apoio ao Projeto de Hardware

**GPP** General Purpose Processor

HDL Hardware Description Language

ICAP Internal Configuration Access Port

IP Intellectual Property

IR Instruction Register

ISE Integrated Software Environment

**JRTR** Java Run-Time Reconfiguration

LUT Look-Up Table

NCD Xilinx Native Circuit Description

NGD Xilinx Netlist Generic Database

NIC Network Interface Card

NMC Netlist Macros

NRE Non-Recurring Engineering

OCP Open Core Protocol

**OPB** On-chip Peripheral Bus

PADREH Partial and Dynamic Reconfiguration of Hardware Project

PAR Place and Route

PC Program Counter

PCF Physical Constraints File

PIM Physically Implemented Modules

PLB Processor Local Bus

R8R Reconfigurável

RAM Random Access Memory

SDR Sistema Digital Reconfigurável

SIMD Single Instruction Multiple Data

SoC System-on-Chip

**SoPC** System-on-Programmable-Chip

SP Stack Pointer

SRAM Static Random Access Memory

SRS Semiconductor Reuse Sector

STL Sonics Transaction Language

TRCE Timing Reporter and Circuit Evaluator

${f UART}$  Universal Asynchronous Receiver/Transmitter

UCF User Constraints File

UCP Unidade Central de Processamento

**ULA** Unidade Lógica Aritmética

USB Universal Serial Bus

VLSI Very Large Scale Integration

VSIA Virtual Socket Interface Alliance

$\mathbf{XHWIF} \qquad \qquad \textit{Xilinx HardWare InterFace}$

"A receita para a eterna ignorância é muito simples e efetiva: esteja satisfeito com suas opiniões e contente com o seu conhecimento". Elbert Hubbard (1856-1915)

#### Agradecimentos

Em primeiro lugar, a Deus pelas coisas boas da vida, por minha saúde, pela minha gana e esforço no trabalho e na luta constante pela sobrevivência nos dias atuais. Agradeço a Deus por tudo que me concebeste, desde o ar que respiro até os maiores de todos os tesouros: o amor, a fraternidade e a humildade.

Aos meus pais, Lea Beatriz e Paulo Renato pelo incentivo, carinho, confiança e amizade, que mesmo estando distante, batalharam e rezaram pelo meu sucesso.

À minha avó, Suely Ceiglinski pela amizade, fraternidade, companheirismo nos cafés da tarde e apoio para o meu sucesso profissional e acadêmico.

À minha namorada, Carla Dorini pelo apoio, compreensão nos momentos de minha ausência e por seu imensurável amor e amizade nos bons e maus momentos deste período que estive morando em Porto Alegre.

Ao meu orientador, Ney Laert Vilar Calazans pelo empenho, amizade e acima de tudo, por mostrar-me o caminho da pesquisa acadêmica para que esta seja usada de maneira direta ou indireta para favorecer a sociedade como um todo.

Ao professor Fernando Gehm Moraes, pela orientação adicional, pela amizade, companheirismo e por estar disponível, quando precisei de auxílio.

Aos colegas Edson Moreno, Ewerson Carvalho e Luciano Ost pelo coleguismo e amizade no decorrer do curso. Pelos jogos de futebol, pelas conversas, pelo dia-a-dia proporcionado por estes três caras. Foram importantes no meu processo de adaptação em Porto Alegre.

Agradecimento especial para Leandro Möller, Aline Vieira, Daniel Camozzato, Luis Ries, Thiago e Rodrigo Wertonge pelas eventuais ajudas extremamente eficazes no desenvolvimento de trabalhos no grupo GAPH.

Agradeço a Kamal Patel, engenheiro da Xilinx, por me proporcionar informações valiosas para o desenvolvimento deste trabalho.

A todos que, de maneira direta ou indireta, contribuíram para o desenvolvimento deste trabalho.

À PARKS e ao CNPq por terem viabilizado este trabalho através do suporte financeiro e terem garantido a minha alimentação e manutenção em Porto Alegre.

Aos demais colegas que conheci na PUCRS e outras instituições em Porto Alegre ou fora dela, pela oportunidade de conhecer pessoas tão especiais.

Aos meus colegas de quarto que me incentivaram e trocaram conhecimentos e idéias, sempre buscando o bem comum.

Ao Estado do Rio Grande do Sul pela sua existência, pela sua cultura, pelo seu povo e por nossa identidade gaúcha, digna e cheia de glórias! Obrigado, meus pais, por proverem meu nescimento em terras gaúchas. Obrigado Deus, por ser simplesmente gaúcho!

#### Resumo

A reconfiguração de hardware apresenta-se como uma tecnologia promissora para aumentar a flexibilidade e o poder computacional de sistemas digitais complexos. Já existem no mercado dispositivos comerciais de alta complexidade que habilitam a reconfiguração de hardware de forma dinâmica e parcial, ou seja, dispositivos VLSI cujo hardware pode ser parcialmente alterado em tempo de execução, enquanto o restante do dispositivo continua a operar normalmente. Contudo, existe uma série de carências, sobretudo em ferramentas e fluxos de projeto, que inviabilizam hoje a utilização de reconfiguração parcial e dinâmica de dispositivos de hardware em larga escala. A alteração de dispositivos reconfiguráveis pode ser dividida em duas classes principais: alterações incrementais, onde a lógica, as interfaces de entrada/saída ou o roteamento de uma pequena porção do dispositivo é mudada, e a inserção e/ou remoção dinâmica de módulos complexos, onde blocos inteiros de lógica e roteamento são alterados ou susbtituídos. A primeira classe de alterações é considerada tecnologia dominada, sendo útil em aplicações restritas. A segunda é mais complexa, de aplicação mais ampla e carece de suporte adequado. A principal contribuição deste trabalho é a proposta de parte de uma infra-estrutura de suporte para o projeto e implementação de sistemas digitais reconfiguráveis complexos sobre dispositivos comerciais. Especificamente, propõe-se e implementa-se um método de geração de arquivos de configuração parciais que correspondem à implementação física de núcleos de propriedade intelectual arbitrariamente complexos. A geração é realizada de tal forma a habilitar que estes núcleos possam ser inseridos ou removidos de um dispositivo reconfigurável em tempo de execução, através de procedimentos mecânicos de reconfiguração parcial e dinâmica. O método foi desenvolvido a partir de adaptação e extensão de técnicas propostas por um fornecedor de dispositivos reconfiguráveis. Como contribuição adicional, foi proposta e implementada uma ferramenta de software para automatizar parcialmente o complexo processo de aplicação do método, aumentando o nível de abstração em que um projetista de um sistema reconfigurável atua. Um conjunto de estudos de caso de implementação de sistemas reconfiguráveis foi empregado para validar o método e seu emprego.

Palavras-chave: Reconfiguração parcial e dinâmica, Projeto Modular, Infra-estrutura de reconfiguração, interfaces de comunicação padronizadas, sistemas digitais reconfiguráveis, núcleos de propriedade intelectual, reuso.

#### Abstract

Hardware reconfiguration stands as a promising new technology to enable the increase of the flexibility and computational power of VLSI digital systems. Complex reconfigurable devices are already available in the market. Some of these support partial and dynamic reconfiguration, which means that part of the device can be changed while the rest of it remains operational. However, there are several features lacking in the design support of reconfigurable systems, which justifies why this technology has not yet become mainstream. Changing the hardware of reconfigurable devices can be achieved by means of two classes of techniques: incremental changes, where a small piece of logic, input/output characteristics and/or routing is altered, and IP core insertion/removal, where arbitrarily large blocks of the integrated circuit are replaced. The first is well known, but has limited scope of application. The second is more complex, has a larger spectrum of applicability and lacks adequate support. The main contribution of this work is the proposition of part of an infrastructure to enhance the design and implementation support of reconfigurable digital systems in commercial devices. Specifically, a method to generate partial and dynamic device reconfiguration files is proposed. Each of these files correspond to the implementation of an arbitrarily complex IP core. The generation process enables that these IP cores be inserted in a reconfigurable device at execution time through the use of standard partial and dynamic device reconfiguration techniques. The method has been developed by adapting and extending techniques proposed by a reconfigurable device vendor. As an additional contribution, a software tool was proposed and implemented to partially automate the complex process of applying the method. This increases the abstraction level in which the reconfigurable system designer interacts with the implementation process. A set of reconfigurable system case studies has been employed to validate the method and its use.

**Keywords:** Partial and dynamic reconfiguration, Modular Design, Reconfiguration framework, standard communication interfaces, reconfigurable digital system, intellectual property cores, reuse.

### Capítulo 1

# Introdução

Durante o desenvolvimento e a execução de funções computacionais por um determinado sistema, deseja-se sempre alcançar o máximo desempenho das mesmas ao menor custo final. Porém, a tarefa de atingir tais objetivos é complexa. O custo final depende de características tais como: (i) área de silício do projeto, (ii) potência dissipada pelo sistema e (iii) tempo de projeto (custos de engenharia não recorrentes, em inglês NRE costs - Non-Recurring Engineering costs). A diminuição de todas estas figuras de mérito conflita diretamente com o desempenho do sistema. Para diminuir o custo final de um sistema, o mais importante atualmente, é diminuir o tempo de projeto, embora outras figuras contribuam em maior ou menor grau, de acordo com o sistema e/ou área de aplicação específica. A dificuldade de reduzir tempo de projeto pode ser atenuada através de técnicas de reuso de projeto. Para a obtenção de reuso, módulos devem ser genéricos. Porém a generalidade seguidas vezes implica perda de desempenho para realizar tarefas específicas.

Duas formas de se obter generalidade são através de sistemas programáveis e sistemas reconfiguráveis. Os primeiros possuem a propriedade de executar software (características dos GPPs (General Purpose Processors), e os últimos alcançam generalidade ao permitir que o hardware seja alterado de forma dinâmica, apresentando a propriedade de reconfigurabilidade. Um sistema que não possua nenhuma destas propriedades pode apresentar o máximo desempenho na execução de uma tarefa como no caso de ASICs (Application-Specific Integrated Circuits). Por outro lado, é possível conceber sistemas mistos, ao mesmo tempo programáveis e reconfiguráveis. Naturalmente estes levam a um grau de flexibilidade máximo. Exemplo de um tal sistema é descrito no Capítulo 6.

Alguns pesquisadores sugerem que sistemas reconfiguráveis podem apresentar uma série de vantagens sobre sistemas com estas características. Segundo Hauck [HAU98], a computação reconfigurável possui potencial para se tornar um paradigma de propósito geral para o desenvolvimento de sistemas computacionais. Um exemplo de tal paradigma hoje é aquele em que se emprega um microprocessador ou microcontrolador associado a software. Hauck também afirma que a flexibilidade de poder inserir novas funções não apenas pela reprogramação de

software, mas também pela reconfiguração do hardware pode resultar em maiores graus de flexibilidade para sistemas. Shirazi et. al. [SHI98] estimam que o uso da reconfigurabilidade pode constituir-se em um paradigma intermediário entre ASICs e sistemas microprocessados, apresentando mais flexibilidade que os primeiros e mais desempenho que os últimos. Segundo Vissers [VIS03], a análise e a exploração de técnicas de reconfiguração dinâmica devem prover um grande passo no sentido de viabilizar plataformas de computação reconfigurável. Ainda segundo este autor, esta viabilização se dá porque tais plataformas permitem atender a compromissos de espaço e tempo sem a necessidade de reescrever e/ou ressintetizar algoritmos.

Um exemplo de dispositivos configuráveis/reconfiguráveis são os FPGAs. FPGAs (Field-Programmable Gate Arrays) são circuitos integrados compostos fundamentalmente por uma matriz de elementos lógicos configuráveis, interconexão configurável entre estes e blocos de entrada e saída configuráveis. FPGAs podem ter parte de seu hardware especializado para executar funções específicas com alto desempenho (característica de ASICs). O comportamento dos módulos funcionais em um FPGA pode também ser alterado em diferentes momentos, dependendo da necessidade (característica de GPPs).

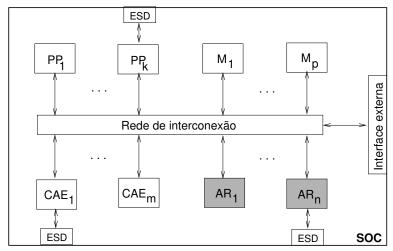

Memórias, FPGAs e microprocessadores são os três principais tipos de circuitos integrados de alto volume de produção usados como geradores de demanda de avanços tecnológicos em microeletrônica. O crescente avanço da tecnologia de implementação dos circuitos integrados (CIs) permite o desenvolvimento de dispositivos cada vez mais densos [CAL98]. Esta tecnologia de implementação viabiliza a construção de sistemas computacionais complexos integrados em um único CI o que é conhecido como SoC (System-on-Chip) [MAR01]. SoCs podem ser desenvolvidos combinando módulos tais como FPGAs, ASICs e GPPs em um único CI. Um SoC é composto por um ou mais processadores, memórias, módulos dedicados de hardware para realização de funções específicas, módulos de software e mesmo sub-sistemas micro-eletromecânicos, sub-sistemas ópticos e outros [JUN01]. Diversos setores da indústria aproveitam o potencial da combinação de tais tecnologias heterogêneas no mesmo CI [IBM02, TEN03, ALT04]. Além da heterogeneidade, outros fatores justificam o interesse por SoCs. Entre estes, pode-se citar a redução do tamanho final do produto, a redução de potência dissipada, o aumento de desempenho potencial e a segurança de projeto [MAR01]. A Figura 1.1, baseada na proposta de Madisetti e Shen em [MAD97], ilustra a arquitetura genérica de um SoC, conforme considerado neste trabalho.

O modelo de SoC usado aqui pressupõe estes compostos basicamente por núcleos de propriedade intelectual (denominados aqui núcleos IP, IPs, ou simplesmente núcleos). Núcleos IP são módulos de hardware complexos pré-caracterizados e pré-validados [BER00]. Estes devem ser reaproveitáveis, tornando viável desenvolver SoCs em tempo reduzido, gerando produtos que podem levar menos tempo para chegar ao mercado [BER00, JAC01].

SoCs podem receber denominações alternativas quando implementados sobre FPGAs. Termos como SoPC (System-on-Programmable Chip), SoRC (System-on-Reconfigurable Chip) e RSoC (Reconfigurable System-on-Chip) aparecem em abundância em publicações técnicas.

Legenda:

PP – processador programável

AR, - área reconfigurável

M<sub>i</sub> – bloco de memória

CAE, - circuíto de aplicação específica

ESD - entrada e saída dedicada

Figura 1.1: Arquitetura genérica de um SoC considerada neste trabalho. Um SoC pode conter vários processadores programáveis, blocos de memória, circuitos de aplicação específica, áreas reconfiguráveis e módulos de entrada e saída dedicados.

Um dos principais problemas enfrentados durante o projeto de SoCs é a definição de como seus IPs componentes se comunicam. Projetistas têm tradicionalmente adotado a abordagem de interconectar núcleos IP através de arquiteturas de barramento padronizadas [BER00, RIN99]. Porém, o uso destas pode limitar o reuso de IPs, pois estes devem possuir interface específica para a arquitetura de barramento escolhida. Se núcleos IP são construídos com interface específica, dificilmente podem ser empregados no contexto de outras arquiteturas de barramento sem modificações, ou mesmo em ambientes onde a comunicação não emprega barramentos. Outras limitações impostas por barramentos são a baixa escalabilidade e a sequencialidade de acesso ao recurso de comunicação [BEN02]. Uma abordagem alternativa de padronizar a comunicação é desenvolver núcleos com uma interface padrão, que não dependam do meio de interconexão escolhido. Este pode ser uma arquitetura de barramento, padronizada ou não, ou mesmo uma interconexão mais complexa, tal como uma rede intra-chip [ZEF03, MOR03a. Isto auxilia o projetista no desenvolvimento do seu núcleo, já que o mesmo pode concentrar-se no projeto do IP, e não na forma como este interage com o restante do sistema. Neste caso, não é necessário dominar o protocolo de comunicação específico utilizado, nem os sinais que compõem a interface de cada núcleo que venha a ser utilizado no projeto [OST02]. Tal abordagem é viabilizada, por exemplo, pela utilização de padrões tais como OCP (Open Core Protocol) [OCP03].

Quanto à adaptabilidade, quanto mais um núcleo é flexível e parametrizável, mais este é reusável, porém menos otimizada cada uma de suas instâncias específicas o será. Existe um compromisso entre reusabilidade e otimalidade de núcleos, segundo critérios tais como área, consumo de potência e velocidade. Um núcleo pode tornar-se um produto de sucesso se alcançar um bom compromisso entre flexibilidade e desempenho.

Quando se emprega reconfiguração, a dificuldade de se obter o compromisso ótimo entre otimalidade e reusabilidade pode ser reduzida. Isto ocorre, pois um núcleo IP ao invés de ser parametrizável, pode ser gerado em diversas versões. Para cada utilização deste IP se escolhe a versão mais adequada. Ou seja, no contexto de SoCs, reconfiguração insere um grau de liberdade a mais no projeto e no uso deste. Isto tende a melhorar a adaptabilidade do hardware ao cenário de uso, que pode assim, mesmo para uma aplicação específica, mudar dinamicamente, fazendo o SoC adaptar-se a este novo cenário.

### 1.1 Motivação

Conforme colocado anteriormente, reconfiguração dinâmica e parcial de hardware é uma tecnologia com potencial para se tornar amplamente utilizada. Esta em si é uma das principais motivações deste trabalho. Para poder contribuir neste sentido, é necessário dominar a tecnologia de modelagem, projeto, validação e implementação de SDRs o que se apresenta como a segunda motivação do trabalho.

Um dos motivos pelos quais SDRs podem se tornar mais amplamente utilizados é o fato de introduzirem graus de liberdade adicionais no projeto de sistemas computacionais. Estes graus surgem a partir da possibilidade de desenvolver sistemas cujo comportamento do hardware pode ser alterado dinamicamente, de forma similar ao que ocorre com software em sistemas programáveis. A reconfigurabilidade pode contribuir para a economia de recursos. Quando uma dada tarefa pode ser quebrada em várias fases, uma configuração diferente pode ser carregada para cada fase seqüencialmente [DEH00] operando de forma análoga à memória virtual em sistemas operacionais. Dessa forma, o tamanho do sistema pode ser menor que o necessário para implementar uma funcionalidade total, o que implica redução de custos e redução de área do dispositivo. Assim, uma outra motivação para o presente trabalho é disponibilizar dados quantitativos sobre compromissos espaço-temporais na implementação de sistemas reconfiguráveis e sistemas programáveis.

Um exemplo de emprego de reconfigurabilidade ocorre em aplicações espaciais. Alterações indesejadas na funcionalidade dispositivos eletrônicos no ambiente hostil do espaço provenientes de radiação podem acarretar erros severos na funcionalidade de tais dispositivos. Reconfigurabilidade pode ser usada, por exemplo, para corrigir erros no circuito e torná-lo tolerante a falhas [BEZ01, BEZ00, CAR00]. Existem casos em que circuitos implementados em áreas de silício danificadas por radiação são substituídos por equivalentes em outra área de um dispositivo. Pode-se elaborar módulos de teste que verificam determinados circuitos e, se estes

1.2 Objetivos 5

estão danificados, reconfiguram o FPGA [BEZ01]. Outras motivações são a economia de área em uma aplicação espacial e atualizações remotas feitas no hardware que implementa uma aplicação espacial realizadas pela reconfiguração. Fabricantes como a Xilinx e a Actel provêem FPGAs que podem ser usados em aplicações espaciais [XIL01, ACT04]. Aos compromissos espaço-temporais citados antes, pode-se acrescentar como motivação a capacidade de SDRs em particular melhorarem a característica de tolerância a falhas de sistemas computacionais e, em geral, aumentarem a flexibilidade dos mesmos.

### 1.2 Objetivos

O objetivo principal deste trabalho é propôr parte de uma infra-estrutura de reconfiguração para desenvolvimento de sistemas dinamicamente e parcialmente reconfiguráveis usando

interfaces de comunicação padronizadas. Em particular buscou-se produzir um método completo de geração de arquivos de configuração parciais e demonstrar seu efetivo funcionamento

em aplicações práticas. Esta parte da infra-estrutura de reconfiguração habilita hoje o grupo

local de pesquisa (GAPH - Grupo de Apoio ao Projeto de Hardware) que sediou este trabalho

a implementar sistemas parcial e dinamicamente reconfiguráveis.

Como objetivo secundário, é proposta e implementada uma ferramenta para incrementar a automatização do fluxo de projeto para desenvolvimento de sistemas dinamicamente reconfiguráveis.

### 1.3 Organização do Volume

- O restante do presente volume está dividido em 6 capítulos.

- O Capítulo 2 apresenta o estado da arte em SDRs, incluindo a introdução de uma proposta de terminologia, uma avaliação sucinta de trabalhos anteriores em SDRs, uma discussão das formas de reconfiguração habilitadas por sistemas atuais e uma revisão de software de suporte proposto para reconfiguração parcial de sistemas.

- O Capítulo 3 discute conceitos associados à reconfiguração baseada em núcleos IP, e ao uso de interfaces padronizadas de comunicação intra-chip, concluindo com a apresentação do contexto e da proposta de desenvolvimento contemplada por este trabalho.

- O Capítulo 4 detalha a proposta de método de projeto para geração de configurações parciais, baseado no fluxo de projeto modular da Xilinx, bem como a proposta de ferramenta de automatização parcial do método, através da ferramenta MDLauncher.

- O Capítulo 5 discute os estudos de casos simples usados na validação do método proposto e apresenta resultados obtidos com estes.

- O Capítulo 6 mostra um estudo de caso realista de um processador com conjunto de instruções extensível através do uso de co-processadores dinamicamente reconfiguráveis. Uma comparação inicial de desempenho entre implementações puramente em software e usando

hardware reconfigurável é apresentada, onde o tempo de execução em software é comparado com a soma de tempos de execução e de reconfiguração, visando estabelecer alguns compromissos entre as diferentes implementações.

Finalmente, o Capítulo 7 apresenta algumas conclusões e direções para trabalhos futuros.

### Capítulo 2

### Estado da Arte em SDRs

Este Capítulo tem como objetivo situar o leitor no que se refere ao estado-da-arte em SDRs, requisitos para habilitar o projeto e a implementação de SDRs, e ferramentas para geração de arquivos de configuração para o desenvolvimento de SDRs.

### 2.1 Definições Básicas de Reconfiguração

Sistemas reconfiguráveis combinam o desempenho de hardware dedicado a graus de flexibilidade similares a componentes de software. Sistemas programáveis estão limitados à arquitetura do microprocessador utilizado. O uso de hardware reconfigurável permite adaptar arquiteturas às aplicações [VIL97]. Para isto, funções de hardware podem ter suas características modificadas. Para tanto, é necessário realizar configuração ou reconfiguração, total ou parcial.

Uma configuração em um dispositivo ou sistema de hardware configurável é um conjunto de bits que deve ser carregado em posições de uma memória de controle para determinar as funções e a estrutura de hardware que se quer construir [MES02]. O termo configuração também pode ser usado para definir o processo descrito na última frase. A configurabilidade pode ser vantajosa, pois o hardware pode ser alterado sem a necessidade de desenvolver um outro dispositivo que atende estas novas características. Reconfiguração é o processo de alterar uma dada configuração de forma total ou parcial, mudando assim as funções desempenhadas pela estrutura do hardware. Dessa forma, a reconfiguração total é uma configuração onde a memória de controle do dispositivo reconfigurável é inteiramente sobrescrita. Reconfiguração parcial como o próprio nome diz, é o processo de configuração onde a memória de controle do dispositivo é alterada apenas parcialmente.

Segundo Sanchez [SAN99], reconfigurações podem ser dinâmicas ou estáticas. Se o sistema não necessita ter seu processamento interrompido (sem disrupção) para que uma reconfiguração seja realizada então ele é dito dinâmico, caso contrário, é dito estático.

Pode-se ainda classificar dispositivos reconfiguráveis de acordo com o tamanho do qrão

configurável. Entende-se por grão a menor unidade configurável de um dispositivo. Modernamente, se as configurações se dão no nível de portas lógicas ou funções simples booleanas de poucas variáveis diz-se que o dispositivo é de grão pequeno. Se estas se dão sobre unidades funcionais maiores, tais como ULAs, diz-se que o dispositivo possui grão médio. Quando estas se dão em unidades de porte considerável, tais como um microprocessador, diz-se que o dispositivo é de grão grande.

### 2.2 Propostas de SDRs

Estrin, em trabalho publicado nos anos 60 [EST63], propôs conceitos hoje considerados como precursores de sistemas de hardware reconfigurável.

O sistema de Estrin chamado Sistema Computador Reestruturável (Restructurable Computer System) baseia-se em um repertório de funções armazenadas em hardware. Se o programa a executar necessita uma determinada função, e esta se encontra no repertório, então a função é executada em hardware, aumentando o desempenho desta em relação à mesma implementada em instruções nativas.

O sistema de Estrin é dividido basicamente em três partes:

- Processador Central (Central Processor): Este é um processador de propósito geral, o qual executa programas convencionais. A implementação realizada usou o computador IBM7090;

- Unidade Supervisora de Controle (Supervisory Control Unit): esta unidade faz análise de instruções que estão sendo executadas no processador central. Se um determinado conjunto de instruções resulta num algoritmo "conhecido" pela unidade de controle supervisora, então este conjunto é executado pelo Inventário de Estrutura Variável.

- Inventário de Estrutura Variável (Variable Structure Inventory). Este é um repertório de funções implementadas em hardware que se encontra comumente em algoritmos para resolução de diversos problemas matemáticos que consomem muito tempo de execução. As seqüências de instruções equivalentes executadas no Inventário de Estrutura Variável têm melhor desempenho do que estas instruções executadas no processador central. Quando uma instrução é executada nesta unidade, o processador central pode estar executando o seu fluxo normal em paralelo, obtendo ganhos de desempenho no que diz respeito ao processamento de dados.

Para modificar uma determinada função no Inventário de Estrutura Variável, é necessário habilitar um conjunto de transistores ou mudanças físicas na localização dos módulos (funções implementadas em hardware) e suas interconexões. Para a construção de uma função razoalvelmente complexa, era necessário um esforço considerável para implementação da mesma [EST63].

Este foi um trabalho isolado. Somente cerca de vinte anos mais tarde, surgiram os primeiros dispositivos configuráveis comerciais.

SDRs podem ser classificados, de acordo com o número de dispositivos que os compõe, em duas grandes classes: sistemas reconfiguráveis em nível de circuito integrado e sistemas reconfiguráveis em nível de placa. Estes sistemas são discutidos nas próximas seções.

No escopo deste trabalho aborda-se apenas a reconfiguração em nível de circuito integrado usando como base o FPGA Virtex II da Xilinx [XIL01a].

#### 2.2.1 Reconfiguração parcial em nível de circuito integrado

Este tipo de reconfiguração parcial acontece sobre áreas de silício de um CI. A unidade fundamental para a reconfiguração parcial neste nível pode ser constituída por LUTs (alguns FPGAs são constituídos por esta unidade de reconfiguração). FPGAs são por excelência sistemas deste tipo. Entre estes, pode-se citar as famílias Xilinx XC6200 [?], ATMEL AT40K [ATM04] e Xilinx Virtex [XIL00].

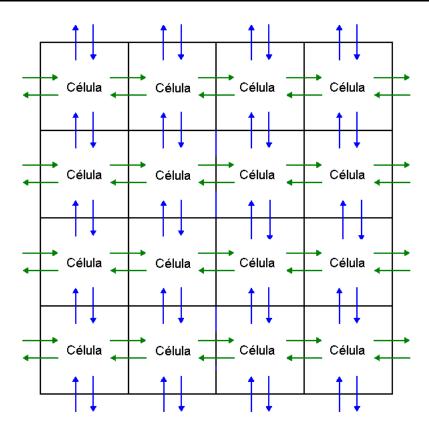

Um exemplo de FPGAs que permite a técnica de reconfiguração parcial é o FPGA XC6200 da Xilinx. Consiste em uma matriz de 64 x 64 células rodeada por portas de entrada e saída. Todas as células lógicas podem implementar qualquer função lógica combinacional de duas entradas. Cada célula pode implementar um flip-flop do tipo D com o objetivo de implementar a função combinacional da célula. As células têm um esquema de hierarquia de barramento. Células são organizadas dentro de blocos de 4 x 4, 16 x 16, etc. Um conjunto de barramentos rápidos estão associados ao tamanho do bloco. Todos os registradores que estão contidos dentro de algum bloco podem ser acessados por uma interface de usuário. Registradores são endereçados através de colunas via registrador de mapeamento. A reconfiguração é parcial e dinâmica realizada através de controle de armazenamento SRAM de seis transistores estáveis. Esta memória SRAM pode ser mapeada dentro de um espaço de endereçamento de um processador hospedeiro e suporte lógico adicional é provido para permitir reconfiguração para todas as partes do dispositivo. O FPGA XC6200 suporta hardware virtual nas quais os circuitos em execução podem ser armazenados. Isto permite que recursos do FPGA podem ser utilizados por tarefas diferentes, e então os circuitos são restaurados num dado momento, com o mesmo estado interno dos seus registradores. A Figura 2.1 mostra uma estrutura de interconexão entre as células que compõe o FPGA.

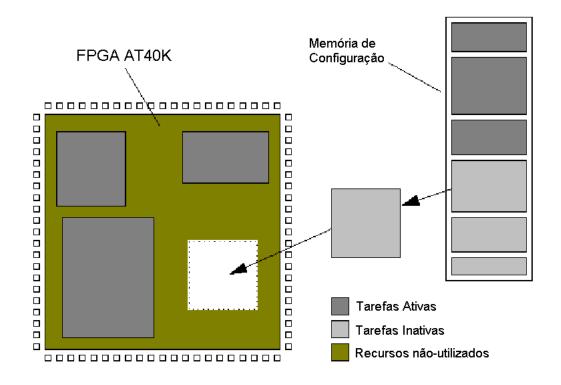

Os FPGAs da família AT40K da ATMEL foram projetados para suportarem reconfiguração parcial e dinâmica. Porém esta família de FPGAs da ATMEL suportam um máximo de 50 mil portas lógicas para implementação de projetos reconfiguráveis, ou seja, o tamanho do FPGA é pequeno comparado com o estado da arte em FPGAs de alta densidade, que excedem este valor de pelo menos duas ordens de grandeza. Este FPGA utiliza uma memória de configuração para armazenamento do contexto. Se novas funções são necessárias para a execução da aplicação, as porções antigas são sobrescritas conforme mostrado na Figura 2.2.

Figura 2.1: Estrutura de interconexão das células no interior do FPGA Xilinx XC6200.

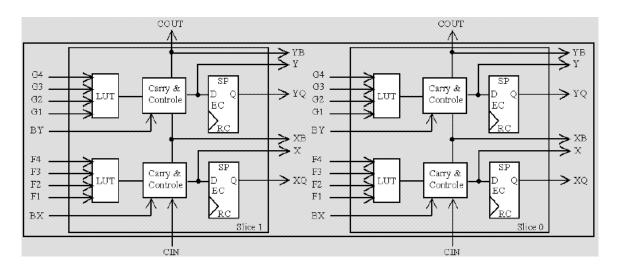

Mais recentemente, a Xilinx desenvolveu os FPGAs da família Virtex, Virtex II e Virtex II Pro. A memória de configuração da Virtex pode ser vista como uma matriz bidimensional de bits. Estes bits são agrupados em quadros verticais de 1 bit de largura, e se estendem do topo à base do dispositivo. Um quadro é a unidade mínima de configuração, ou seja, é a menor porção de memória de configuração que pode ser lida ou escrita. Quadros são lidos e escritos seqüencialmente, com endereços crescentes para cada operação. Como os quadros podem ser lidos e escritos individualmente, é possível reconfigurar parcialmente esses dispositivos através da modificação desses quadros no arquivo de configuração. Além disso, a disposição regular de elementos configuráveis permite, em teoria, relocação e desfragmentação de módulos, que têm importância no que se refere no assunto de reconfiguração parcial e dinâmica [COM02]. Os elementos configuráveis são CLBs (Configurable Logic Block), BRAMs, roteamento e multiplicadores. A Figura 2.3 mostra um CLB do FPGA Virtex XCV300.

Nesta Figura, nota-se que cada CLB contém duas fatias (slices), que por sua vez contém duas LUTs cada, além dos recursos de Carry e dois flip-flops.

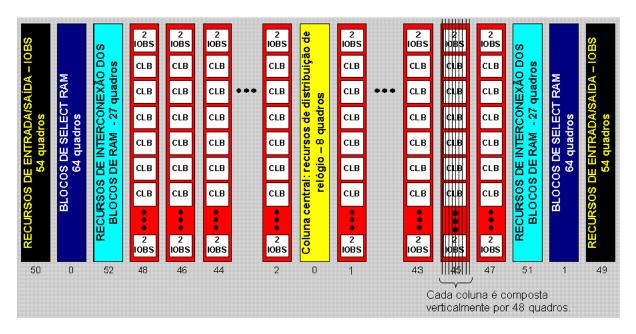

Os quadros podem ser vistos em relação a uma coluna através da Figura 2.4. Cada coluna CLB é cortada verticalmente por 48 quadros sucessivos. Como a disposição das CLBs é em colunas, a modificação de uma CLB implica na alteração de todas as CLBs da coluna a

Figura 2.2: FPGA AT40K da ATMEL, onde núcleos IP armazenados em memória configuram o FPGA em tempos diferentes.

Figura 2.3: Esquema de um CLB do FPGA XCV300.

que pertence. Nota-se ainda que as colunas são numeradas a partir do 0 (zero), atribuído à coluna central. As demais colunas são numeradas em ordem crescente, com valores pares à esquerda da coluna central, e ímpares a sua direita. A numeração é importante para o

endereçamento dos elementos. Para maiores informações sobre detalhes da arquitetura da Virtex, veja [XIL00].

Figura 2.4: Disposição em colunas dos elementos do FPGA Virtex XCV300.

Uma das famílias mais recentes dos FPGAs da Xilinx é a Virtex II. Os FPGAs desta família permitem desenvolver circuitos de  $500\times10^3$  a  $10000\times10^3$  portas lógicas.

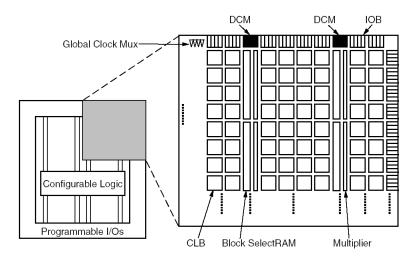

A arquitetura geral de um dispositivo da família Virtex II [XIL02] está apresentado na Figura 2.5.

Figura 2.5: Arquitetura de um dispositivo da Família VirtexII.

Na Figura 2.5 pode-se ver que os IOBs programáveis fornecem uma interface entre os pinos

externos e a lógica interna configurável. Essa lógica interna inclui quatro elementos principais, os quais são organizados em uma matriz regular:

- Os CLBs fornecem elementos funcionais para lógicas combinacionais e síncronas, incluindo elementos básicos de armazenamento. Buffers tri-states (TBUFs) são associados a cada CLB e dedicados diretamente a recursos de roteamento horizontal que podem ser segmentados.

- Módulos de memória, chamados *Block SelectRAM*, fornecem elementos de armazenamento de 18 Kbits com verdadeiras RAMs de porta dupla.

- Blocos Multiplicadores, compostos por multiplicadores de 18-bits x 18-bits.

- Gerenciador de Clock Digital (DCM), módulos responsáveis pelo sincronismo de relógio, com possibilidade de multiplicação e divisão de freqüência do relógio, e mudança de fase.

Todos os elementos programáveis, incluindo os recursos de roteamento, são controlados por valores armazenados em células de memória estática. Esses valores são carregados em células de memórias durante a configuração e podem ser recarregados a qualquer momento para modificar a funcionalidade do elemento programável.

Como já foi citado, os IOBs são programáveis. Eles podem ser vistos como um bloco de entrada com um registrador opcional, um bloco de saída com um registrador, um buffer tri-state, ou um bloco bidirecional com qualquer combinação de configurações de entradas e saídas. Os IOBs são fornecidos no perímetro de cada dispositivo em grupos de dois ou de quatro.

Os blocos lógicos configuráveis (CLBs) da família Virtex II são compostos por quatro slices (ou fatias) e dois buffers tri-states. Cada um dos slices são equivalentes e são compostos por dois geradores de funções (denominados de F e G) de quatro entradas, dois elementos de armazenamento e multiplexadores. Tais geradores podem ser configurados como Look-Up-Tables (LUTs) de quatro entradas capazes de implementar qualquer função combinacional de quatro entradas, registradores de deslocamento de 16 bits ou memória SelectRAM de 16 bits.

Os multiplexadores que fazem parte de um slice e os geradores de funções na *Virtex* II podem ser implementados como: multiplexador 4:1 em um *slice*, multiplexador 8:1 em dois slices, multiplexador 16:1 em um CLB (4 slices) e multiplexador 32:1 em CLBs.

Cada CLB contém dois dispositivos tri-state, cada um com seu próprio pino de controle e seu próprio pino de entrada. Cada um dos quatro slices tem acesso a dois tri-states através de conexões diretas. A saída do tri-state é dirigida para recursos de roteamento horizontais usados para implementar barramentos tri-state.

Cada dispositivo *Virtex* II incorpora uma quantidade de blocos de memória SelectRAM de 18 Kbits, as quais são programáveis desde 16Kx1 bit até 512x36 bits, em várias larguras

e profundidades. As SelectRAMs são de porta dupla, possuindo duas portas com clocks e controles síncronos independentes, as quais acessam uma área de armazenamento comum.

Os FPGAS da família Virtex II-Pro [XIL03] constituem uma extensão da família Virtex II. A novidade desta família é conter processadores IBM PowerPC 405 embarcados. Segundo os fabricantes, pela primeira vez os projetistas podem particionar e reparticionar seus sistemas entre hardware e software durante o ciclo de desenvolvimento de uma maneira mais flexível, ou seja, não apenas no início do projeto. O maior dispositivo desta família possui quatro processadores PowerPC embarcados.

#### 2.2.2 Reconfiguração parcial em nível de placa

Este tipo de reconfiguração é realizada em sistemas reconfiguráveis implementados sobre uma ou mais placas de circuito impresso contendo vários componentes como processadores, memórias, UARTs, barramentos e até mesmo vários FPGAs. Tais sistemas podem ser caracterizados como grão fino, médio e grosso, inclusive pode haver casos em que estes sistemas reconfiguráveis utilizam FPGAs como unidades fundamentais de reconfiguração.

A seguir, serão mostrados alguns exemplos de arquiteturas reconfiguráveis que têm como característica a reconfiguração parcial em nível de placa.

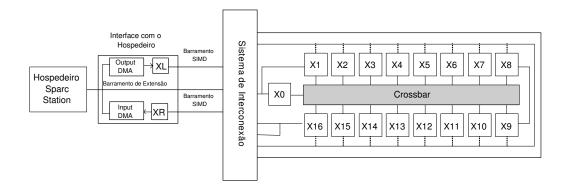

#### Splash 2

O Splash 2 é uma arquitetura reconfigurável baseada em FPGAs. Essa é constituída por 17 FPGAs 4010 da Xilinx, cada um acoplado a blocos de 512Kb de memória e um hospedeiro SparcStation. Dezesseis desses FPGAs são conectados em um vetor, e também a uma rede crossbar que introduz uma flexibilidade maior que se fosse tratado como uma matriz linear [ARN92, ARN93]. O décimo sétimo FPGA é conectado a rede crossbar e se comporta como um hardware de distribuição dos dados que recebe do barramento SIMD (Single Instruction Multiple Data). Existe também uma interface de conexão ao hospedeiro (Interface Board) que contém um relógio de sistema programável e provê acesso ao DMA para a memória do hospedeiro através de dois FPGAs (XL e XR), os quais são usados para enviar e receber dados do hospedeiro ao Splash 2. Um sistema de interconexão é usado para prover o acesso aos Splash 2 a interface de conexão ao hospedeiro. A placa Splash2 é ligada ao resto do sistema por cinco barramentos. Além do barramento SIMD, usado para transferir dados do computador hospedeiro à placa, existem dois barramentos de extensão, um barramento da dados de saída e um barramento de configuração. A arquitetura do SPLASH 2, bem como sua organização são mostradas na Figura 2.6.

O sistema Splash2 apresenta ferramentas de software baseadas em VHDL. Um simulador de Splash2 compreende um conjunto de descrições VHDL para cada um dos componentes do sistema, e pode simular o comportamento do sistema como um todo. Uma outra parte da plataforma de software é um compilador que compila código VHDL em uma netlist Xilinx, e a

Figura 2.6: Arquitetura do SPLASH 2.

otimiza para o sistema Splash2. Softwares da Xilinx fazem o roteamento e a posicionamento. Splash2 foi desenvolvido para incrementar certos aspectos do sistema Splash: escalabilidade, largura de banda para E/S e programabilidade. Tem conexões mais flexíveis que seu antecessor, apresenta rede crossbar. Assim como seu antecessor, Splash2 sofre pela baixa velocidade de integração, mas tem a vantagem da reconfiguração parcial. Esta propriedade é devida a possibilidade de reconfiguração da rede de interconexão.

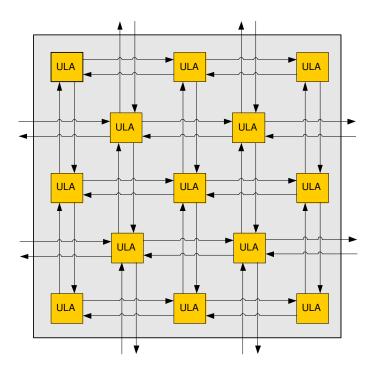

#### **CHESS**

CHESS [MAR99] é uma arquitetura reconfigurável para aplicações multimídia, desenvolvidas no Hewlett Packard Laboratories em 1999. A arquitetura do CHESS é constituída basicamente por um conjunto de ULAs (Unidade Lógica Aritmética) de 4 bits dispostas matricialmente e interconectadas (Figura 2.7). Cada ULA utiliza como entrada dados provenientes da saída de uma outra ULA. Bancos de memória externa podem ser conectados à arquitetura. Um arranjo de 512 ULAs pode ser configurado num tempo de 40 ns. CHESS oferece flexibilidade no roteamento, escalabilidade e reconfiguração parcial/dinâmica.

#### Amalgam

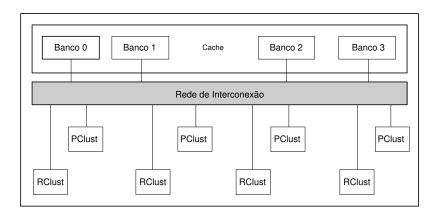

A arquitetura Amalgam [WAL02] é um exemplo de arquitetura que utiliza FPGA como unidade mínima reconfigurável. Esta arquitetura foi desenvolvida na Universidade de Illinois em 2002. Componentes como unidades de processamento programáveis e reconfiguráveis chamados clusters são integrados à arquitetura conectados a um barramento com um sistema de memória compartilhada. A arquitetura Amalgam é constituída de quatro clusters programáveis (PClust) e quatro clusters reconfiguráveis (RClust) como mostrado na Figura 2.8.

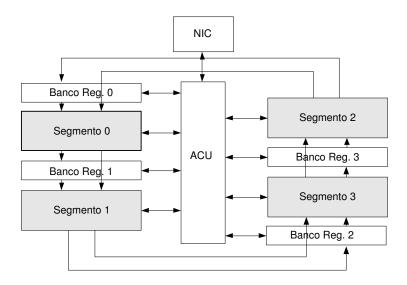

O RClust é constituído por um arranjo de blocos lógicos (32x32) de 32 bits, particionados em quatro segmentos e organizados em anel (Figura 2.9). Neste cluster, existe um controlador programável chamado de ACU (Array Control Unit), responsável pelo gerenciamento da

Figura 2.7: Arquitetura CHESS constituída por um arranjo matricial de ULAs conectadas entre si.

Figura 2.8: Arquitetura do sistema reconfigurável Amalgam.

computação e controle do fluxo de dados com a interface de rede (NIC - Network Interface Card). RClust é conectado a um banco de registradores, cada qual com portas de leitura e escrita, integrando os blocos lógicos, transparecendo ser um único sistema. De acordo com Walstrom et. al. [WAL02], cada RClust atua como um coprocessador para cada PClust.

O *PClust* contém um banco de dados de registradores, *cache* de instruções (*I-Cache*) e duas ULA's que executam um conjunto de instruções baseado no MIPS ISA.

A arquitetura Amalgam é uma nova proposta de sistemas embarcados que integra unidades programáveis e reconfiguráveis. RClust tem suporte a reconfiguração dinâmica, Porém apenas

Figura 2.9: Arquitetura do Cluster Reconfigurável.

um único contexto pode ser armazenado em cada ciclo. As configurações uma vez utilizadas são armazenadas em memória *cache*.

#### 2.3 Formas de Reconfiguração

Atualmente, existe uma carência no que diz respeito ao ferramental para desenvolvimento de sistemas dinamicamente reconfiguráveis [ZHA00]. Segundo McMillan [MCM99], existem duas iniciativas que se destacam na tentativa de solucionar este problema. A primeira delas é provida por pesquisas acadêmicas, que propõe um conjunto de ferramentas de CAD baseada em JAVA que habilita o projeto e a implementação de sistemas dinamicamente reconfiguráveis, e ferramentas para modificação de bitstreams para implementar módulos de hardware reconfiguráveis [HOR02, HOR01].

A segunda iniciativa é provida pelo setor industrial. A equipe de desenvolvimento da empresa Xilinx (fabricante de FPGAs) disponibiliza técnicas baseadas em fluxos de execução de ferramentas de síntese e implementação. Além disto, a equipe oferece classes em Java que provêem APIs (Application Programming Interface) para manipulação de arquivos de configuração (bitstream) do FPGA, de modo a torná-los parcialmente reconfiguráveis.

#### 2.3.1 Reconfiguração baseada em alterações incrementais

Este método de reconfiguração baseado na técnica Small Bit Manipulation, descrita através da XAPP290 [LIM03], consiste em modificar apenas alguns quadros que constituem o FPGA. A idéia central é gerar bitstreams parciais usando a diferença de um bitstream total e modificações feitas num arquivo que posteriormente é lido pela ferramenta geradora de

bitstreams denominada *BitGen*. A ferramenta de edição do FPGA (FPGA *Editor*) permite a modificação das funções contidas em uma ou mais LUTs. Dados de BRAMs (*Block RAM*) e pinos de I/O também podem ser manipulados em nível de bits e modificados dinamicamente. Isto é útil para aplicações reconfiguráveis que necessitam de pequenas alterações pontuais. Porém esta técnica é extremamente penosa para desenvolvimento de arquivos de configuração que armazenam módulos de hardware. Para a geração de bitstreams parciais que representam módulos inteiros de um dado projeto, a Xilinx recomenda o uso do fluxo do Projeto Modular [XIL01b] apresentado no Capítulo 4.

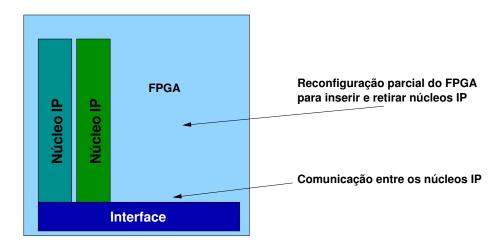

#### 2.3.2 Reconfiguração baseada na inserção/remoção de núcleos

Este método de reconfiguração consiste em reconfigurar parcialmente núcleos IP que podem ocupar os mais variados tamanhos no FPGA. A Figura 2.10 mostra alguns núcleos IP conectados a uma interface de comunicação. O objetivo é possibilitar que os núcleos IP possam ser inseridos e removidos (plug-and-play) dinamicamente sem afetar o resto do sistema. A entrada para a execução deste método de reconfiguração é um sistema descrito em HDL, e a execução desse método gera arquivos de configurações totais e parciais, habilitando então a reconfiguração parcial e dinâmica nesse sistema.

Figura 2.10: Núcleos IP reconfiguráveis conectados a uma interface de comunicação.

Porém existe uma carência de ferramentas para a execução de tal método. Na bibliografia, existem poucos fluxos e ferramentas para desenvolvimento de projetos dinamicamente reconfiguráveis. Esses fluxos para habilitação da reconfiguração baseada em núcleos IP são descritos mais detalhadamente na Seção 3.1. Como inconvenientes. o uso de recursos adicionais do FPGA para prover comunicação entre os núcleos IP e problemas quanto a erros eventuais de roteamento do sistema, cujo usuário deve fazer o roteamento manualmente.

#### 2.4 Requisitos para Habilitar SDRs

O presente trabalho enfoca a reconfiguração parcial em nível de CI apenas (Seção 2.2.1). Além disto, pressupõe-se que o processo de reconfiguração é baseado em inserção/remoção de IPs (Seção 2.3.2).

Para a realização de reconfiguração parcial em dispositivos reconfiguráveis, é possível identificar seis requisitos:

- FPGAs que suportam reconfiguração parcial e dinâmica: atualmente dois fabricantes de FPGAs oferecem suporte para reconfiguração parcial e dinâmica: Atmel e Xilinx. Atmel produz os FPGAs das famílias AT40K e AT6000. Estes FPGAs são inadequados para o desenvolvimento de SoCs, por causa do seu tamanho reduzido em relação ao número de unidades fundamentais de reconfiguração (LUTs). Por outro lado, os FPGAs da Xilinx disponibilizam as famílias Virtex, Virtex-II e Virtex-II Pro. A unidade atômica de reconfiguração se chama quadro. Este compreende em uma seção vertical que se extende por todo o FPGA. Um núcleo IP é fisicamente implementado nestes dispositivos da Xilinx como um conjunto de quadros consecutivos;

- Ferramentas para determinar a forma e a posição do núcleo IP: restrições de posicionamento devem ser inseridas durante o projeto de SDRs para a definição do tamanho, formato e posição dos núcleos IP reconfiguráveis. ex: Floorplanner da Xilinx;

- Suporte para geração de arquivos de reconfiguração parciais e configuração destes no FPGA: protocolos de reconfiguração parcial e total são distintos. Características especiais devem estar presentes nas ferramentas e dispositivos usados para reconfigurar parcialmente os FPGAs;

- Interface de Comunicação entre Núcleos IPs: em um projeto de SoC convencional, arquiteturas de barramento intra-chip padronizadas, tais como AMBA e CoreConnect podem ser usadas para prover comunicação entre os núcleos IPs. Entretanto, estas arquiteturas não apresentarem características necessárias em SDRs, como isolamento de núcleos IPs durante a reconfiguração. Para habilitar a inserção e remoção dinâmica de núcleos IPs dentro do FPGA em operação, uma interface de comunicação para conexão e isolamento de núcleos em momentos distintos deve ser usada. Esta interface deve prover funções diversas tais como arbitragem, comunicação entre módulos, virtualização dos pinos de entrada e saída e controle de configuração;

- Virtualização dos pinos de entrada e saída: este conceito permite troca de dados entre o núcleo IP reconfigurável e o meio externo sem alteração das características de pinagem do CI;

• Controle de reconfiguração dinâmica: Métodos para controle ou execução do processo de reconfiguração dinâmica são um requisito imprescindível. Estes métodos podem ser implementados em hardware, software ou ambos [CAR04].

#### 2.5 Suporte de Software para Reconfiguração Parcial

A geração de arquivos de configuração parciais apresenta-se como uma tarefa crucial para o desenvolvimento de SDRs. Os fabricantes fornecem junto com seus dispositivos ambientes de CAD para desenvolvimento de sistemas que contém, muitas vezes, diversas ferramentas. Dentre estas, algumas se dedicam à geração de arquivos de configuração parciais.

O fluxo de geração de arquivos parciais com ferramentas fornecidas pelos fabricantes deve ser realizado, ainda hoje de forma manual. Por isso, trata-se de um processo demorado e complexo, passível de erros, para projetos que necessitam de diversas configurações parciais. Necessita-se, portanto, de ferramentas mais automatizadas para o projeto de sistemas reconfiguráveis.

Nesta Seção, apresentam-se algumas ferramentas que tem por objetivo auxiliar projetistas na tarefa de gerar arquivos de configuração parciais.

#### 2.5.1 Conjunto de classes JBits

JBits é um conjunto de classes Java que fornecem uma API que permite manipular o arquivo de configuração das famílias de FPGAs Virtex e Virtex-E da Xilinx [GUC99]. Esta interface opera tanto em arquivos de configuração gerados pelas ferramentas de projeto da Xilinx quanto em arquivos de configuração lidos do hardware (Readback). Para que este conjunto de classes possa dar suporte à reconfiguração parcial e dinâmica, 3a ferramenta deve ser rápida e prover informações físicas detalhadas a respeito da arquitetura do hardware, bem como elementos arquiteturais reconfiguráveis do dispositivo a ser configurado. Isto permite que os circuito seja reconfigurado sem a necessidade de se refazer o posicionamento e o roteamento com ferramentas convencionais oferecidas pelos fabricantes de FPGAs.

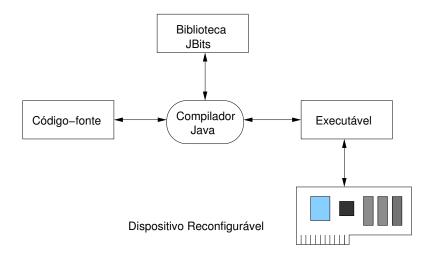

A Figura 2.11 ilustra o fluxo de projeto do JBits. Neste fluxo, um compilador de Java lê o programa descrito pelo usuário com as classes para acesso ao FPGA. o compilador também lê dados da biblioteca do conjunto de classes JBits. O compilador gera um código executável que fornece o controle de configuração e dados para a lógica de reconfiguração do dispositivo. Neste fluxo de projeto, o arquivo executável gerado pelo compilador Java é somente um componente arbitrário do código Java compilado. Este executável permite desenvolver aplicações em software para acessar a aplicação reconfigurável no dispositivo. A informação de controle ou de dados pode ser compartilhada entre o computador hospedeiro e o FPGA.

A Figura 2.12-a apresenta uma aplicação escrita em JAVA desenvolvida pelo usuário. O diagrama da Figura 2.12-b é dividido em três níveis de abstração. O nível de abstração

Figura 2.11: Fluxo de projeto do JBits para prover controle e dados de configuração.

mais baixo, apresentado na Figura 2.12-b.3, representa uma classe denominada Bitstream que gerencia o arquivo de configuração do dispositivo e disponibiliza suporte para leitura e escrita das configurações dos arquivos. Em seguida, o nível de abstração intermediário, apresentado na Figura 2.12-b.2, representa a classe Interface em Nível de Bit. Este nível é responsável por ocultar características específicas relativas a dispositivos diferentes de uma mesma família. Também, neste nível, é possível modificar até um único bit no arquivo de configuração. O nível de abstração mais alta (JBits) provê uma abstração que permite a modificação de conjunto de bits no arquivo de configuração através de uma ou mais chamadas de métodos da classe Interface em Nível de Bit. A API JBits utiliza o software XHWIF (Xilinx HardWare InterFace) para configurar o dispositivo e realizar leituras através deste. (Figura 2.12-d).

Finalmente, o módulo mostrado na Figura 2.12-e, utiliza uma biblioteca de núcleos IP (conjunto de classes em JAVA) que podem ser adicionados ou removidos do dispositivo.