Pontifícia Universidade Católica do Rio Grande do Sul Faculdade de Engenharia Faculdade de Informática Curso de Engenharia de Computação

# HNPlus – A Network on Chip Prototyping Platform with a Generic Traffic Generation Scheme

Bruno Fin Ferreira Ismael Luís Heinen

END OF TERM WORK

Prof. Dr. Ney Laert Vilar Calazans Advisor

> Porto Alegre 2011

# **CONTENTS**

| Co | NTENTS                                           | 3  |

|----|--------------------------------------------------|----|

| LI | ST OF ABBREVIATIONS                              | 5  |

| LI | ST OF FIGURES                                    | 7  |

| 1. | INTRODUCTION                                     | 9  |

|    | 1.1 Motivation                                   | 9  |

|    | 1.2 Objectives                                   | 9  |

|    | 1.2.1 Strategic Objectives 1                     | 0  |

|    | 1.2.2 Specific Objectives 1                      | 0  |

|    | 1.3 Organization of the Document1                | .0 |

| 2. | BASIC CONCEPTS1                                  | 1  |

|    | 2.1 NoCs                                         | .1 |

|    | 2.2 The GALS Style and the Hermes-GLP NoC1       | .2 |

|    | 2.3 ATLAS                                        | .3 |

|    | 2.4 Analysis by Emulation1                       | .4 |

|    | 2.5 The Original HardNoC Platform1               | .5 |

|    | 2.5.1 The HardNoC Block Diagram 1                | 5  |

|    | 2.5.2 The HardNoC Packet Formats 1               | 5  |

|    | 2.5.3 Link Layer Packet Format 1                 | .6 |

|    | 2.5.4 NoC Network Layer Packet Formats 1         | .6 |

|    | 2.5.5 Network Layer System Packet Formats 1      | .7 |

|    | 2.5.6 The TG IP Core 1                           | .8 |

|    | 2.5.7 Using HardNoC 1                            | .9 |

|    | 2.5.8 HardNoC-GLP 1                              | .9 |

| 3. | RELATED WORK                                     | 0  |

|    | 3.1 HW/SW Emulation Platforms2                   | 0  |

|    | 3.2 Emulating Different NoCs without Resynthesis | 1  |

| 4. | THE HNPLUS PLATFORM                              | 2  |

|    | 4.1 TG2                                          | 2  |

|    | 4.2 Software                                     | 8  |

|    | 4.3 The HNPlus Platform Operation                | 0  |

| 5. | VALIDATION, PROTOTYPING AND EXPERIMENTATION      | 2  |

|    | 5.1 Overview of HNPlus Operation                 | 2  |

|    | 5.2 Validation                                   | 3  |

| Re | FERENCES                                                     | 45 |

|----|--------------------------------------------------------------|----|

|    | 6.1 Future Work                                              |    |

| 0. |                                                              |    |

| 6  | CONCLUSION AND FUTURE WORK                                   |    |

|    | 5.4.2 Two TGs Sending Packets to the Same Target             | 42 |

|    | 5.4.1 One Source TG Sending Packets to Two Different Targets | 41 |

|    | 5.4 Experimentation                                          | 40 |

|    | 5.3 Prototyping                                              |    |

|    | 5.2.6 End of Packet Reception during Emulation               |    |

|    | 5.2.5 End of Packet Sending during Emulation                 | 37 |

|    | 5.2.4 Steady State Emulation Operation                       |    |

|    | 5.2.3 Emulation Packet Reception                             | 35 |

|    | 5.2.2 Start of HNPlus Emulation                              |    |

|    | 5.2.1 TG Programming and Pre Reading                         | 33 |

# LIST OF ABBREVIATIONS

- BRAM Block RAM

- FIFO First In First Out

- **FPGA** Field Programmable Gate Array

- GALS Globally Asynchronous Locally Synchronous

- GAPH Grupo de Apoio ao Projeto de Hardware

- GLP GALS Low Power

- HDL Hardware Description Language

- HW Hardware

- IC Integrated Circuit

- IP Intellectual Property

- NoC Network on Chip

- RAM Random Access Memory

- SoC System on a Chip

- SW Software

- **TG** Traffic Generator

- TI Traffic Injector

- TR Traffic Receptor

- VC Virtual Channel

- VHDL VHSIC Hardware Description Language

- VHSIC Very-High-Speed Integrated Circuit

# LIST OF FIGURES

| Figure 2.1 – General structure for describing traffic in ATLAS traffic files                                     |

|------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 – The original HardNoC system block diagram16                                                         |

| Figure 2.3 - The HardNoC link protocol layer and its packet format                                               |

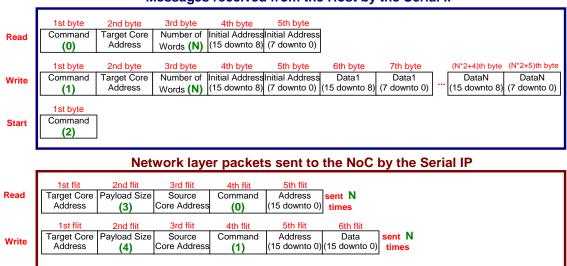

| Figure 2.4 - HardNoC TG/Serial IP NoC network layer packet formats. In the Data packet format,  Data             |

| stands for the size, in flits, of the variable size Data part of the packet, from the ninth flit on. Only the    |

| Serial IP generates the first two formats, and only TGs generate the last two formats                            |

| Figure 2.5 - Messages received from the host computer by the Serial IP and corresponding packets sent to         |

| the NoC by the Serial IP                                                                                         |

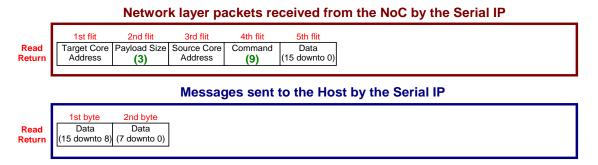

| Figure 2.6 - Packets received from the NoC by the Serial IP and corresponding data sent to the Host              |

| computer                                                                                                         |

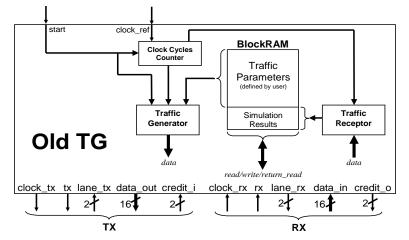

| Figure 4.1 - The HardNoC TG structure                                                                            |

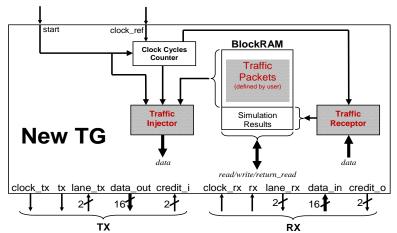

| Figure 4.2 – The HNPlus TG structure                                                                             |

| Figure 4.3 – The HNPlus Packet format23                                                                          |

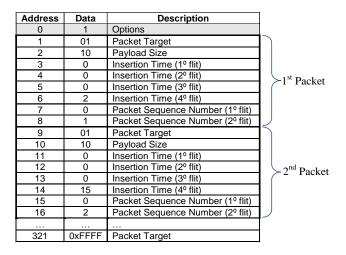

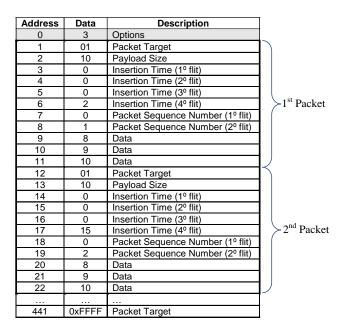

| Figure 4.4 – Memory organization example, describing a traffic with 40 packets, without real data24              |

| Figure 4.5 - Memory organization example, describing traffic with 40 packets containing real data traffic.24     |

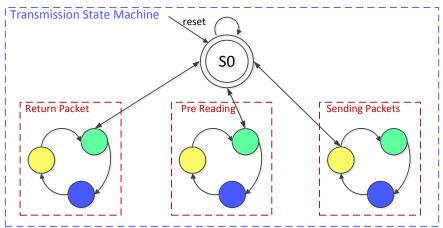

| Figure 4.6 – Operating modes of Transmission State Machine                                                       |

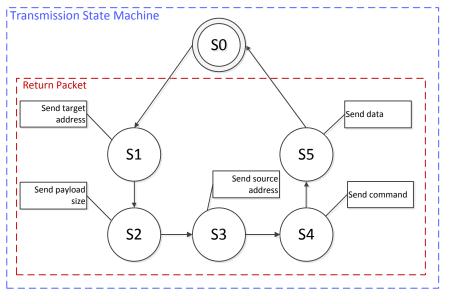

| Figure 4.7 – Return Packet States                                                                                |

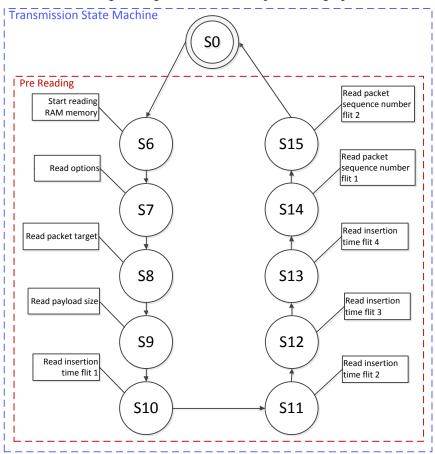

| Figure 4.8 – Pre Reading States                                                                                  |

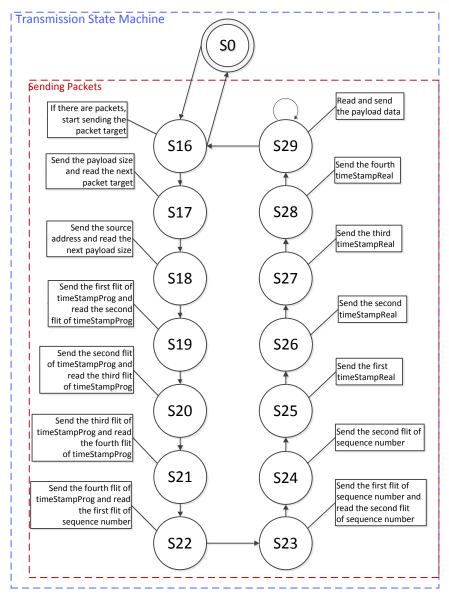

| Figure 4.9 – Sending Packet States27                                                                             |

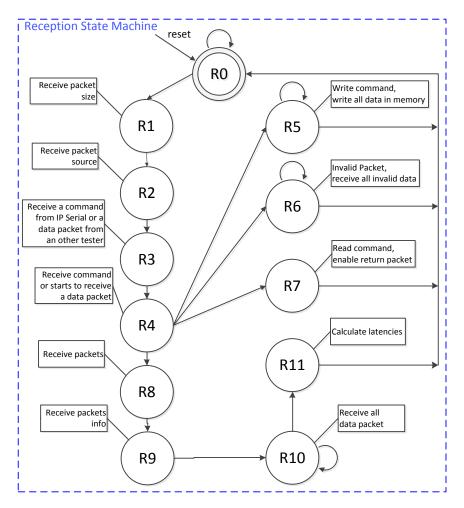

| Figure 4.10 – Reception State Machine                                                                            |

| Figure 4.11 – HardNoC, old host software29                                                                       |

| Figure 4.12 – The HNPlus host software, showing contents of the traffic file generated by ATLAS29                |

| Figure 4.13 – The HNPlus host software, showing the obtained statistical results                                 |

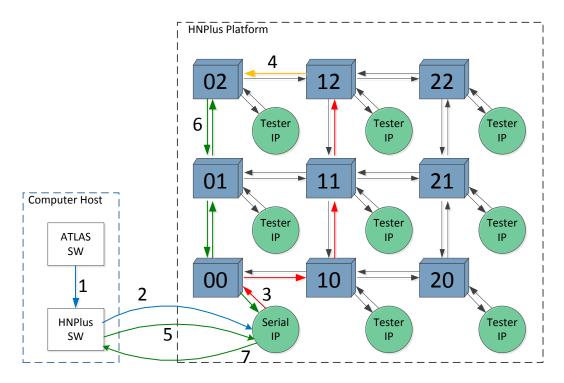

| Figure 4.14 – HNPlus platform operation overview                                                                 |

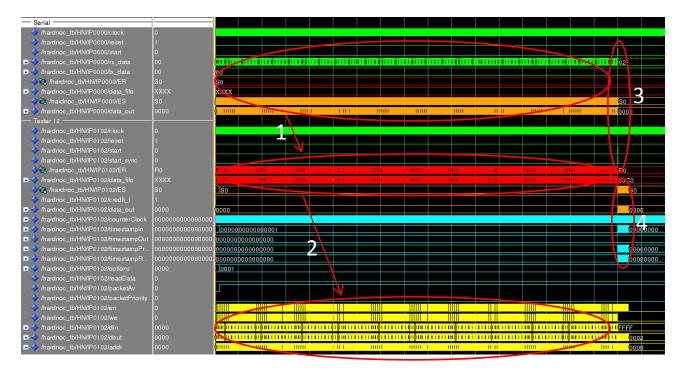

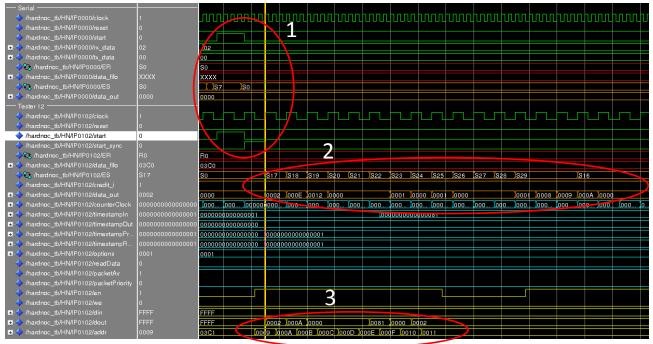

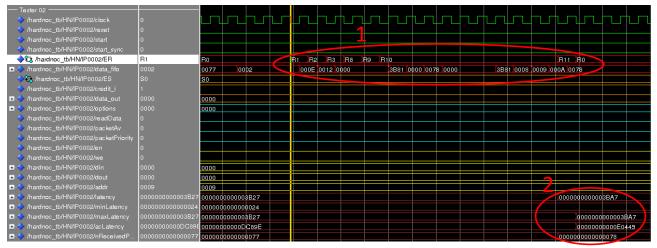

| Figure 5.1 – An overview of a complete simulation of the HNPlus platform: Serial IP programs the TG,             |

| followed by start signal generation and the emulation process                                                    |

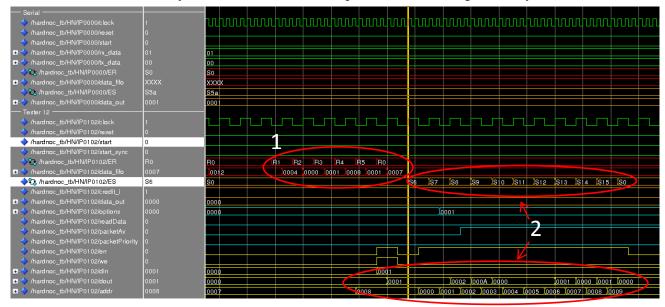

| Figure 5.2 – TG receiving the last header information of the first packet from Serial IP and activation of pre   |

| reading                                                                                                          |

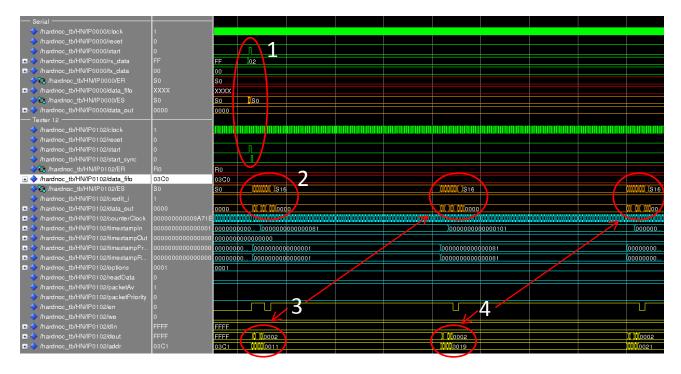

| Figure 5.3 – Start signal reception, injection of the first packet in the first clock cycle and parallel reading |

| of the second packet                                                                                             |

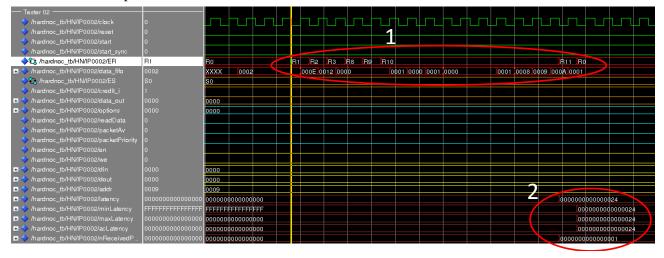

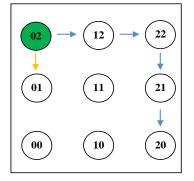

| Figure 5.4 – TG 02 receiving the first packet from TG 12                                                         |

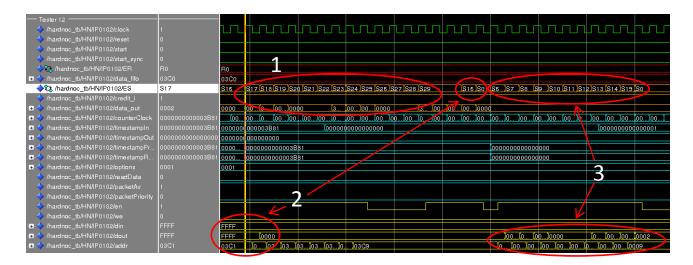

| Figure 5.5 – Overview of the simulation start, showing start signal processing, the first three packets being    |

| sent and the pre readings                                                                                        |

| Figure 5.6 – Sending the last packet of traffic, the identification by parallel reading of the traffic end and   |

| the pre reading activation to prepare for a possible repetition of emulation                                     |

| Figure 5.7 – TG 02 receiving the last packet of a traffic                                                        |

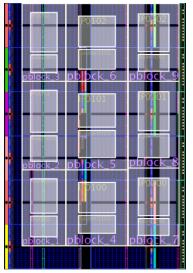

| Figure 5.8 – Floorplanning used to optimize the physical synthesis of HardNoC-GLP and HNPlus                     |

| Figure 5.9 – HardNoC-GLP physical synthesis report using a 3x3 Hermes-GLP40                                      |

| Figure 5.10 - HNPlus physical synthesis report using a 3x3 Hermes-GLP              | .40  |

|------------------------------------------------------------------------------------|------|

| Figure 5.11 – First traffic is the blue path and second traffic is the orange path | .41  |

| Figure 5.12 – Statistical results, after first traffic emulation                   | . 42 |

| Figure 5.13 – Statistical results, after second traffic emulation                  | .42  |

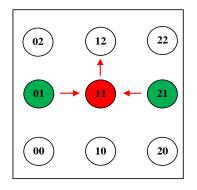

| Figure 5.14 – Traffic scenario used to cause a traffic hotspot on node 11          | .43  |

| Figure 5.15 - Statistical results obtained after hotspot emulation                 | .43  |

# **1. INTRODUCTION**

The evolution of the technologies used to fabricate integrated circuits (ICs) brought the possibility of implementing hundreds of millions of transistors in a single chip. Thus, modern ICs can contain all elements of a complex system in a single chip. Such devices receive the name of Systems on a Chip (SoCs) [MOR10]. A SoC is typically composed of information processing modules (the so-called intellectual property cores or IP cores), an intrachip interconnect architecture and interfaces for peripherals of the IC.

Traditional intrachip interconnect architectures, such as dedicated wires and buses, can be considered insufficient for current SoCs. Dedicated wires have poor reusability and flexibility, while shared buses transmit only one data per clock cycle and offer limited scalability. The emerging Network-On-Chip (NoC) interconnect architecture provides an energy-efficient and scalable communication solution for multiple cores, serving as a powerful replacement for bus architectures. Multiple point-to-point data links interconnected by switching nodes typically compose an NoC. Any source module may relay messages to any destination module over several links, by making routing decisions at the switching nodes or at the message's source.

Due to increase in inter-module communication requirements and demand for reduced time-to-market, validation of intrachip communication infrastructures plays a major role in chip design [LOT11]. Typically, software or HDL simulators accomplish the validation process. The increasing complexity and size of NoCs mandate that simulation software deals with too many signals and data, making the validation process take a significant fraction of the overall chip design time, maybe affecting accuracy. In addition, real application speeds are not possible with software simulators. Fast, cycle-accurate FPGA emulators are an alternative to software simulators as they reduce validation time without compromising accuracy. FPGA emulators allow the user to exploit the parallel nature of hardware, thereby enabling the detection of design and architectural problems early and reducing the number of chip respins [LOT11].

### **1.1 Motivation**

The increasing complexity of NoCs can difficult the process of validating them by software simulator because of time consumption that it takes. Instead, validating complex NoCs by emulation platforms can be a solution, once emulation in hardware can present a three or more order of magnitude gain in terms of time execution when compared to software simulators. Besides this, platforms based in FPGAs are powerful, simple to use and are available to execute this work.

## 1.2 Objectives

The main objective of this work is to contribute to the validation process of NoCs, by ameliorating an existing NoC evaluation hardware environment, named HardNoC-GLP. The specific goal is the development of a new traffic injector module for an existing environment, making the necessary adjustments and enhancements in the system to ensure its correct operation.

#### 1.2.1 Strategic Objectives

During its development, this work achieved several strategic objectives. Examples are the exploration and understanding of how NoC emulation platforms work, the use of HDL-based hardware design techniques and the dominium of FPGA prototyping techniques. The achievement of these objectives required the use of much of the knowledge acquired during the Computer Engineering course, applying concepts from various disciplines. This included concepts of software development, communication networks, digital circuits, computer organization and architecture, microelectronics and circuit design techniques that were revisited and solidified. Applying such knowledge to this work gave the authors additional experience, close to that needed to develop commercial products.

#### 1.2.2 Specific Objectives

The specific objectives involved enhancing the existing HardNoC-GLP platform, developed at the GAPH research group, to support the standard traffic description files produced by the ATLAS NoC design and verification environment. The new platform denomination is HNPlus. After concluded the development work, it was possible to validate and test instances of a specific NoC (the Hermes-GLP) with several traffic patterns distinct from those previously possible. While the original HardNoC-GLP platform worked with only two traffic types, the improvement this work proposed and implemented enables the exercise of NoCs with virtually any traffic type, incuding real traffic data, what makes the exploration of new NoC designs more flexible. Additionally, this work provides en anhancement in the software used to provide interaction between the user and the HNPlus platform. The new software improves the original interface, rather crude and difficult to use, by an interface that adds semantic meaning to the NoC packet structure.

### **1.3 Organization of the Document**

The rest of this work comprises five additional chapters. Chapter 2 describes the basic concepts used along the text. Chapter 3 describes related work. Chapter 4 presents the proposed architecture and its development details. Chapter 5 presents the validation and prototyping of the new platform beyond experiments and some analysis of the results obtained with it. Chapter 6 contains some conclusions and directions for future work.

# 2. BASIC CONCEPTS

This Chapter explores basic concepts of the main subjects involved in this work. The presentation comprisers five Sections. General concepts include NoCs, addressed in Section 2.1, and globally asynchronous locally synchronous basics and a brief account of the Hermes-GLP NoC both in Section 2.2. The used traffic generation environment, ATLAS, is the focus of Section 2.3. Follows a brief definition and discussion of concepts related to emulation of digital systems, in Section 2.4. The Chapter ends with a brief presentation of the original HardNoC platform, in Section 2.5.

### 2.1 NoCs

Given the limitations of dedicated wires and buses in intrachip communication architectures of current ICs, NoCs are emerging as a solution to existing interconnection architecture constraints, due to the following NoC good characteristics: (*i*) energy efficiency and reliability; (*ii*) scalability of bandwidth when compared to traditional bus architectures; (*iii*) reusability; (*iv*) distributed routing decisions [MOR04].

NoCs use concepts of telecommunication networks and parallel processing networks, where information is organized and transferred in layers and protocols. Switching nodes and links compose a network. The exchange of messages among IP cores accomplishes the exchange of information between source node and target nodes of a system. Often, the structure of some message types is not adequate for communication purposes on NoCs. This leads to the concept of packet. A packet is a standard way of representing information in a form adequate for communication. One packet may correspond to a fraction, one or even several messages. In the context of NoCs, packets are frequently a fraction of a message. A header and a payload often compose packets. The switching nodes realize the transfer of information between the IP cores by routing the packets accordingly to get them closer to their destination IP cores. To do so, switching nodes comprise a switching fabric, a routing logic, an arbitration logic, and associated communication ports connecting through links to neighbor switching nodes, depending on the network topology. A network topology is defined by the way switching nodes connect to one another. A very popular network topology is the 2D Mesh topology, where switching nodes occupy two dimensions forming a square or a rectangle where nodes connect to neighbors in vertical and horizontal directions. The communication mechanism, the switching mode and the routing algorithm are functions of the network topology and are necessary items to the execution of services provided by the NoC.

The *communication mechanism* specifies how messages travel through the network. Two methods for transferring packets are *circuit switching* and *packet switching*. In *circuit switching*, a path from source to target is established by the allocation of a sequence of switching nodes. This is a *connection*. Packets start to travel through the allocated path and, during this connection, any other communication desiring to use any of the allocated path segments is denied. In *packet switching*, packets follow along the network without any need for deploying connection establishment procedures.

A packet switching mechanism requires the use of a *switching mode*, which defines how packets move along switches. *Store-and-forward*, *virtual-cut-through* and *wormhole* are the most important modes. In *store-*

*and-forward* mode, a switch just forwards a packet when it has been completely received. The switch decides what to do every time a packet comes in. In *virtual-cut-through* mode, the switch needs a guarantee from the next switch that the packet can be received completely. It implies in a buffer to store the complete packet. The *wormhole* switching mode is a variant of the virtual-cut-through mode that avoids the need of large buffer spaces. In this mode, a packet is divided into smaller units, called flits. A *flit* is the smallest unit of flow control. Only the header flit has the routing information. The rest of the flits of the packet must follow the same path reserved for the header.

The *routing algorithm* defines the path a packet takes to go from the source to the target. It is possible to classify a routing algorithm in *source* or *distributed*, depending on where the decisions are taken. In *source* routing the whole path is decided at the source switch node while in *distributed* routing the path is decided by a set of local decision taken at every switch. The *XY algorithm* can be a source or distributed routing algorithm that routes flits according to the position the switch occupies on the network topology, usually 2D Mesh. First, the XY algorithm checks if the incoming flit has arrived at its target. If so, the flit is routed to the switch's local port, typically connected to an IP core. If not, the XY algorithm routes the flit to a switch closer to the target always sending it to a horizontally located neighbor. The flit is sent up or down only if there is no horizontally located neighbor or if the existing ones are farther from the target.

Besides the communication system, a NoC provides communication services to the SoC. As essential services to a SoC, it is possible to cite data integrity, throughput and latency guarantees. In the context of NoCs, latency is the time a packet takes to go from the source to the target. If divided in flits, as in wormhole mode, latency is the time delay from the insertion of the first flit in the NoC until the time the last flit composing the packet leaves the NoC.

### 2.2 The GALS Style and the Hermes-GLP NoC

Due to the facility of implementation and verification, the use of a single clock signal in digital system design has been widely used along the years. This approach, however, brings some undesired issues, like clock distribution problems, clock skew and clock power consumption. It was easy to deal with these problems until the 80's, but they became a major limitation with the technology scaling of VLSI circuits into deep submicron geometries.

As an alternative to the synchronous design style, the asynchronous style treats time as a continuous variable, creating the possibility to solve clock skew and clock power problems. Completely asynchronous systems, though, are limited by a generalized shortage of adequate design automation (computer aided design or CAD) tools.

A strategy applicable to fill the gap between synchronous and asynchronous design is the adoption of globally asynchronous locally synchronous (GALS) techniques [CHA84]. The adoption of GALS keeps the use of synchronous methods and CAD tools for the design of synchronous modules and transfers all synchronization problems to the interface between modules. In this context, some NoCs with GALS communication support have become popular [VAN08].

The proposition of the Hermes-GALS Low Power NoC (Hermes-GLP) NoC [PON08] intended to support the GALS paradigm, and at the same time reduce power consumption using mechanisms that dynamically adapt the operating conditions of routers in response to communication requirements [PON08].

Hermes-GLP builds upon the synchronous Hermes NoC [MOR04] and includes bi-synchronous FIFOs for communication between each pair of routers and between a router and its local IP Core.

Each Hermes-GLP router is locally synchronous, with all its ports switching at the same clock frequency. The communication between the router's ports and the rest of the NoC, however, passes through a bi-synchronous FIFO, because the rest of the NoC could be using different clock signals. This occurs because the router has available a set of input clock signals and through an internal logic is capable to choose among these different clocks which to use as router clock. Clock selection is made at runtime, according to the priority of all traffics instantaneously passing through the router. If the priority associated with the traffic set is low, the router automatically selects a lower frequency to operate, thus reducing the power consumption by the NoC. If instead, the traffic priority is high, the router selects a higher clock frequency to send the packet according to the urgency it requires. If there is more than one traffic priority, the router sets its clock according to the highest priority one. If there is no traffic in the router, it is possible to gate all clocks and turn the idle router off. It returns to activity immediately if there are incoming packets asking for transmission.

By reducing clock frequency in each router that is idle or with low priority traffic, Hermes-GLP reduces the power consumption of the clock signal at these routers and globally in the NoC.

### **2.3 ATLAS**

ATLAS is an open source tool designed by the GAPH research group. It automates various processes related to the design flow for NoCs proposed by the same group. NoC Generation, synthetic Traffic Generation, NoC Simulation, Traffic Evaluation and Power Evaluation compose the basic current design flow.

In the NoC generation step, it is possible to configure the parameters of the NoC that to create, such as channel bandwidth, buffers depth, number of virtual channels and flow control strategies. After defining the necessary parameters, the user can ask the software to generate all the hardware modules that compose the NoC and appropriate testbench files for simulation. Modules employ VHDL code, and serve as input to classic FPGA synthesis tools. In addition to basic testbenches, the user may generate optional SystemC files that correspond to the traffic injection modules associated to each IP core.

The traffic generation step produces traffic files that simulate the behavior of the processing modules connected to the NoC, injecting synthetic traffic into the NoC through the previously mentioned SystemC modules during simulation. Traffic configuration evolves setting the frequency of packet injection, the target for each IP core, the number of packets to be transmitted, the size of each packet and a probability distribution model, which guides the injection of traffic in the NoC. It is possible to configure a separated traffic for each IP core, with very different parameters. After the definition of a traffic scenery, traffic files are generated for each IP and contain the information needed to reproduce the defined scenery and the traffic data that will be transmitted. The user may define as many traffic sceneries as needed, and choose one of these for simulation in the next step.

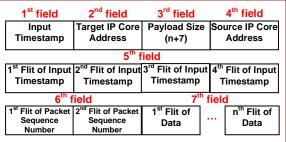

The simulation files generated by ATLAS to each IP are just a set of lines describing packets to inject in the NoC, with the format displayed in Figure 2.1. Each flit contains the number of bits set by the user in the NoC generation step. The first field contains the ideal timestamp value for injecting the packet into the NoC. The second field contains the target IP that will receive the current packet. The third field contains the payload size set by the user subtracted by six flits. The reason for this is explained later. The fourth field contains the source IP that will send the packet. The fifth field, composed by four flits, is the packet generation instant, and corresponds to the time the packet should be first inserted into the NoC (it is a repetition of the first field). ATLAS calculates it according to the probability distribution chosen by the user. The sixth field contains the packet sequence number that is the order in which the packet will be inserted into the NoC considering all the packets generated for all routers in the current scenery. This sixth field comprises two flits. The rest of the packet flits are the actual data flits and do not have a fixed number. The data information is synthetic and ATLAS generates it randomly. In addition, data is present only if it is expected to be transmitted, otherwise they do not exist. Therefore, the first six fields form the minimum amount of information sent that composes an ATLAS packet. The reason the third field is subtracted by six flits is the fact that the time the packet should be inserted into the NoC can be different of the time it is actually inserted. These values differ because the local router can be busy with other traffic in the moment the new packet should enter it. Therefore, the time information in the fifth field is not the one used by the target IP to calculate latency values. To be possible to calculate the latency at the target IP, the exact injection moment information must travel within the packet. To send the right insertion time, the simulation/emulation process produces this information and injects it in the packet dynamically. As the payload size is used to count the number of flits to be read from the memory and inserted into the NoC, it should not count reading these values from memory. Instead, these two will be inserted in the packet during simulation.

### Traffic description file format in Atlas

Figure 2.1 – General structure for describing traffic in ATLAS traffic files.

The next step implies NoC simulation. It runs an external simulator (today it supports Mentor Graphics Modelsim natively) associated with ATLAS, performs the simulation and generates the simulation output files.

The last step provides the analysis of the simulation results. The traffic evaluation mode facilitates the visualization of the results by presenting different type of graphs, tables and textual accounts.

Power Evaluation is only applicable to the Hermes NoC so far, and is omitted here.

## 2.4 Analysis by Emulation

Digital systems analysis procedures can be divided into two groups: abstract and concrete analysis. In abstract analysis, the techniques are based on manual or computational manipulation of abstract models of the system to be analyzed. The physical implementation is not required. Concrete analysis, on the other hand, is based on manual or computational manipulation of concrete implementations of the system to be analyzed. The physical implementation is necessary.

The complexity to analize NoCs by abstract simulation is increasing with the complexity of these.

When the routers become more complex, more signals need to be analyzed by the simulation software. In addition, the increasing speeds traffic drives in a NoC make the task of analyzing a significant period of it really time consuming. Simulation software needs to deal with too much signals and data and can waste much time to do it.

Simulation by emulation, on the other hand, is one subtype of concrete analysis and can exercise NoCs at actual hardware speeds, once it uses the physical implementations of the NoC under test. Emulation is a process similar to prototyping, but with a physic connection between the host and the prototype through a subsystem denominated *emulator*. Emulators are composed of specific hardware and software to substitute one or more components in the system's prototype [CAL98].

Fast, cycle-accurate FPGA emulators have been used as an alternative to software simulators, as they reduce validation time without compromising accuracy. FPGA emulators allows the user to exploit the parallel nature of hardware, thereby enabling easier detection of design and architectural problems early and reducing the number of chip respins [LOT11].

## 2.5 The Original HardNoC Platform

The HardNoC system is a hardware platform to exercise with NoCs in general, first developed for the Hermes-2VC NoC [MEL05]. Both, the HardNoC and the Hermes-2VC NoC were developed and implemented by the GAPH research group at PUCRS. This Chapter describes the platform's hardware in detail and its use.

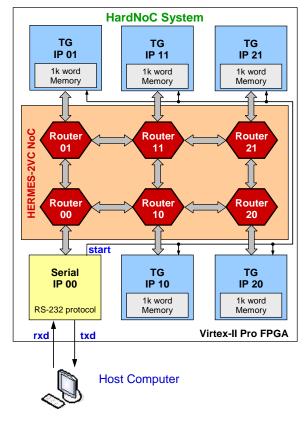

#### 2.5.1 The HardNoC Block Diagram

The first version of the HardNoC hardware comprised six IP cores connected to a 6-router Hermes-2VC NoC, as illustrated in Figure 2.2. The circuit was originally designed to run in a Xilinx University Program Virtex-II Pro Development System (XUP-V2PRO) with a Xilinx Virtex-II Pro XC2VP30 FPGA. The platform can easily be adapted to other boards and instances of HardNoC with more routers and IP Cores. The HardNoC instance depicted in Figure 2.2 includes five traffic generators (TG) IPs, each implemented with two 16 Kbits Block RAMs, resulting in a memory capacity of 1024 32-bit words at each TG. Also, there is one RS-232 serial IP that provides bi-directional communication with a host processor. The external interface of the HardNoC system is very simple, and comprises four signals:

- reset, responsible to initialize the HardNoC system;

- clock, the basic synchronization signal;

- rxd, serial data, coming from the host computer to the HardNoC system;

- txd, serial data going from the HardNoC system to the host computer.

#### 2.5.2 The HardNoC Packet Formats

Packet formats define a set of services offered by the host and communication network to all IP Cores in the system. The packet formats differ depending on the layer transmission is done, if it is packets transmitted by the NoC or through serial IP. The link layer encompasses a protocol employed to transmit information among the NoC routers, while the network layer includes different protocols to transmit data end-to-end between IP Cores or between IPs and the host.

Figure 2.2 – The original HardNoC system block diagram.

## 2.5.3 Link Layer Packet Format

At the link layer, there is only one packet format, employed to transmit data within the NoC, between routers, as Figure 2.3 depicts. At this level, all the information needed for transmission is the target IP, the payload size and the payload data. Thus, the packet format at the link layer contains two control information in the first two flits, Target IP Core Address (destination address) and Payload Size.

| Link Layer (NoC) Packet Format |                     |              |  |              |  |  |  |  |

|--------------------------------|---------------------|--------------|--|--------------|--|--|--|--|

| 1st flit                       | 2nd flit            | 3rd flit     |  | (n+2)th flit |  |  |  |  |

| Target IP Core<br>Address      | Payload Size<br>(N) | Payload Data |  | Payload Data |  |  |  |  |

Figure 2.3 - The HardNoC link protocol layer and its packet format.

### 2.5.4 NoC Network Layer Packet Formats

At the network layer, it is necessary to keep information about the source IP and the action to take with the transmitted packet. Thus, packets between TGs need more control fields. See Figure 2.4.

| 1 <sup>st</sup> flit | 2 <sup>nd</sup> flit                                                                                  | 3 <sup>rd</sup> flit                                                                                                                                                                                    | 4 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                        | 5 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9 <sup>th</sup> flit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target IP Core       | Payload Size                                                                                          | Source IP Core                                                                                                                                                                                          | Command                                                                                                                                                                                                                                                                                                                                                                                     | Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address              | (3)                                                                                                   | Address                                                                                                                                                                                                 | (0)                                                                                                                                                                                                                                                                                                                                                                                         | (15 downto 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Target IP Core       | Payload Size                                                                                          | Source IP Core                                                                                                                                                                                          | Command                                                                                                                                                                                                                                                                                                                                                                                     | Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address              | (4)                                                                                                   | Address                                                                                                                                                                                                 | (1)                                                                                                                                                                                                                                                                                                                                                                                         | (15 downto 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (15 downto 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ·                    |                                                                                                       |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Target IP Core       | Payload Size                                                                                          | Source IP Core                                                                                                                                                                                          | Command                                                                                                                                                                                                                                                                                                                                                                                     | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address              | (3)                                                                                                   | Address                                                                                                                                                                                                 | (9)                                                                                                                                                                                                                                                                                                                                                                                         | (15 downto 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                    |                                                                                                       |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Target IP Core       | Payload Size                                                                                          | Source IP Core                                                                                                                                                                                          | Command                                                                                                                                                                                                                                                                                                                                                                                     | Insertion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Insertion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Insertion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Insertion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |