#### PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL SCHOOL OF TECHNOLOGY COMPUTER ENGINEERING UNDERGRADUATE PROGRAM

# ASCEND-TSMC180-NCL: A SIMPLE NCL CELL LIBRARY TO SUPPORT MANUFACTURABLE QDI DESIGNS

# GABRIEL MITTEREGGER SUSIN

Thesis submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fulfillment of the requirements for the degree of Bachelor in Computer Engineering.

Advisor: Prof. Dr. Ney Laert Vilar Calazans Co-Advisor: MsC. Marcos Luiggi Lemos Sartori

> Porto Alegre 2020

# REPLACE THIS PAGE WITH THE LIBRARY CATALOG PAGE

# REPLACE THIS PAGE WITH THE COMMITTEE FORMS

I dedicate this work to my family and to all my friends, specially to my grandparents without whom I could not achieve this.

"A man travels the world over in search of what he needs, and returns home to find it." (George Moore)

# ASCEND-TSMC180-NCL: UMA BIBLIOTECA SIMPLES DE CÉLULAS NCL PARA SUPORTE AO PROJETO DE CIRCUITOS QDI FABRICÁVEIS

#### RESUMO

Circuitos digitais modernos podem conter bilhões de transistores, executando tarefas de computação extremamente complexas. O projeto baseado em células auxilia o processo de desenvolver circuitos integrados específicos para uma aplicação dada. Esta técnica exige uma biblioteca de células de suporte para intermediar a tradução de descrições alto nível de hardware, e.g. em Verilog ou VHDL, em um leiaute de circuito integrado fabricável. Existem numerosas bibliotecas disponíveis para elaborar circuitos síncronos. Infelizmente, poucas bibliotecas dão suporte ao projeto não-síncrono, e praticamente nenhuma destas está comercialmente disponível. Circuitos digitais assíncronos podem ser desenvolvidos usando diversos estilos lógicos. Null Convention Logic é um estilo entre os mais mencionados na literatura, conhecido por sua robustez a variações que perpassam o processo de projeto de circuitos integrados. Este trabalho propõe e descreve o desenvolvimento da ASCEnD-TSMC180-NCL, uma biblioteca de células que dá suporte à fabricação de circuitos digitais assíncronos. Catorze tipos de células com diferentes funções lógicas foram desenvolvidas, cada uma disponível em um conjunto de diferentes dimensionamentos. Até onde o Autor pode verificar, ASCEnD-TSMC180-NCL é poderosa o suficiente para permitir o projeto de circuitos usando um estilo de projeto derivado da Null Convention Logic. Como um projeto completo de um circuito integrado fabricável requer células especiais (e.g. pinos de E/S, espaçadores, uma variedade de buffers e inversores, células de antena, etc.), há vantagens em tornar uma biblioteca de células assíncronas compatível com uma biblioteca comercial escolhida, que forneça o conjunto complementar de células para habilitar projetos fabricáveis. Emprega-se aqui a biblioteca SAGE-X do ARM para tal compatibilidade. Um somador pipeline de 32 bits serviu para validar a biblioteca ASCEnD-TSMC180-NCL. Este circuito atesta a correção da implementação da biblioteca ASCEnD-TSMC180-NCL, integrando-a a um conjunto de ferramentas comerciais, o que forma um fluxo completo para o projeto de circuitos integrados digitais baseados nela.

**Palavras-Chave:** Circuitos assíncronos, Projeto baseado em células, Null convention logic, NCL, Quasi-delay insensitive, QDI, Biblioteca de células, leiaute de células.

# ASCEND-TSMC180-NCL: A SIMPLE NCL CELL LIBRARY TO SUPPORT MANUFACTURABLE QDI DESIGNS

#### ABSTRACT

Modern digital circuits can encompass billions of transistors, and are able to execute immensely complex computation tasks. The design process of application specific integrated circuits this big benefits from using cell-based design techniques. Such techniques require the existence of a supporting library of component cells, which intermediates the translation of high level hardware descriptions in e.g. Verilog or VHDL into an integrated circuit manufacturable layout. There are currently numerous libraries available for the design of synchronous circuits. Unfortunately, few libraries support clockless design, and fewer, if any of these, are commercially available. Asynchronous digital circuits can be developed using one of several available logic templates. Null convention logic is one such template that is among the most mentioned in the literature, being known for its robustness to timing and other variations that plague the integrated circuit design process. This work proposes and describes the development of ASCEnD-TSMC180-NCL, a simple null convention logic cell library for supporting the manufacturing of asynchronous digital circuits. Fourteen cell types with different logic functions were developed, each available in a set of different drive strengths. As far as the Author could verify, ASCEnD-TSMC180-NCL is resourceful enough to allow the design of circuits using the spatially distributed dual-spacer null convention logic template, derived from the null convention logic template. However, since a complete integrated circuit design requires some special cells to be manufacturable (I/O cells, fillers, a large variety of buffers and inverters, antenna cells etc.), there are advantages in making an asynchronous cell library fully compatible with some selected commercial library, which can provide a complementary set of cells. In this work, the SAGE-X library from ARM was selected for compatibility. To validate the ASCEnD-TSMC180-NCL library, a pipelined adder circuit with eight 32-bit inputs was described and implemented. The design attests the correction of the ASCEnD-TSMC180-NCL library implementation, by integrating it with a set of commercial tools, thus forming a complete design flow for digital integrated circuits design based on this library.

**Keywords:** Asynchronous circuit, Cell-based design, Null convention logic, NCL, Quasi delay insensitive, QDI, Standard cell library, Cell layout.

# LIST OF FIGURES

| 2.1 | A classical asynchronous circuit organization and an instance of a hand-<br>shake control protocol [SF01].                                                                                                                                   | 16   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2 | An asynchronous data flow representation for a linear pipeline. The hand-<br>shake between every pair of stages is abstracted in this representation [SF01].<br>Note that control signals flow in both directions, requests flow in the same |      |

|     | sense as data, while acknowledgement signals flow in the reverse direction.                                                                                                                                                                  | 16   |

| 2.3 | Examples of the two basic types of asynchronous handshake protocols [Sar19]                                                                                                                                                                  | . 17 |

| 2.4 | The basic transition diagram for transmitting binary data in a QDI channel, where S stands for the spacer, adapted from [MBSC18]                                                                                                             | 18   |

| 2.5 | Symbols and example behavior for NCL gates [Sar19]                                                                                                                                                                                           | 19   |

| 4.1 | A simplified flow diagram representing the cell development process used in this work                                                                                                                                                        | 28   |

| 4.2 | Pre- and post-sizing descriptions for INCL2W2110F3x4 cell.                                                                                                                                                                                   | 30   |

| 4.3 | Astran output for cell INCL2W2110F3x4.                                                                                                                                                                                                       | 30   |

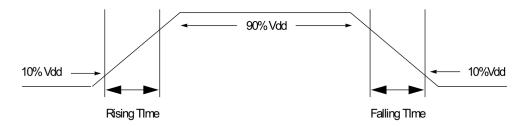

| 4.4 | Propagation delay at 50/50, adapted from [ARM08a]                                                                                                                                                                                            | 32   |

| 4.5 | Signal transition times definition, adapted from [ARM08a].                                                                                                                                                                                   | 32   |

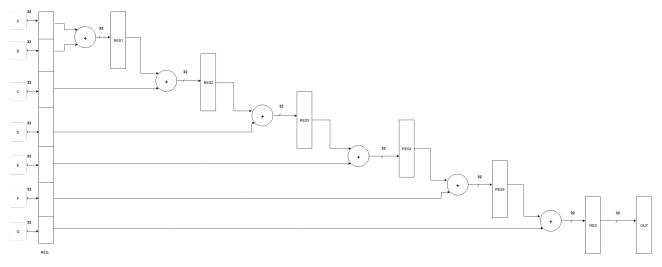

| 5.1 | The schematic of the pipeline adder                                                                                                                                                                                                          | 34   |

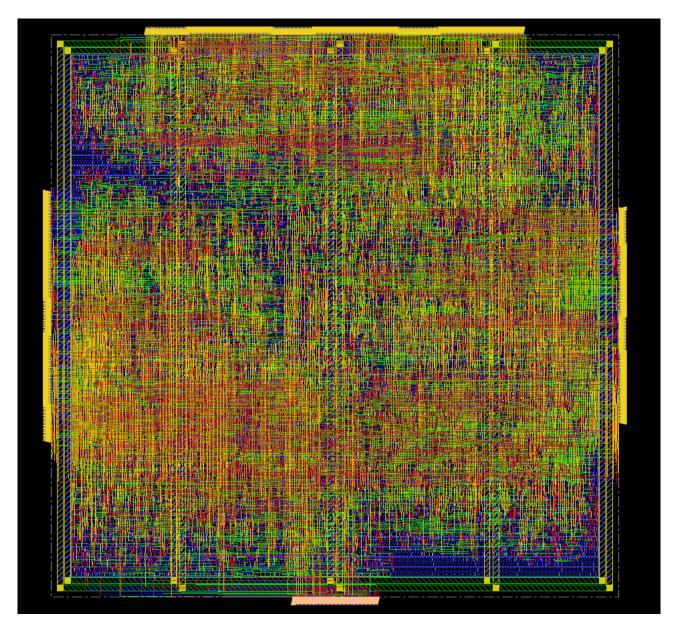

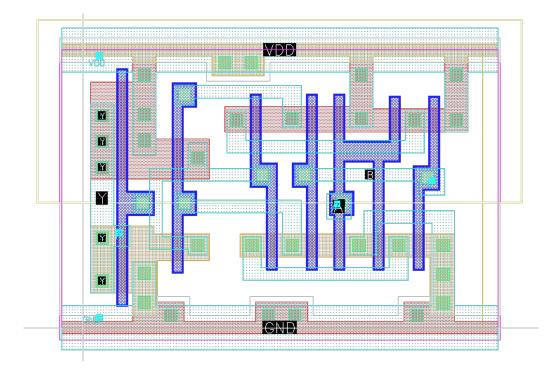

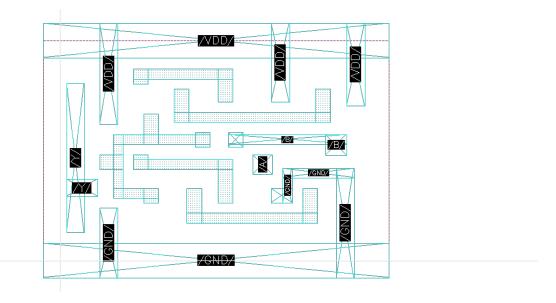

| 5.2 | The Innovus view of the developed circuit                                                                                                                                                                                                    | 39   |

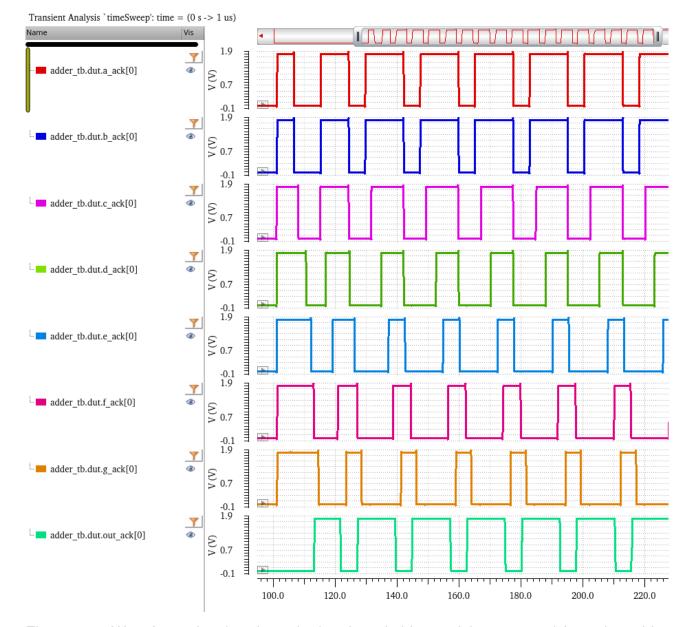

| 5.3 | Waveform showing the ack signals switching activity, captured from the adder analog simulation                                                                                                                                               | 40   |

# LIST OF TABLES

| The complete list of the 26 ASCEND-TSMC180-NCL cells. There are 14 cell classes and up to four drive strengths available.                                                                                                                            | 25                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| A list of the implemented 12 combinational cell classes, with their respective characteristic functions and virtual functions. A, B etc are cell inputs and Y is the cell output.                                                                    | 27                                                    |

| A list of the characterized corners in the library.                                                                                                                                                                                                  | 33                                                    |

| List of total gate instances used in the circuit and gate percentages by library.                                                                                                                                                                    | 35                                                    |

| List of instantiated gates used in the pipeline adder circuit. Includes details<br>on the number of instances of each cell and the total area taken by this cell.<br>The last column indicates the library from where the cell is taken              | 36                                                    |

| List of instantiated gates used in the pipeline adder circuit. Includes details<br>on the number of instances of each cell and the total area taken by this cell.<br>The last column indicates the library from where the cell is taken (continued). | 37                                                    |

| List of instantiated gates used in the pipeline adder circuit. Includes details<br>on the number of instances of each cell and the total area taken by this cell.<br>The last column indicates the library from where the cell is taken (continued). | 38                                                    |

|                                                                                                                                                                                                                                                      | cell classes and up to four drive strengths available |

# LIST OF ACRONYMS

- AMS Analog Mixed-Signal

- ARM Advanced RISC Machine

- BNF Backus-Naur Form

- CES Cell Specifier

- CMOS Complementary Metal Oxide Semiconductor

- DI Delay Insensitive

- DRC Design Rule Checker

- EDA Electronic Design Automation

- FPGA Field-Programmable Gate Array

- GAPH Hardware Development Support Group

- IC Integrated Circuits

- LEF Library Exchange Format

- LIB Liberty

- LVS Layout vs Schematic

- NCL Null Convention Logic

- NDA Non-Disclosure Agreement

- NMOS N Metal Oxide Semiconductor

- NRE Non-Recurring Engineering

- PEX Parasitic Extraction

- PMOS P Metal Oxide Semiconductor

- PVT Process, Voltage and Temperature

- QDI Quasi Delay Insensitive

- RISC Reduced Instruction Set Computer

- ROGEN Ring Oscillator Generator

- RTL Register Transfer Level

- SDDS-NCL Spatially Distributed Dual-Spacer Null Convention Logic

- SOC System-on-Chip

- SPICE Simulation Program with Integrated Circuit Emphasis

- TSMC Taiwan Semiconductor Manufacturing Company

- VF Virtual Function

- VHDL VHSIC Hardware Description Language

- VHSIC Very-High-Speed Integrated Circuit

# CONTENTS

| 1                                                                    |                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                        |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1.1                                                                  | MOTIVATION                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                        |

| 1.2                                                                  | OBJECTIVES                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                        |

| 1.3                                                                  | CONTRIBUTIONS                                                                                                                                                                                                                                                                                                                                                                                 | 14                                                        |

| 2                                                                    | BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                        |

| 2.1                                                                  | SOME ASYNCHRONOUS DESIGN PRINCIPLES AND TECHNIQUES                                                                                                                                                                                                                                                                                                                                            | 15                                                        |

| 2.1.1                                                                | HANDSHAKE COMMUNICATION                                                                                                                                                                                                                                                                                                                                                                       | 15                                                        |

| 2.1.2                                                                | QUASI DELAY INSENSITIVE (QDI) CIRCUITS                                                                                                                                                                                                                                                                                                                                                        | 17                                                        |

| 2.1.3                                                                | THE NULL CONVENTION LOGIC (NCL) DESIGN TECHNIQUE                                                                                                                                                                                                                                                                                                                                              | 18                                                        |

| 2.2                                                                  | STANDARD CELL-BASED DESIGN                                                                                                                                                                                                                                                                                                                                                                    | 18                                                        |

| 2.2.1                                                                | THE CELL PHYSICAL STRUCTURE - LAYOUT                                                                                                                                                                                                                                                                                                                                                          | 19                                                        |

| 2.2.2                                                                | CELL BEHAVIOR                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                        |

| 2.2.3                                                                | INTERFACE BETWEEN THE CELL AND ITS ENVIRONMENT                                                                                                                                                                                                                                                                                                                                                | 20                                                        |

| 2.2.4                                                                | THE CELL ELECTRICAL CHARACTERIZATION                                                                                                                                                                                                                                                                                                                                                          | 20                                                        |

| 2.3                                                                  | SPICE                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                        |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |

| 3                                                                    | RELATED WORKS                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                        |

|                                                                      | RELATED WORKS                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

| 3.1                                                                  |                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |

| <b>3</b><br>3.1<br>3.2<br>3.3                                        | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22                                                  |

| 3.1<br>3.2<br>3.3                                                    | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23                                            |

| 3.1<br>3.2<br>3.3                                                    | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23                                            |

| 3.1<br>3.2<br>3.3<br>3.4                                             | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23                                      |

| 3.1<br>3.2<br>3.3<br>3.4                                             | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23<br><b>24</b>                         |

| 3.1<br>3.2<br>3.3<br>3.4<br><b>4</b><br>4.1                          | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23<br><b>24</b><br>24                   |

| 3.1<br>3.2<br>3.3<br>3.4<br><b>4</b><br>4.1<br>4.2                   | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23<br><b>24</b><br>24<br>27             |

| 3.1<br>3.2<br>3.3<br>3.4<br><b>4</b><br>4.1<br>4.2<br>4.2.1          | THE SDDS-NCL QDI DESIGN TEMPLATE                                                                                                                                                                                                                                                                                                                                                              | 22<br>22<br>23<br>23<br><b>24</b><br>24<br>27<br>28       |

| 3.1<br>3.2<br>3.3<br>3.4<br><b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2 | THE SDDS-NCL QDI DESIGN TEMPLATE.<br>THE ASCEND CELL LIBRARY IMPLEMENTATION FLOW<br>A PROPOSAL OF DEVELOPMENT FOR A HIGH PERFORMANCE STAN-<br>DARD CELL LIBRARY.<br>A HIGH DENSITY STANDARD CELL LIBRARY<br>LIBRARY SPECIFICATION AND CELL DEVELOPMENT FLOW<br>THE ASCEND-TSMC180-NCL LIBRARY<br>ASCEND-TSMC180-NCL CELL DEVELOPMENT FLOW<br>CELL TRANSISTOR SIZING                           | 22<br>22<br>23<br>23<br><b>24</b><br>24<br>27<br>28<br>29 |

| 3.1<br>3.2<br>3.3<br>3.4<br><b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2 | THE SDDS-NCL QDI DESIGN TEMPLATE.<br>THE ASCEND CELL LIBRARY IMPLEMENTATION FLOW<br>A PROPOSAL OF DEVELOPMENT FOR A HIGH PERFORMANCE STAN-<br>DARD CELL LIBRARY.<br>A HIGH DENSITY STANDARD CELL LIBRARY<br>LIBRARY SPECIFICATION AND CELL DEVELOPMENT FLOW<br>THE ASCEND-TSMC180-NCL LIBRARY<br>ASCEND-TSMC180-NCL CELL DEVELOPMENT FLOW<br>CELL TRANSISTOR SIZING<br>LAYOUT PLACE AND ROUTE | 22<br>22<br>23<br>23<br>24<br>24<br>27<br>28<br>29<br>31  |

| REFERENCES                                                                                                                                                      | 42 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| APPENDIX A – Example Cell Layout                                                                                                                                | 44 |

| <b>APPENDIX B</b> – An ASCEnD-TSMC180-NCL Library Datasheet (Data correspond to characterization results for the nominal Supply, 1.8V, and temperature of 25°C) | 45 |

## 1. INTRODUCTION AND MOTIVATION

In the past decades asynchronous digital circuit design has been a research subject for some research groups and companies. The design complexity of these do not currently allow them to be employed in large-scale projects. Meanwhile, the electronic design automation (EDA) industry developed a large number of tools and techniques intended to support almost exclusively synchronous designs. Nonetheless, as technology geometries get smaller, problems like power consumption density and clock skew inside chips started to become increasingly difficult to cope with.

Asynchronous design begins to re-emerge as a solution to the aforementioned issues. This approach has the ability to relieve designers from using a clock, substituting it by local handshake protocols, which potentially solve problems caused by synchronous design in newer technologies. Handhsake communication protocols are covered in some detail in Section 2.1.1. The discussion herein states the Author's motivation to explore this area, brings the objectives of the work and reports its achieved contributions.

#### 1.1 Motivation

One of the biggest problems with asynchronous design of digital circuits is where to learn about it. There are several books and articles discussing asynchronous advantages and inconveniences, but the subject is convoluted for several reasons, some of which are depicted next. First, most undergraduate courses, if not all, tend to focus on synchronous design only, and rarely explore alternatives to this well-established design approach. Second, asynchronous design is not a single discipline. There is a large number of design techniques outside the synchronous domain, and it is very hard to deal with the large diversity of alternative approaches. Third, electronic design automation (EDA) tools tend to strongly focus on supporting synchronous design alone, leaving asynchronous design techniques unattended by automated tools support.

As Moreira points out in [Mor16] about the design of integrated circuits (ICs): "Contemporary IC design styles trade off time to market, non-recurring engineering (NRE) costs, production cost per part and performance, area and energy efficiency. These design styles are often classified into full-custom and semi-custom approaches. In the former, all the aspects of an IC are handcrafted and the application is literally manually designed, from functional to physical level. This means that every transistor is individually sized and laid out, involving detailed manipulation of physical and electrical characteristics of these devices." Examples of ICs designed using full-custom techniques are RAM and Flash memory and microprocessor chips, since the sales scale of such circuits justify the huge design effort they require.

Designing using a full custom flow is very complex. As the project gets bigger, difficulties grow very fast. Full custom designs are highly optimized in terms of transistor positioning and in area utilization, compared to schemes where transistors are pre-fabricated, like in gate arrays or field-programmable gate arrays (FPGAs). An intermediate alternative between full custom and the previously mentioned array-based approaches is to employ IC design schemes relying on the use of pre-defined cell libraries or generators, in what is called a *cell-based* design approach.

Semi-custom design approaches can be divided into cell-based and array-based ones. Array-based design uses pre-positioned and pre-fabricated transistors and/or other components/structures, which provide the opportunity for the designer to reduce or altogether avoid getting involved in the fabrication process, as when using FPGAs. This approach may penalize achievable performance and power. Array-based is not covered in this work.

Cell-based flows employ pre-designed logic cell libraries, known as *standard cells*, to develop ICs. As Moreira points out in [Mor16]: "Cells are designed at the layout level and implement basic logic functions, including combinational and sequential logic. Note that cells are organized in libraries, which can contain hundreds or thousands of them and the quality of a semi-custom design is a direct function of the quality of the library used to compose it." Each standard cell is designed, implemented and optimized individually. Optimization criteria encompass sizing and laying out cells for speed, power, resilience, security etc.

Cell-based design greatly reduces design complexity and design time. Implementing asynchronous circuits very often requires the use of specialized components, which are not available in typical commercial cell libraries. Nonetheless, there are few, if any, cell libraries available for those who intend to implement asynchronous circuits using a semicustom cell-based approach. The lack of commercially available standard cell libraries with dedicated cells for asynchronous design is an acute problem for both the research and commercial deployment of asynchronous techniques. This is accordingly the main motivation to this work.

#### 1.2 Objectives

This End of Term work targeted as main goal the development of an asynchronous standard cell library deemed for application in IC prototyping through fabrication services. To reach the established main goal, some objectives were established:

- The library to develop needed to contain enough cells to support implementing, with a reasonable degree of efficiency, a large spectrum of circuits describable as asynchronous circuits. This implies, for example enabling combination and sequential circuit design to be achievable. Support to some special functionalities were disregarded in this first implementation, though. For example, arbitration within asynchronous circuits may require components like *mutexes*, which will not be considered here for implementation as a cell.

- Full compatibility with some commercial standard cell library in the same fabrication technology is a requirement. This is what enables reducing the library implementation effort and yet supporting the complete design of manufacturable asynchronous ICs.

- The Author dominates the library design flow process at the end of the work.

- The library must be validated with the implementation of some real circuit, even if only to the point preceding the fabrication of some IC.

# 1.3 Contributions

Of course, the main contribution of this work is the development of the ASCEnD-TSMC180-NCL library, containing 26 cells designed from scratch. The library is fully compatible with the ARM SAGE-X library. Both libraries target the TSMC 180nm bulk CMOS technology.

As a second contribution of the work, the Author dominated every step of the cell and cell library design flow using multiple tools and design frameworks from Cadence and Mentor, two commercial providers of electronic design automation tools for the world semiconductor industry.

A third contribution is the availability of a design environment for using ASCEnD-TSMC180-NCL conjointly with the ARM SAGE-X library to develop asynchronous blocks and whole ICs. By applying these libraries to the development of a digital circuit, the Author demonstrates the compatibility between them.

# 2. BACKGROUND

This Chapter provides an introduction on some topics required to understand this work. Section 2.1 brings an overview on asynchronous circuit design, showing some of its aspects, like handshake protocols definition and operation, specific cell characteristics associated to some asynchronous design styles etc. Section 2.2 details some of the features of the standard cell-based design process, introducing the background about the cell creation process, from its starting informal logic description to a Spice file through layout generation and design rules verification, until reaching a fully characterized electrical structure for the desired cell.

### 2.1 Some Asynchronous Design Principles and Techniques

Asynchronous circuits do not rely on the use of a single, global and common time reference (as provided by a global clock signal). In synchronous circuits, all components share a discrete notion of time, as defined by the clock signal distributed throughout the device. Asynchronous circuits are different. As in synchronous circuits, they also employ binary signals that represent information using discrete functions, but time is not discretized. Also, information evolves among circuit modules using local handshake communication instead of all modules marching under the rule of the clock beat.

### 2.1.1 Handshake Communication

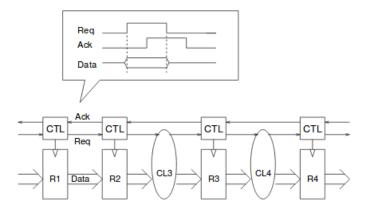

An asynchronous module has often the capacity to communicate with other modules regardless of the speed of its peers. Handshake protocols make this possible, using request and acknowledgment control signals to guarantee the data flow integrity. Figure 2.1 illustrates the general organization of a typical asynchronous pipeline [SF01], also showing an example waveform for a handshake data exchange.

Figure 2.1: A classical asynchronous circuit organization and an instance of a handshake control protocol [SF01].

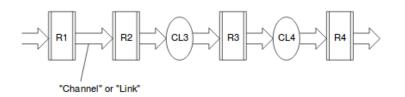

A handshake channel is where an asynchronous circuit keeps the distinct components synchronized, performing communication. Registers are only loaded where and when needed, and their timing operation is determined by actual circuit delays. A handshake protocol is characterized by two steps (assuming the transmitter initiates communication, which may not be always true): (i) A transmitter module produces a request for communication, announcing data availability; (ii) When ready, the receiver gets the data and acknowledges the request, allowing a new data transmission to take place. Figure 2.2 show a data flow for a linear asynchronous pipeline where handshake signals are abstracted.

Figure 2.2: An asynchronous data flow representation for a linear pipeline. The handshake between every pair of stages is abstracted in this representation [SF01]. Note that control signals flow in both directions, requests flow in the same sense as data, while acknowledgement signals flow in the reverse direction.

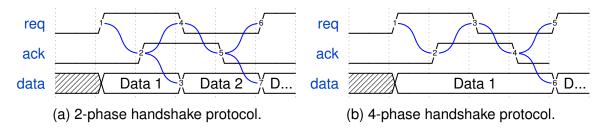

A 2-phase handshake protocol is one where the two steps mentioned above are implemented by single transitions in a control signal or in other equivalent way. Here, new data can be immediately sent after a request is acknowledged. A 4-phase handshake protocol is another protocol that is also commonly used, in which request and acknowledge signals need to be reset (return to their starting values) before new data can be made available and communicated. Figure 2.3 shows instances of a 2-phase and of a 4-phase protocol.

#### 2.1.2 Quasi Delay Insensitive (QDI) Circuits

Delay insensitive (DI) circuits are those where variations in the values of delays for any of its components (gates, registers etc.) and variations on the delay of any of its wires cannot modify the circuit behavior, i.e. the circuit behavior is absolutely insensitive to delays, provided only that all delays are finite. One of the techniques that facilitates the implementation of DI circuits is the use of DI codes for carrying information between the circuit components [Ver88]. Examples of DI codes are 1-hot, K-out-of-N and Berger codes [Ver88].

Unfortunately, it has been proved that the class of DI circuits is very limited [MD90], and few practical circuits can be implemented that display the DI circuit required properties. The least compromise that can be made to enable the design of circuits that are mostly robust to variations of delays in wires and components relies on the assumption that some wire forks in a circuit are identified as necessarily *isochronic*. This means that the propagation delay from the fork transmitter side to both receiving sides of the fork (or more sides, if the fork goes to more than two distinct places) are the same, or if they differ by some well-defined and *negligible* amount of time. Circuits that are DI except for this compromise are the class of the so-called quasi-delay insensitive (QDI) circuits.

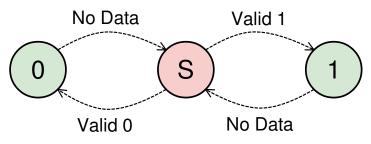

The handshake protocols and channels mentioned in Section 2.1.1 are essential in QDI circuits. In QDI circuits the use of DI codes allow embedding the request signal within the data representation itself. Another technique that improves the delay insensitivity of QDI circuits is, for example, to employ a 4-phase communication protocol coupled to the alternation of valid data and *spacers* in the circuit data wires (a spacer is a special invalid code in a DI scheme, say all wires at 0, to represent the absence of data). Figure 2.4 shows a basic transition diagram for transmitting data on a 1-bit QDI channel.

Figure 2.4: The basic transition diagram for transmitting binary data in a QDI channel, where S stands for the spacer, adapted from [MBSC18].

2.1.3 The Null Convention Logic (NCL) Design Technique

Null Convention Logic (NCL), originally proposed by Fant and Brandt [FB96, Fan05], is a semi custom QDI circuit design template that relies on the propagation of spacers during the reset phase of a 4-phase protocol. According to Moreira [Mor16], NCL design has been a subject of research for several groups worldwide and has been used to construct different circuits, especially for low power and small-to-medium sized applications. NCL circuits rely on the existence of special gates, called *threshold* gates or NCL gates. The output of an NCL gate is driven low when all inputs are low. The output is driven high when inputs meet the threshold conditions implied in the specific gate architecture. When the inputs do not fulfill the previous conditions, the gate output keeps its previous value.

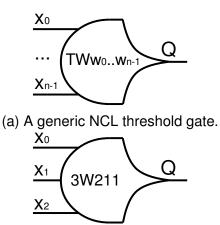

An NCL gate Boolean function expresses the threshold conditions, which often can be computed from a set o weights assigned to each input. Figure 2.5a shows a generic NCL gate, where n is the number of gate inputs, T is the threshold of the gate and each input  $x_i$  has a weight  $w_i$ .

The gate name reflects its threshold value. For example, a classical 2-input Muller C-Element is equivalent to a 2-input, threshold 2 NCL gate with weight 1 in all inputs. In the convention adopted here, this example gate receives the NCL name 2W211.

Figure 2.5b shows the 3-input gate 3W211, a 3-input, threshold 3 NCL gate with weight 2, 1 and 1 for the inputs (the convention is to assign weights from the upper inputs to the lower ones, in the order specified in the gate name). Figure 2.5c shows the truth table for this gate.

## 2.2 Standard Cell-Based Design

Cell-based design uses pre-characterized cell libraries, known as standard cell libraries, to develop IC modules or entire projects. This kind of design relies on a typically technology independent specification of the circuit (say in VHDL or Verilog), a selected technology and one or more cell libraries developed for that technology.

(b) The 3W211 NCL gate.

Figure 2.5: Symbols and example behavior for NCL gates [Sar19].

A standard cell library assumes that cells share a basic set of characteristics, often including: (i) A same height for all cells, to allow easy combination of cells in rectangular rows in the final circuit layout; (ii) Track placement - power and ground rails must be geometrically identical, follow a same orientation (usually horizontal), and be positioned at a same height relative to the cell origin. Also, wires passing over a cell frequently use pre-defined (horizontal and/or vertical) positions, called *tracks*. It is not unusual identify a cell library by the number of separated horizontal metal lines that can pass over the cell. Common examples are 7-track libraries, or 9-track libraries.

To employ a cell library, information must be made available on each cell. This information is organized in views that bring data about: (i) The cell physical structure or layout; (ii) The cell behavior; (iii) The interfaces between the cell and the circuit environment where it is to be used; (iv) The cell electrical characteristics (propagation delay, output delay, power consumption etc.).

### 2.2.1 The Cell Physical Structure - Layout

The physical structure of a cell is also called its *layout*. A layout is basically a set of rectangles drawn in a given set of technology layers<sup>1</sup>. The cell design must obey a set of rules among rectangles of a same and/or of distinct layers. A process called Design Rule Checking (DRC) verifies if a cell or an entire IC design respects all predefined rules.

DRC is a physical verification process to determine if a cell/IC layout is correct, under the point view of minimal conditions that ensure manufacturability. Each semiconductor process has its own set of rules and defines sufficient margins such that normal variability

| $X_0$ | $X_1$ | $X_2$ | $Q_t$     |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0         |

| 0     | 0     | 1     | $Q_{t-1}$ |

| 0     | 1     | 0     | $Q_{t-1}$ |

| 0     | 1     | 1     | $Q_{t-1}$ |

| 1     | 0     | 0     | $Q_{t-1}$ |

| 1     | 0     | 1     | 1         |

| 1     | 1     | 0     | 1         |

| 1     | 1     | 1     | 1         |

<sup>&</sup>lt;sup>1</sup>Each *layer* corresponds to a given material or physicochemical step used in the IC fabrication process.

in the manufacturing process does not result in IC failure. A rule can be as simple as the minimum width of a wire or the distance between two wires.

The layout view contains information about transistor positions, with their width and height, according to the technology. Metal level interconnections create the desired logic.

#### 2.2.2 Cell Behavior

A cell is designed to work with a pre-defined behavior, usually described in Verilog, a hardware description language. This behavior is combined with that of other cells by automated synthesis processes to produce operational circuits. A cell implements at least a basic function, such as input inversion, or computing Boolean functions such as OR, NOR, AND, NAND, XNOR or XOR. Furthermore, libraries can also contain more complex logic functions, like single or multi-bit adders, multiplexers, flip-flops, encoders, AND-OR-Invert cells, etc.

### 2.2.3 Interface Between the Cell and its Environment

Libraries gather the so-called abstract views of cells, using a standard format for this, the *Library Exchange Format* (or LEF). The cell abstract view provides information about cell inputs and outputs (pin position, pin size, etc.), routing metals blockages and area usage. Thus, LEF views are in fact an abstraction of the cell layout. They are employed, for example, in the cell placement phase of the physical circuit design process and in the routing phase, for interconnecting cells.

### 2.2.4 The Cell Electrical Characterization

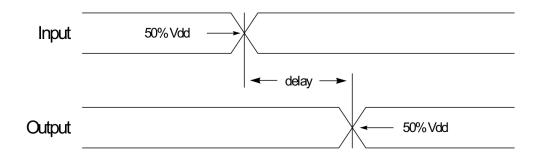

The cell electrical characterization is usually stored in files that employ the *Liberty* (or LIB) standard format. LIB files define characterization parameters, such as the name of the power rails. They also contain information about power consumption, input and output pins, logic function, input and output capacitances and propagation time of input transitions to output transitions. This information is used for computing, reporting and validating the operation of the design that employs the cell.

### 2.3 Spice

Spice is a description language useful to model circuits by means of the interconnection of electronic components such as transistors, capacitors, diodes etc. Spice allows the development of circuit topologies at the electric level, being able to express component dimensions, connections and other characteristics, as well as defining input stimuli for exercising the circuit by simulation.

There are several Spice-compatible simulators available, which allow experimenting with circuit inputs (such as input slew rates), outputs (such as the capacitances of output nodes) and internal parameters, such as component dimensions. Spice simulation enables the design of highly optimized small to medium circuits (with typically less than a few thousands transistors).

## 3. RELATED WORKS

This Chapter introduces relevant works employed in the development of the work proposed here. The Chapter is divided into four sections, Section 3.1 focus on the specific QDI design template to support in this work; Section 3.2 gives the overall cell design process employed here; Section 3.3 presents a development of standard cell library focused in high performance circuits; Section 3.4 approaches the development of a high density standard cell library.

#### 3.1 The SDDS-NCL QDI Design Template

QDI circuits are a class of asynchronous circuits that perform computation on DIencoded information. A QDI design usually requires less restrictive timing assumptions than other classes of asynchronous design (e.g. bundled-data or speed independent ones). This makes QDI circuits less sensitive to process, voltage and temperature (PVT) variations and ageing.

The library cells developed in this work are destined for use in the design of QDI circuits, more specifically for design templates developed within the scope of the Author's research group. One of these is the SDDS-NCL design template, an enhancement of the NCL template proposed by Moreira [Mor16] and also used in Sartori's MsC dissertation [Sar19]. Sartori proposed a synthesis flow for QDI circuits called Pulsar, which uses commercial EDA tools along the circuit design process. This method allows designers to use worst-case performance metrics for implementing asynchronous circuit modules. Furthermore, Pulsar allows trading performance, power and area during the circuit optimization phases.

#### 3.2 The ASCEnD Cell Library Implementation Flow

The present work also relies on the cell library development flow described by Moreira in his PhD work [Mor16]. In that Thesis the author explores how to build libraries to support semi custom asynchronous design, improving commercial tools with aids to e.g. better sizing transistors and to characterize asynchronous components. Together with the proposition of a flow for asynchronous cell library design called ASCEnD, Moreira also brought about a fully automated flow for asynchronous circuit design. His techniques describe the optimization of asynchronous design, from design capture to the electric, cell and layout levels. Moreira shows that asynchronous design can be an efficient choice for both low-power and high-performance designs. Given these advantages, he proposes new way of implementing asynchronous design, exploring power, delay and area trade-offs. The Author also presents an exploration of the state of the art in related works in the area of asynchronous project development methods.

## 3.3 A Proposal of Development for a High Performance Standard Cell Library

The development of high performance standard cell library as proposed by Kotkar [Kot14], has as main objective to increase performance of logic cells satisfying a given specification. The work proposes the development of specific cell library at different drives strengths. The author mentions that designing every logic gate under several different specifications is a very time-consuming process. He points out the possibility of using this high performance cell library to design complex circuits. His techniques describe the benefit of a high performance cell library in highly computing-intensive IC designs, where density can be neglected to meet performance.

# 3.4 A High Density Standard Cell Library

Melinmani et al. describe the development of a high density standard cell library [MSM19]. The work relies on a traditional library design flow. The library is designed for the technology UMC 180nm CMOS. It is characterized on three corners. The library contains 103 high density, 9-track cell, each cell type presenting from 1 to 5 distinct drive strengths. The library provides layout, schematic, symbol and abstract views. The Author explores the beta ratio calculation, using F03 and calculating the delay in the middle of the chain, a method which according to the authors eliminates slew effects after the 4th or 5th circuit stage.

# 4. LIBRARY SPECIFICATION AND CELL DEVELOPMENT FLOW

This work presents the development of an NCL cell library to support the design of manufacturable asynchronous circuits that follow a specific QDI template, SDDS-NCL, as proposed by Moreira et al. [MTMC14, Mor16] and later enhanced by Sartori et al. [SWMC19, Sar19]. The library development follows the design flow described in [Mor16], with some differences, due to the evolution of individual techniques and tools composing the flow since its first proposal. The cells developed address the TSMC 180nm bulk CMOS technology. Access to use this technology is granted through the signing of a specific NDA between PUCRS and TSMC, through the EuroPractice service. The reason for choosing this technology is that the Author's research group has multiple opportunities to employ the latter to perform real IC prototyping, having already successfully designed and tested two operational systems-on-chip (SoCs) in it. To this technology is added the use of a specific library from a third-party vendor, to which the Author's research group has access. The developed library, called ASCEND-TSMC180-NCL, is fully compatible with the ARM SAGE-X library [ARM08a], henceforth called the *reference library*. Access to use the latter library is granted through the signing of a specific NDA between PUCRS and ARM. The compatibility allows a designer to mix gates from the reference library and the ASCEND-TSMC180-NCL library. This is important to enable the design of complete ICs.

The characteristics of the ASCEND-TSMC180-NCL library are the target of Section 4.1. Section 4.2 presents the library cell development flow.

## 4.1 The ASCEnD-TSMC180-NCL Library

The complete set of cells in the ASCEnD-TSMC180-NCL library is depicted in Table 4.1. These were developed using the flow described in Section 4.2. Each cell is implemented in one to four drive strengths, in accordance with the available drive strengths of the reference library (XL, X1, X2, X4). These cells, together with several cells from the ARM TSMC 180nm Process 1.8V Sage-X standard cell library [ARM08b] form a basic set to produce pseudo-synchronous [Sar19] SDDS-NCL circuits using the Pulsar flow [Sar19].

The composition of reference library cells and ASCEnD-TSMC180-NCL to produce complete SDDS-NCL circuit modules is as follows:

1. NCL relies on threshold gates, as briefly described in Section 2.1.3. However, an NCL gate with threshold 1 is an ordinary OR gate (present in several flavors in the reference library);

| Cell Class Name | Cell Type | Threshold | Input Weights | Inputs | Drive Strengths |

|-----------------|-----------|-----------|---------------|--------|-----------------|

| NCL2W110F2      | NCL       | 2         | 11            | 2      | XL/X1/X2/X4     |

| NCL3W111OF3     | NCL       | 3         | 111           | 3      | X4              |

| NCL2W211OF3     | NCL       | 2         | 211           | 3      | X4              |

| NCL3W211OF3     | NCL       | 3         | 211           | 3      | X4              |

| RNCL2W110F2     | RNCL      | 2         | 11            | 2+1    | X4              |

| SNCL2W110F2     | SNCL      | 2         | 11            | 2+1    | X4              |

| INCL2W110F2     | INCL      | 2         | 11            | 2      | XL/X1/X2/X4     |

| INCL3W1110F3    | INCL      | 3         | 111           | 3      | X4              |

| NCLP2W11OF2     | NCLP      | 2         | 11            | 2      | XL/X1/X2/X4     |

| NCLP3W111OF3    | NCLP      | 3         | 111           | 3      | X4              |

| NCLP2W211OF3    | NCLP      | 2         | 211           | 3      | X4              |

| NCLP3W211OF3    | NCLP      | 3         | 211           | 3      | X4              |

| INCLP2W11OF2    | INCLP     | 2         | 11            | 2      | XL/X1/X2/X4     |

| INCLP3W111OF3   | INCLP     | 3         | 111           | 3      | X4              |

Table 4.1: The complete list of the 26 ASCEND-TSMC180-NCL cells. There are 14 cell classes and up to four drive strengths available.

- SDDS-NCL uses three gate classes besides NCL: (i) NCL inverted counterparts (INCL), where threshold-1 gates are NOR gates; (ii) NCLP gates that follow the RTO protocol not RTZ as in NCL. Here,threshold-1 gates are AND gates; (iii) NCLP inverted counterparts (INCLP), where threshold-1 gates are NAND gates;

- As a consequence of the previous two items and of the chosen full compatibility of the involved libraries, ASCEnD-TSMC180-NCL need not contain any threshold-1 gates. Accordingly, all cells ASCEnD-TSMC180-NCL are sequential gates with some degree of hysteresis, functionality absent in commercial cell libraries;

- 4. It is often necessary, during digital circuit implementation, to generate storage devices that can be initialized. Thus, a minimum ensemble of gates with set or/and reset control is necessary in ASCEnD-TSMC180-NCL. Note that ordinary flops and latches from the reference library have no use in NCL or SDDS-NCL design.

Assuming the above information on how cells from the two libraries are composed or excluded from use, it is then possible to interpret the data in Table 4.1. Every specific instance of a cell has a name structured according to the following Backus-Naur Form (BNF): **[R|S][I]NCL[P]<T>W<ws>OF<ins>X<L|1|2|4>**. Here, elements between square brackets ([]) are optionally present, vertical bars (|) represent choices and elements between angle brackets (<>>) are mandatory in the name, while letters outside all mentioned brackets are mandatory and present as themselves in the name. The latter correspond to type designators and/or field separators. **<T>** is a number representing the threshold of the gate, **<ws>** is the set of natural number weights, one for each gate input, **<ins>** is the number of inputs of the gate, and the field after the **X** letter represents the cell instance drive strength. For example, the cell classes NCL2W110F2 and NCL3W1110F3 are respectively 2- and 3-input

C-Elements (conventional RTZ gates). This notation extends the generic NCL gate naming presented in Section 2.1.3.

One feature of the library is that some cells have the property that their functional behavior can be interpreted in different forms by naming their pins differently. This feature enables that some cell pairs share a same layout. Analysis conducted here showed that the 26 cells in the ASCEnD-TSMC180-NCL library only require 14 distinct cell layouts. For example, cells NCLP2W211OF3 and NCL2W211OF3 can be used as a settable and as a resetable C-element, respectively. The latter interpretations allow them to be employed as components of registers. In addition, to use these cells in an SDDS-NCL design environment, it is necessary to develop cells in complementary pairs, as explained in detail, e.g. in [MTMC14]. Such pairs are determined through the concept of *virtual functions* [MTMC14].

Besides the functional characteristics, cells can be differentiated by their *strength*, the relative capacity of a cell to drive its output, using *Xi*. The bigger the value of *i*, the stronger the cell. An *X*1 cell can drive a certain output capacitance with a certain delay. However, an *X*4 cell can drive a 4 times larger capacitance with the same delay as cell *X*1. The *XL* designator corresponds to a drive with nominally half the drive strength of *X*1, *L* standing for *low drive strength*. In this work, cell output buffers are sized to agree with the drive strength definition defined in the reference library (ARM TSMC 180nm Process 1.8V Sage-X standard cell library [ARM08b]).

Table 4.2 describes the functionality for each of the 12 cell classes that are used to build combinational circuits (all cells, except those with set or reset pins). Functionality is described in terms of the cell sequential behavior (using its characteristic function) and by means of the cell virtual function (used by commercial synthesis tools to manipulate the cell). Note that an NCL gate virtual function is a function that produces 1 for every input combination (and only for these) that makes the NCL gate producing 1. Similar but not identical observations hold for INCL, NCLP and INCLP gates, see [Sar19] for more on this. More formally, a virtual function or *vfunction* is a Boolean function associated with the NCL, NCLP, INCL or INCLP gates, which represents its support gate. Vfunctions *f* are defined as follows [SWMC19]:

- if the support gate of *f* is an NCL gate A, the ON-set of *f* is the same as the ON-set of A. The OFF-set of *f* comprises all other n-input patterns;

- 2. if the support gate of *f* is an NCLP gate B, the OFF-set of *f* is the same as the OFF-set of B. The ON-set of *f* comprises all other n-input patterns;

- 3. if the support gate of *f* is an INCL gate C, the OFF-set of *f* is the same as the OFF-set of C. The ON-set of *f* comprises all other n-input patterns;

- 4. if the support gate of *f* is an INCLP gate D, the ON-set of *f* is the same as the ON-set of D. The OFF-set of *f* comprises all other n-input patterns.

If the support gate of *f* is of type NCL or NCLP, f is a positive vfunction. Otherwise, *f* is a negative vfunction.

Table 4.2: A list of the implemented 12 combinational cell classes, with their respective characteristic functions and virtual functions. A, B etc are cell inputs and Y is the cell output.

| Gate Name     | Characteristic Function           | Virtual Function                    |

|---------------|-----------------------------------|-------------------------------------|

| NCL2W110F2    | (A * B) + Y * (A + B)             | A * B                               |

| NCL3W111OF3   | (A * B * C) + Y * (A + B + C)     | A * B * C                           |

| NCL2W211OF3   | B * C + Y * (B + C) + A           | A + B * C                           |

| NCL3W211OF3   | A * (B + C) + Y * (A + B + C)     | A * (B + C)                         |

| INCL2W11OF2   | !((A * B) + !Y * (A + B))         | !( <i>A</i> * <i>B</i> )            |

| INCL3W111OF3  | !((A * B * C) + !Y * (A + B + C)) | !( <i>A</i> * <i>B</i> * <i>C</i> ) |

| NCLP2W11OF2   | (A * B) + Y * (A + B)             | A + B                               |

| NCLP3W111OF3  | (A * B * C) + Y * (A + B + C)     | A + B + C                           |

| NCLP2W211OF3  | (B * C + Y * (B + C)) * A         | A * (B + C)                         |

| NCLP3W211OF3  | A * B * C + Y * (A + B * C)       | A + B * C                           |

| INCLP2W11OF2  | !((A * B) + !Y * (A + B))         | !( <i>A</i> + <i>B</i> )            |

| INCLP3W111OF3 | !((A * B * C) + !Y * (A + B + C)) | !(A+B+C)                            |

An observation regarding the cell composition of library ASCEnD-TSMC180-NCL is that all possible threshold functions depending on up to three inputs can be produced with just one library gate, with a single exception, the NCL2W111OF3 gate [Fan05]. No version of this gate could be developed in the time available to complete this work. Its implementation is a recommended future work, to make the library functionally complete for functions with up to three inputs. Also, an attentive reader will note in Table 4.1 that the current state of ASCEnD-TSMC180-NCL could benefit from a larger diversity of drive strengths for many of the cells, which is another useful future work. Several publications on NCL mention the availability of functions with up to four inputs [Fan05]. Although not necessary to implement circuits in general, expanding library ASCEnD-TSMC180-NCL to contain 4-input cells could be useful to enable more flexibility during circuit synthesis. Note however that 4-input functions can be cumbersome. For ultra low power circuits operating under deep voltage scaling (e.g. in near- and sub-threshold regimes) 4-input functions are typically not used.

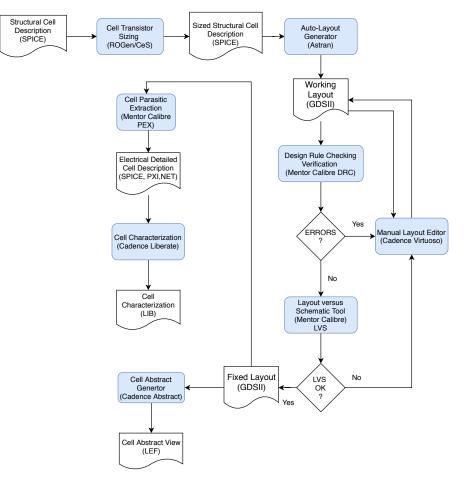

#### 4.2 ASCEnD-TSMC180-NCL Cell Development Flow

Developing a cell from scratch is an activity contemplating multiple steps, some of which imply iterative refinements. Linearizing these steps, it is possible to divide tasks associated with cell development into eight steps: (i) functionality design; (ii) schematic view capture; (iii) transistor sizing; (iv) layout view generation; (v) layout verification; (vi) layout extraction; (vii) characterization view; (viii) abstract view generation. The four steps with the word "view" in their names (ii, iv, vii and viii) produce each a part of the cell description that together form the complete information set about that cell in the library. The distinct views are used along IC development by several design and verification tools.

Figure 4.1 details the cell development flow, which operation is discussed in the next three sections.

Figure 4.1: A simplified flow diagram representing the cell development process used in this work.

### 4.2.1 Cell Transistor Sizing

As mentioned before, a library may contain multiple driving strengths, which indicate the relative capability of a gate to drive an output load. At the layout level, different drive strengths are obtained by transistor *folding* or *fingering*. For example, "X4" indicates four folds. The reference library also provides a half-fold configuration identified by the suffix "XL".

For each cell, the driving strength defines how to dimension the cell output buffer. These are often inverters dimensioned according to inverters of corresponding driving strength from the reference library. Figure 4.2a depicts a cell schematic with an output buffer for a "X4" driving strength cell.

Transistor sizing in this work relies on the use of the ROGen/CeS in-house tools. ROGen/CeS execution is parameterized by an input configuration file. This file is prepared based on the technology under use, on the library compatibility issues and on the definition of ranges for the variable amounts employed by the programs. Given that a previous effort by the GAPH group already generated such a configuration file for the TSMC 180nm technology, when proposing the ASCEnD-TSMC180-Velo library [Gua17], this work chose to employ this configuration as is, after careful consideration of its contents. The starting point for sizing cell transistors is a Spice schematic derived from the behavioral specification of the cell. In this schematic the width of output, state-holding and feedback transistors are fixed to pre-determined values and the transistors taking part on the set and reset logic of the gate are subject of transistor sizing. This is a simplification of the transistor sizing process, employed by the ROGen tool. The parametric variable pparam is assigned to the width of PMOS transistors subject to sizing. Similarly, the parametric variable nparam is assigned to the width of NMOS transistors subject to sizing. The length for all cell transistors is kept fixed at the minimum value, another simplification adopted by ROGen. ROGen and CeS are in-house software tools of the GAPH group, used to perform the transistor sizing process and to help the user to pick the best size options. ROGen generates Spice simulation decks where each instance of a sized cell is arranged in a ring oscillator. This simulation deck is used to explore a range for sizing parameters pparam and nparam. The ring oscillator is simulated for each combination of values for sizing parameters. Power and timing results are then collected from simulations. Next, CeS analyses the power and timing results and selects the best sizing parameters, according to a user-defined cost function. The output of CeS is a Spice schematic with all transistors sized. An example output of CeS is depicted in Figure 4.2b.

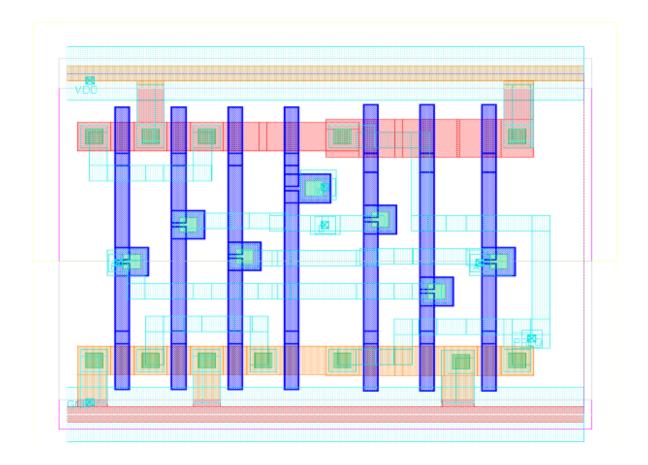

#### 4.2.2 Layout Place and Route

The layout is generated from the new schematic with Astran [ZRM<sup>+</sup>14], once the sizing is completed. An example layout produced by Astran is depicted in Figure 4.3. This generated layout does not always respect the target technology abutment and design rules. This occurs because Astran offers little flexibility to parameterize its layout generation process.

However, it is possible to manually correct the layout generated by Astran. Layout correction follows a loop where design rules are checked using the Calibre DRC tool and if rules are violated the layout is manually fixed with the Cadence Virtuoso layout editor. The loop goes on until no design rule violations are left.

When no further violations are found by the DRC tool, the equivalence between the layout and the schematic is checked. The Layout versus Schematic (LVS) tool [Men19],

| .SUBCKT INCL2W2110F3X4 A B C QN GND VDD                  |

|----------------------------------------------------------|

| *.pininfo A:I B:I C:I QN:O GND:G VDD:P                   |

| *SET/RESET logic                                         |

| MPS00 VDD  A pl00 VDD pch W=pparam L=0.18u               |

| MPS01 pl00 B pl01 VDD pch W=pparam L=0.18u               |

| MPS02 pl01 C PREQ VDD pch W=pparam L= <mark>0.18u</mark> |

| MNS01 PREQ C nl01 GND nch W=nparam L=0.18u               |

| MNS02 nl01 B GND  GND nch W=nparam L=0.18u               |

| MNS03 PREQ A GND GND nch W=nparam L=0.18u                |

| *FeedbacK INV + HOLD1/HOLD1                              |

| MPF00 FBP IQ PREQ VDD pch W=0.42u L=0.18u                |

| MPF01 FBP A FBP0 VDD $pch W=0.42u L=0.18u$               |

| MPF02 VDD B FBP VDD pch W=0.42u L=0.18u                  |

| MPF03 VDD C FBP VDD pch W=0.42u L=0.18u                  |

| MNF00 FBN IQ PREQ GND nch W=0.42u L=0.18u                |

| MNF01 FBN A GND GND nch W=0.42u L=0.18u                  |

| MNF02 FBN B GND GND nch W=0.42u L=0.18u                  |

| MNF03 FBN C GND GND nch W=0.42u L=0.18u                  |

| *Output BUFF                                             |

| MPI00 VDD PREQ IQ VDD pch W=1.44u L=0.18u                |

| MPI01 VDD IQ QN VDD pch W=3.52u L=0.18u                  |

| MNI00 GND PREQ IQ GND nch W=0.96u L=0.18u                |

| MNI01 GND IQ QN GND nch W=2.4u L=0.18u                   |

| *Transistors count: NMOS 8 PMOS 8 TOTAL 16               |

| *.SCALE meter                                            |

| *.ROGen:THR 2                                            |

| *.ROGen:IN 3                                             |

| *.ROGen:DRV X4                                           |

| *.ROGen:PIN in in in out gnd vdd                         |

| *.ROGen:PTC RTZ                                          |

| *.ROGen:INV 1                                            |

| *.ROGen:CONF NONE                                        |

| *.ROGen:RST 0                                            |

| *.ROGen:SET 1                                            |

| . ENDS                                                   |

| .SUBCKT INCL2W2110F3X4 A B C QN GND VDD                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *.pininfo A:I B:I C:I QN:O GND:G VDD:P                                                                                                                                                             |

| *SET/RESET logic                                                                                                                                                                                   |

| MPS00 VDD A pl00 VDD pch W=0.56u nf=1 L=0.18u                                                                                                                                                      |

| MPS01 pl00 B pl01 VDD pch W=0.56u nf=1 L=0.18u                                                                                                                                                     |

| MPS02 pl01 C PREQ VDD pch W=0.56u nf=1 L=0.18u                                                                                                                                                     |

| MNS01 PREQ C nl01 GND nch W=0.44u nf=1 L=0.18u                                                                                                                                                     |

| MPS01 p100 b p101 vb pch w=0.300 mf=1 L=0.300<br>MPS02 p101 C PREQ VDD pch W=0.560 mf=1 L=0.300<br>MNS01 PREQ C n101 GND nch W=0.440 nf=1 L=0.300<br>MNS02 n101 B GND GND nch W=0.440 nf=1 L=0.300 |

| MNS03 PREO A GND GND nch W=0.44u nf=1 L=0.18u                                                                                                                                                      |

| *FeedbacK INV + HOLD1/HOLD1                                                                                                                                                                        |

| MPF00 FBP0 IQ PREQ VDD pch W=0.42u L=0.18u                                                                                                                                                         |

| MPF01 FBP A FBP0 VDD pch W=0.42u L=0.18u                                                                                                                                                           |

| MPF02 VDD B FBP VDD pch W=0.42u L=0.18u                                                                                                                                                            |

| MPF03 VDD C FBP VDD pch W=0.42u L=0.18u                                                                                                                                                            |

| MNF00 FBN IQ PREQ GND nch W=0.42u L=0.18u                                                                                                                                                          |

| MNF01 FBN A GND GND nch W=0.42u L=0.18u                                                                                                                                                            |

| MNF02 FBN B GND GND nch W=0.42u L=0.18u                                                                                                                                                            |

| MNF03 FBN C GND GND nch W=0.42u L=0.18u                                                                                                                                                            |

| *Output BUFF                                                                                                                                                                                       |

| MPI00 VDD PREQ IQ VDD pch W=1.44u L=0.18u                                                                                                                                                          |

| MPI01 VDD IQ QN VDD pch W=3.52u L=0.18u                                                                                                                                                            |

| MPI01 VDD IQ QN VDD pch W=3.52U L=0.18U<br>MNI00 GND PREQ IQ GND nch W=0.96U L=0.18U                                                                                                               |

| MNIOI GND IQ QN GND NCH W=2.40 L=0.180                                                                                                                                                             |

| *Transistors count: NMOS 8 PMOS 8 TOTAL 16                                                                                                                                                         |

| *.SCALE meter                                                                                                                                                                                      |

| *.ROGen:THR 2                                                                                                                                                                                      |

| *.ROGen:IN 3                                                                                                                                                                                       |