## Organização e Arquitetura de Computadores

#### Memória Cache: Mapeamento Associativo

Alexandre Amory Edson Moreno

#### Na Aula Anterior

- Cache com mapeamento direto

- Um bloco só pode assumir uma linha da cache

- Hardware simples

- Posicionamento dos blocos de memória não é flexível

- Mesmo que eu tenha linhas disponíveis na cache (bit de validade='0') ainda sim é possível ocorre cache miss.

- Existem outras maneiras mais flexíveis de posicionar blocos de memória

- Mapeamento associativo

### Introdução

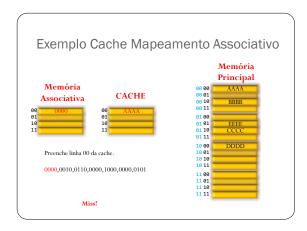

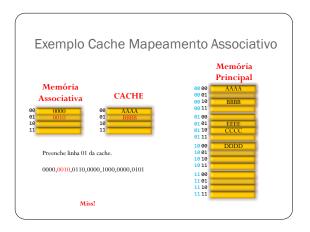

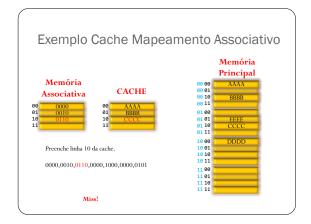

- Endereço da MP em qualquer posição da cache

- Tag não fica mais na cache e sim em memória especial (memória associativa)

- Pode ter bit de validade ou usar tag com valor inválido para determinar se posição tem uma informação válida

- Consequências

- Necessita fazer procura de dado

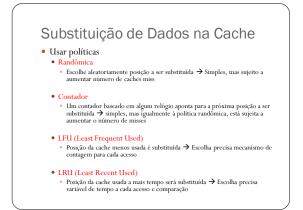

- Necessita política de substituição

- Quando ocorre miss

- Solução para procurar

- Procurar em paralelo

- Usar memória associativa

- Memória cara e de tamanho limitado

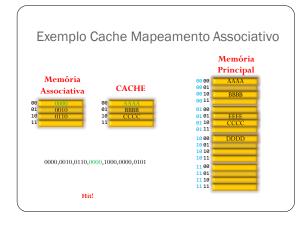

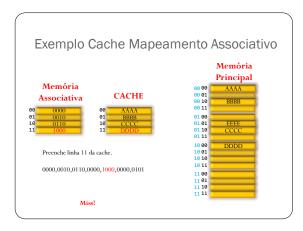

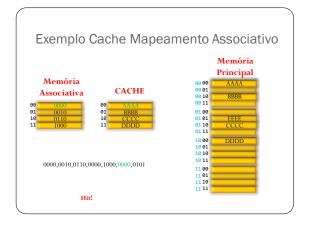

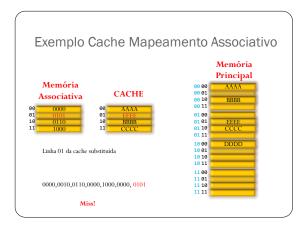

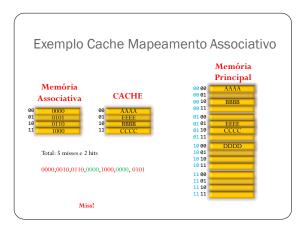

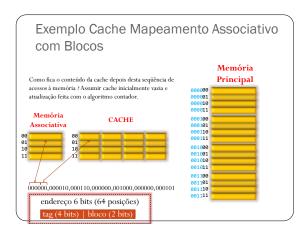

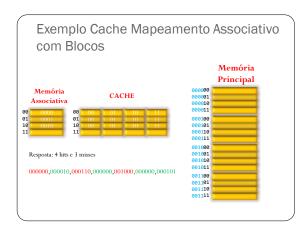

### Mapeamento Associativo

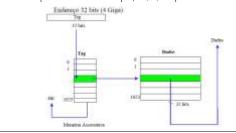

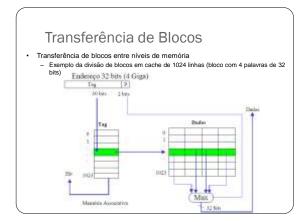

- Divisão de bits no registrador de endereçamento

- Exemplo de uma cache com 1024 posições (2<sup>10</sup>) com palavra de 32 bits

#### Acessando a Cache

- Passos para um acesso

- Extrair a Tag do endereço requisitado

- 2. Se Tag está na memória associativa

(Hit) Acessar memória cache com <mark>índice</mark> fornecido pela memória associativa Ir para 7

Senão

Acusar miss

3. Se não existir posição livre na cache

Escolher endereço para substituir de acordo com política estabelecida (e.g. LRU)

- 4. Buscar dado no nível inferior

- 5. Colocar na posição livre ou escolhida da memória cache

- 6. Cadastrar posição na memória associativa para pesquisas futuras

- 7. Efetuar leitura

- 8. Fim

###

#### Exercício

- 1. Considerando espaço de endereçamento de 256 Mega palavras. Como ficaria a divisão de bits do endereço para uma cache de 2048 posições e que trabalhe com blocos de 8

- 2. Quanto tem efetivamente de dados nessa cache?

- 3. Oual o tamanho da memória associativa?

### Resposta do Exercício

1. Considerando espaço de endereçamento de 256 Mega palavras. Como ficaria a divisão de bits do endereço para uma cache de 2048 posições e que trabalhe com blocos de 8

> Endereço de 28 bits (256 Mega) 3 (Palavra) 25 (Tag)

2. Quanto tem efetivamente de dados nessa cache?

100% (não considerando bit de validade)

3. Qual o tamanho da memória associativa?

Tamanho = 2048 \* 25 (tag)

= 51200 bits / 8

= 6400 bytes / 1024

= 6,25 Kbytes

#### Exercício

(POSCOMP 2005 - 23) Das afirmações a seguir, sobre memória cache, quais são verdadeiras?

- Numa estrutura totalmente associativa, um bloco de memória pode ser mapeado em qualquer slot do cache.

- . O campo tag do endereço é usado para identificar um bloco válido no cache, junto com o campo de índice.

- III. Um cache de nível 2 serve para reduzir a penalidade no caso de falta no nível 1.

- IV. O esquema de substituição LRU é o mais usado para a estrutura de mapeamento direto.

- Somente as afirmações (I), (III) e (IV). Somente as afirmações (II), (III) e (IV).

- Somente as afirmações (I) e (II).

- Somente as afirmações (II) e (III).

- Somente as afirmações (I), (II) e (III)

### Resposta do Exercício

(POSCOMP 2005 - 23) Das afirmações a seguir, sobre memória cache, quais são verdadeiras?

- Numa estrutura totalmente associativa, um bloco de memória pode ser mapeado em qualquer slot do cache.

- O campo tag do endereço é usado para identificar um bloco válido no cache, junto com o

- III. Um cache de nível 2 serve para reduzir a penalidade no caso de falta no nível 1.

- O esquema de substituição LRU é o mais usado para a estrutura de mapeamento direto.

- Somente as afirmações (I), (III) e (IV). Somente as afirmações (II), (III) e (IV).

- Somente as afirmações (I) e (II).

- Somente as afirmações (I), (II) e (III)

- Somente as afirmações (II) e (III).

# Conclusões e Questões

- · Vantagens do mapeamento associativo

- Melhor distribuição da informação na cache

- Melhor aproveitamento da cache → Praticamente 100% de aproveitamento

- Tags não ocupam espaço da cache (estão na memória associativa)

- Desvantagens

- Memória associativa tem alto custo e tamanho limitado

- Limita número de linhas da cache

- Necessita política de substituição

- Pode ocorrer escolhas inadequadas

- Limite de tamanho da cache devido pesquisa na memória associativa é uma restrição muito forte 🗦 Tendência é aumentar a cache